# CS162 Operating Systems and Systems Programming Lecture 13

# Address Translation (Con't) Caching

March 12<sup>th</sup>, 2019 Prof. John Kubiatowicz http://cs162.eecs.Berkeley.edu

### Recall: Page Table Discussion

- What needs to be switched on a context switch?

Page table pointer and limit

- Analysis

- Pros

- » Simple memory allocation

- » Easy to share

- Con: What if address space is sparse?

- » E.g., on UNIX, code starts at 0, stack starts at (2<sup>31</sup>-1)

- » With 1K pages, need 2 million page table entries!

- Con: What if table really big?

- » Not all pages used all the time ⇒ would be nice to have working set of page table in memory

- How about multi-level paging or combining paging and segmentation?

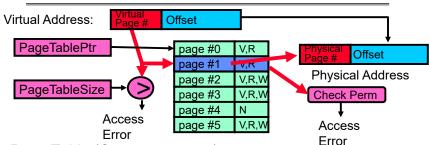

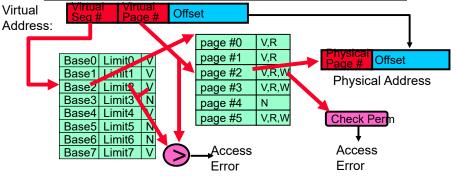

### Recall: Simple Paging

- Page Table (One per process)

- Resides in physical memory

- Contains physical page and permission for each virtual page

» Permissions include: Valid bits, Read, Write, etc

- Virtual address mapping

- Offset from Virtual address copied to Physical Address

» Example: 10 bit offset ⇒ 1024-byte pages

- Virtual page # is all remaining bits

- » Example for 32-bits: 32-10 = 22 bits, i.e. 4 million entries

- » Physical page # copied from table into physical address

- Check Page Table bounds and permissions

3/12/19

3/12/19

Kubiatowicz CS162 ©UCB Spring 2019

Lec 13.2

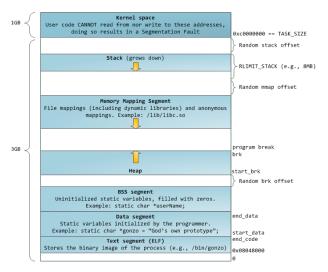

# Recall: Memory Layout for Linux 32-bit

http://static.duartes.org/img/blogPosts/linuxFlexibleAddressSpaceLayout.png

### What is in a Page Table Entry (PTE)?

- What is in a Page Table Entry (or PTE)?

- Pointer to next-level page table or to actual page

- Permission bits: valid, read-only, read-write, write-only

- Example: Intel x86 architecture PTE:

- Address same format previous slide (10, 10, 12-bit offset)

- Intermediate page tables called "Directories"

| Page Frame Number<br>(Physical Page Number) | Free<br>(OS) | 0 | L | D | Α | PCD | PWT | U | w | Р |

|---------------------------------------------|--------------|---|---|---|---|-----|-----|---|---|---|

| 31-12                                       | 11-9         | 8 | 7 | 6 | 5 | 4   | 3   | 2 | 1 | 0 |

- P: Present (same as "valid" bit in other architectures)

- W: Writeable

- U: User accessible

- PWT: Page write transparent: external cache write-through

- PCD: Page cache disabled (page cannot be cached)

- A: Accessed: page has been accessed recently

- D: Dirty (PTE only): page has been modified recently

- L: L=1⇒4MB page (directory only).

Bottom 22 bits of virtual address serve as offset

3/12/19

3/12/19

Kubiatowicz CS162 ©UCB Spring 2019

Lec 13.6

### Examples of how to use a PTE

- How do we use the PTE?

- Invalid PTE can imply different things:

- » Region of address space is actually invalid or

- » Page/directory is just somewhere else than memory

- Validity checked first

- » OS can use other (say) 31 bits for location info

- Usage Example: Demand Paging

- Keep only active pages in memory

- Place others on disk and mark their PTEs invalid

- Usage Example: Copy on Write

- UNIX fork gives copy of parent address space to child

- » Address spaces disconnected after child created

- How to do this cheaply?

- » Make copy of parent's page tables (point at same memory)

- » Mark entries in both sets of page tables as read-only

- » Page fault on write creates two copies

- Usage Example: Zero Fill On Demand

- New data pages must carry no information (say be zeroed)

- Mark PTE's as invalid; page fault on use gets zeroed page

- Often, OS creates zeroed pages in background

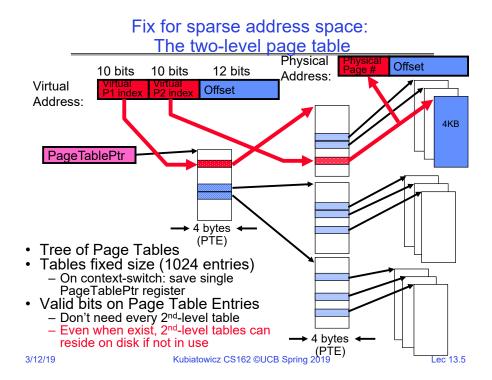

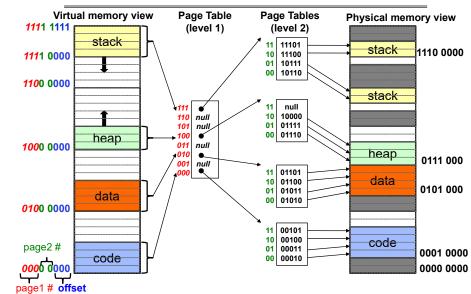

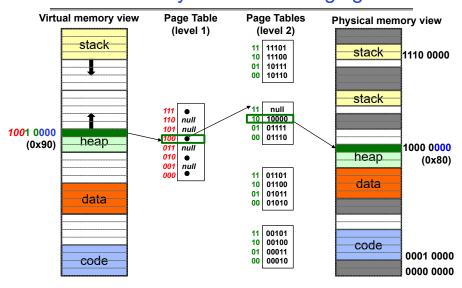

### Summary: Two-Level Paging

### Summary: Two-Level Paging

3/12/19 Kubiatowicz CS162 ©UCB Spring 2019

Lec 13.9

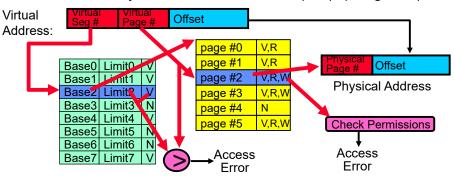

### Multi-level Translation: Segments + Pages

- · What about a tree of tables?

- Lowest level page table ⇒ memory still allocated with bitmap

- Higher levels often segmented

- Could have any number of levels. Example (top segment):

- What must be saved/restored on context switch?

- Contents of top-level segment registers (for this example)

- Pointer to top-level table (page table)

3/12/19

Kubiatowicz CS162 ©UCB Spring 2019

Lec 13.10

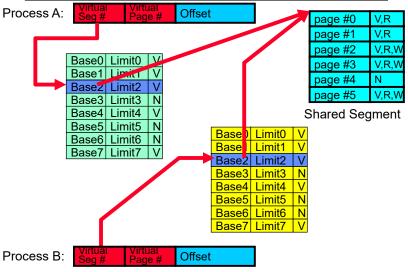

# What about Sharing (Complete Segment)?

# Multi-level Translation Analysis

### • Pros:

- Only need to allocate as many page table entries as we need for application

- » In other wards, sparse address spaces are easy

- Easy memory allocation

- Easy Sharing

- » Share at segment or page level (need additional reference counting)

#### · Cons:

- One pointer per page (typically 4K 16K pages today)

- Page tables need to be contiguous

- » However, previous example keeps tables to exactly one page in size

- -Two (or more, if >2 levels) lookups per reference

- » Seems very expensive!

### Administrivia

- Final Project 1 Report Due today!

- Project 2 Release on Thursday (3/14)

- Happy PI day!

- Midterm 2: Thursday 4/4

- Ok, this is a few weeks and after Spring Break.

- Will definitely include Scheduling material (lecture 10)

- Up to and including some material from lecture 17

- Probably try to have a Midterm review in early part of that week.... Stay tuned

- Note: A double-lock release always bad!

- Solution to (3c) on exam doesn't protect against a double release (i.e. release when lock is free).

- » Enhancement: Crash program (with error) if release on free lock

- » NOT: Fix it up so that a release on free lock ok!

- Why? Because releasing without acquiring means messing up a different thread that has just acquired lock properly!

3/12/19

Kubiatowicz CS162 ©UCB Spring 2019

Lec 13.13

### CS 162 Collaboration Policy

Explaining a concept to someone in another group Discussing algorithms/testing strategies with other groups Helping debug someone else's code (in another group) Searching online for generic algorithms (e.g., hash table)

Sharing code or test cases with another group Copying OR reading another group's code or test cases Copying OR reading online code or test cases from from prior years

We compare all project submissions against prior year submissions and online solutions and will take actions (described on the course overview page) against offenders

3/12/19

3/12/19

Kubiatowicz CS162 ©UCB Spring 2019

Lec 13.14

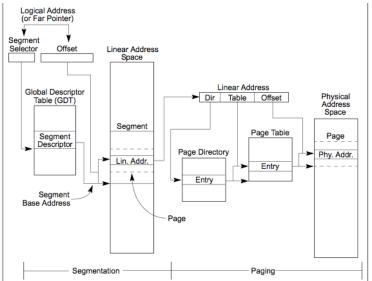

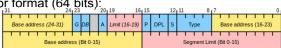

### Making it real: X86 Memory model with segmentation (16/32-bit)

### X86 Segment Descriptors (32-bit Protected Mode)

- Seaments are either implicit in the instruction (say for code segments) or actually part of the instruction

- There are 6 registers: SS, CS, DS, ES, FS, GS

- What is in a segment register?

- A *pointer* to the actual segment description:

Segment selector [13 bits] RPL

G/L selects between GDT and LDT tables (global vs local descriptor

- Two registers: GDTR and LDTR hold pointers to the global and local descriptor tables in memory

- Includes length of table (for < 213) entries

Descriptor format (64 bits):

G: Granularity of segment [Limit Size] (0: 16bit, 1: 4KiB unit)

DB: Default operand size (0: 16bit, 1: 32bit)

A: Freely available for use by software

P: Segment present

DPL: Descriptor Privilege Level

S: System Segment (0: System, 1: code or data)

Type: Code, Data, Segment

### Recall: How are segments used?

- One set of global segments (GDT) for everyone, different set of local segments (LDT) for every process

- In legacy applications (16-bit mode):

- Segments provide protection for different components of user programs

- Separate segments for chunks of code, data, stacks

- Limited to 64K segments

- · Modern use in 32-bit Mode:

- Segments "flattened", i.e. every segment is 4GB in size

- One exception: Use of GS (or FS) as a pointer to "Thread Local Storage" (TLS)

- » A thread can make accesses to TLS like this: mov eax, qs(0x0)

- Modern use in 64-bit ("long") mode

- Most segments (SS, CS, DS, ES) have zero base and no length limits

- Only FS and GS retain their functionality (for use in TLS)

3/12/19

Kubiatowicz CS162 ©UCB Spring 2019

Lec 13.17

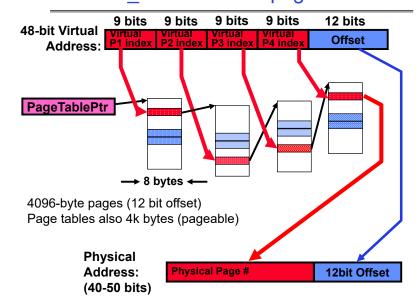

### X86 64: Four-level page table!

Kubiatowicz CS162 ©UCB Spring 2019

Lec 13.18

### IA64: 64bit addresses: Six-level page table?!?

64bit Virtual 7 bits 9 bits 9 bits 9 bits 9 bits 9 bits 9 bits 12 bits

Address: Virtual Virtual Virtual Virtual Virtual Virtual Virtual Virtual P4 index P5 index P6 index Offset

No!

Too slow

Too many almost-empty tables

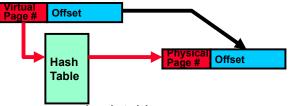

### Inverted Page Table

- With all previous examples ("Forward Page Tables")

- Size of page table is at least as large as amount of virtual memory allocated to processes

- Physical memory may be much less

- » Much of process space may be out on disk or not in use

- Answer: use a hash table

- Called an "Inverted Page Table"

- Size is independent of virtual address space

- Directly related to amount of physical memory

- Very attractive option for 64-bit address spaces

» PowerPC, UltraSPARC, IA64

- Cons:

- Complexity of managing hash chains: Often in hardware!

- Poor cache locality of page table Spring 2019

### Address Translation Comparison

|                            | Advantages                                                      | Disadvantages                                                 |  |  |  |

|----------------------------|-----------------------------------------------------------------|---------------------------------------------------------------|--|--|--|

| Simple<br>Segmentation     | Fast context switching:<br>Segment mapping<br>maintained by CPU | External fragmentation                                        |  |  |  |

| Paging (single-level page) | No external fragmentation, fast easy allocation                 | Large table size ~ virtual memory Internal fragmentation      |  |  |  |

| Paged segmentation         | Table size ~ # of pages in virtual memory, fast easy allocation | Multiple memory references per page access                    |  |  |  |

| Two-level pages            |                                                                 |                                                               |  |  |  |

| Inverted Table             | Table size ~ # of pages in physical memory                      | Hash function more complex<br>No cache locality of page table |  |  |  |

3/12/19 Kubiatowicz CS162 ©UCB Spring 2019 Lec 13.21

### How is the Translation Accomplished?

- What, exactly happens inside MMU?

- One possibility: Hardware Tree Traversal

- For each virtual address traverses page table in hardware

- Generates a "Page Fault" if it encounters invalid PTE

- » Fault handler will decide what to do

- » More on this next lecture

- Pros: Relatively fast (but still many memory accesses!)

- Cons: Inflexible, Complex hardware

- Another possibility: Software Tree Traversal

- Each traversal done in software (often invoked by "TLB Fault" more on this later)

- Software may generate "Page Fault" later if PTE invalid

- Pros: Very flexible

- Cons: Every translation must invoke Fault!

- In fact, need way to cache translations for either case!

3/12/19

3/12/19

Kubiatowicz CS162 ©UCB Spring 2019

Lec 13.22

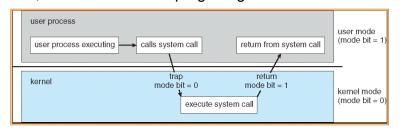

### Recall: Dual-Mode Operation

- Can a process modify its own translation tables?

- NO!

- If it could, could get access to all of physical memory

- Has to be restricted somehow

- To Assist with Protection, Hardware provides at least two modes (Dual-Mode Operation):

- "Kernel" mode (or "supervisor" or "protected")

- "User" mode (Normal program mode)

- Mode set with bit(s) in control register only accessible in Kernel mode

- Kernel can easily switch to user mode; User program must invoke an exception of some sort to get back to kernel mode (more in moment)

- Note that x86 model actually has more modes:

- Traditionally, four "rings" representing priority; most OSes use only two:

- » Ring  $0 \Rightarrow$  Kernel mode, Ring  $3 \Rightarrow$  User mode

- Newer processors have additional mode for hypervisor ("Ring -1")

- Certain operations restricted to Kernel mode:

- Including modifying the page table (CR3 in x86), and GDT/LDT

- Have to transition into Kernel mode before you can change them Kubiatowicz CS162 ©UCB Spring 2019 Lec 13.23

# Recall: User→Kernel (System Call)

- Can't let inmate (user) get out of padded cell on own

- Would defeat purpose of protection!

- -So, how does the user program get back into kernel?

- System call: Voluntary procedure call into kernel

- Hardware for controlled User→Kernel transition

- Can any kernel routine be called? » No! Only specific ones.

- System call ID encoded into system call instruction

- » Index forces well-defined interface with kernel

Kubiatowicz CS162 ©UCB Spring 2019

### Recall: System Call Continued

- · What are some system calls?

- I/O: open, close, read, write, Iseek

- Files: delete, mkdir, rmdir, truncate, chown, chgrp, ...

- Process: fork, exit, wait (like join)

- Network: socket create, set options

- What happens at beginning of system call?

- -On entry to kernel, sets system to kernel mode

- Handler address fetched from table/Handler started

- System call argument passing:

- In registers (not very much can be passed)

- Write into user memory, kernel copies into kernel mem

- » User addresses must be translated!

- » Kernel has different view of memory than user

- Every argument must be explicitly checked!

3/12/19

Kubiatowicz CS162 ©UCB Spring 2019

Lec 13.25

# Recall: User→Kernel (Exceptions: Traps & Interrupts)

- A system call instruction causes a synchronous exception (or "trap")

- In fact, often called a software "trap" instruction

- Other sources of Synchronous Exceptions ("Trap"):

- Divide by zero, Illegal instruction, Bus error (bad address, e.g. unaligned access)

- Segmentation Fault (address out of range)

- Page Fault (for illusion of infinite-sized memory)

- Interrupts are Asynchronous Exceptions:

- Examples: timer, disk ready, network, etc....

- Interrupts can be disabled, traps cannot!

- · On system call, exception, or interrupt:

- Hardware enters kernel mode with interrupts disabled

- Saves PC, then jumps to appropriate handler in kernel

- Some processors (e.g. x86) also save registers, changes stack

- Handler does any required state preservation not done by CPU:

- Might save registers, other CPU state, and switches to kernel stack

3/12/19

Kubiatowicz CS162 ©UCB Spring 2019

Lec 13.26

### How to get from Kernel→User

- What does the kernel do to create a new user process?

- Allocate and initialize address-space control block

- Read program off disk and store in memory

- Allocate and initialize translation table

- » Point at code in memory so program can execute

- » Possibly point at statically initialized data

- Run Program:

- » Set machine registers

- » Set hardware pointer to translation table (e.g. CR3 in x86)

- » Set processor status word for user mode

- » Jump to start of program

- · How does kernel switch between processes?

- Same saving/restoring of registers as before

- Save/restore PSL (hardware pointer to translation table)

# Closing thought: Protection without Hardware

- Does protection require hardware support for translation and dualmode behavior?

- No: Normally use hardware, but anything you can do in hardware can also be done in software (possibly expensive)

- · Protection via Strong Typing

- Restrict programming language so that you can't express program that would trash another program

- Loader needs to make sure that program produced by valid compiler or all bets are off

- Example languages: LISP, Ada, Modula-3 and Java

- Protection via software fault isolation:

- Language independent approach: have compiler generate object code that provably can't step out of bounds

- » Compiler puts in checks for every "dangerous" operation (loads, stores, etc). Again, need special loader.

- » Alternative, compiler generates "proof" that code cannot do certain things (Proof Carrying Code)

- Or: use virtual machine to guarantee safe behavior (loads and stores recompiled on fly to check bounds)

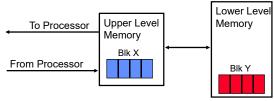

### **Caching Concept**

- Cache: a repository for copies that can be accessed more quickly than the original

- Make frequent case fast and infrequent case less dominant

- Caching underlies many techniques used today to make computers fast

- Can cache: memory locations, address translations, pages, file blocks, file names, network routes, etc...

- · Only good if:

- Frequent case frequent enough and

- Infrequent case not too expensive

- Important measure: Average Access time =

(Hit Rate x Hit Time) + (Miss Rate x Miss Time)

3/12/19

Kubiatowicz CS162 ©UCB Spring 2019

Lec 13.29

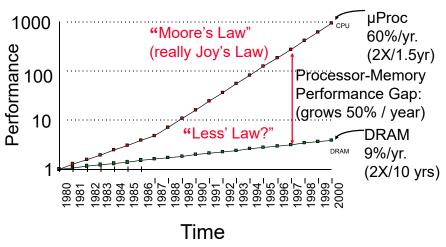

### Why Bother with Caching?

### Processor-DRAM Memory Gap (latency)

3/12/19 Kubiatowicz CS162 ©UCB Spring 2019

Lec 13.30

### Another Major Reason to Deal with Caching

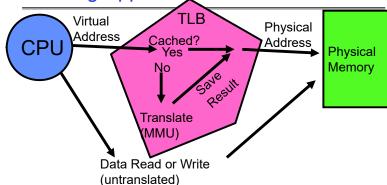

- · Cannot afford to translate on every access

- At least three DRAM accesses per actual DRAM access

- Or: perhaps I/O if page table partially on disk!

- Even worse: What if we are using caching to make memory access faster than DRAM access?

- · Solution? Cache translations!

- Translation Cache: TLB ("Translation Lookaside Buffer")

# Why Does Caching Help? Locality!

- Temporal Locality (Locality in Time):

- Keep recently accessed data items closer to processor

- Spatial Locality (Locality in Space):

- Move contiguous blocks to the upper levels

3/12/19 Kubiatowicz CS162 ©UCB Spring 2019

Lec 13.32

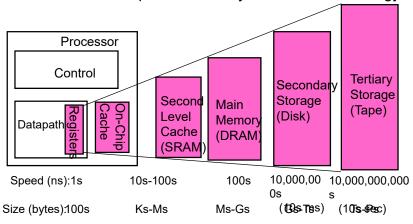

### Memory Hierarchy of a Modern Computer System

- Take advantage of the principle of locality to:

- Present as much memory as in the cheapest technology

- Provide access at speed offered by the fastest technology

3/12/19 Kubiatowicz CS162 ©UCB Spring 2019

Lec 13.33

### A Summary on Sources of Cache Misses

- Compulsory (cold start or process migration, first reference): first access to a block

- "Cold" fact of life: not a whole lot you can do about it

- Note: If you are going to run "billions" of instruction, Compulsory Misses are insignificant

- Capacity

- Cache cannot contain all blocks access by the program

- Solution: increase cache size

- Conflict (collision):

- Multiple memory locations mapped to the same cache location

- Solution 1: increase cache size

- Solution 2: increase associativity

- Coherence (Invalidation): other process (e.g., I/O) updates memory

3/12/19

3/12/19

Kubiatowicz CS162 ©UCB Spring 2019

Lec 13.34

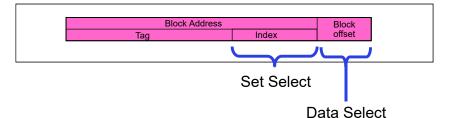

### How is a Block found in a Cache?

- Block is minimum quantum of caching

- Data select field used to select data within block

- Many caching applications don't have data select field

- Index Used to Lookup Candidates in Cache

- Index identifies the set

- Tag used to identify actual copy

- If no candidates match, then declare cache miss

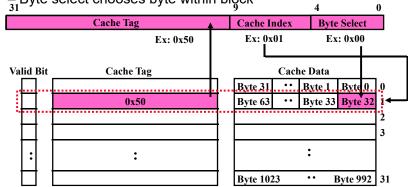

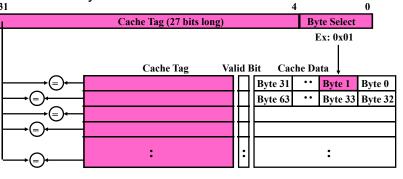

# Review: Direct Mapped Cache

- Direct Mapped 2<sup>N</sup> byte cache:

- The uppermost (32 N) bits are always the Cache Tag

- The lowest M bits are the Byte Select (Block Size = 2<sup>M</sup>)

- Example: 1 KB Direct Mapped Cache with 32 B Blocks

- Index chooses potential block

- Tag checked to verify block

Byte select chooses byte within block

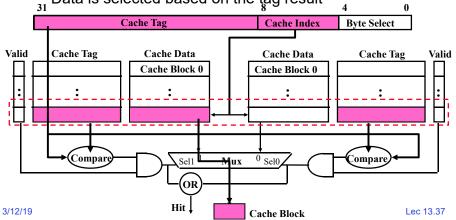

### Review: Set Associative Cache

- N-way set associative: N entries per Cache Index

- N direct mapped caches operates in parallel

- Example: Two-way set associative cache

- Cache Index selects a "set" from the cache

- Two tags in the set are compared to input in parallel

- \_\_ Data is selected based on the tag result

### Review: Fully Associative Cache

- Fully Associative: Every block can hold any line

- Address does not include a cache index

- Compare Cache Tags of all Cache Entries in Parallel

- Example: Block Size=32B blocks

- -We need N 27-bit comparators

- Still have byte select to choose from within block

3/12/19 Kubiatowicz CS162 ©UCB Spring 2019

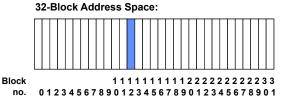

### Where does a Block Get Placed in a Cache?

• Example: Block 12 placed in 8 block cache

#### Direct mapped: block 12 can go only into block 4

#### Set associative: block 12 can go anywhere in set 0

Block 0 1 2 3 4 5 6 7 no. Set Set Set Set Set

0 1 2 3

(12 mod 4)

# Fully associative: block 12 can go

Block 0 1 2 3 4 5 6 7 no.

anywhere

### Which block should be replaced on a miss?

- · Easy for Direct Mapped: Only one possibility

- Set Associative or Fully Associative:

- Random

3/12/19

- LRU (Least Recently Used)

- · Miss rates for a workload:

|        | 2-    | way   | 4-way |       | 8-way |        |  |  |

|--------|-------|-------|-------|-------|-------|--------|--|--|

| Size   |       |       |       |       |       | Random |  |  |

| 16 KB  | 5.2%  | 5.7%  | 4.7%  | 5.3%  | 4.4%  | 5.0%   |  |  |

| 64 KB  | 1.9%  | 2.0%  | 1.5%  | 1.7%  | 1.4%  | 1.5%   |  |  |

| 256 KB | 1.15% | 1.17% | 1.13% | 1.13% | 1.12% | 1.12%  |  |  |

Lec 13.38

### Review: What happens on a write?

- Write through: The information is written to both the block in the cache and to the block in the lower-level memory

- Write back: The information is written only to the block in the cache

- Modified cache block is written to main memory only when it is replaced

- Question is block clean or dirty?

- · Pros and Cons of each?

- -WT:

- » PRO: read misses cannot result in writes

- » CON: Processor held up on writes unless writes buffered

- -WB:

- » PRO: repeated writes not sent to DRAM processor not held up on writes

- » CON: More complex Read miss may require writeback of dirty data

3/12/19 Kubiatowicz CS162 ©UCB Spring 2019

Lec 13.41

### Caching Applied to Address Translation

- Question is one of page locality: does it exist?

- Instruction accesses spend a lot of time on the same page (since accesses sequential)

- Stack accesses have definite locality of reference

- Data accesses have less page locality, but still some...

- Can we have a TLB hierarchy?

- Sure: multiple levels at different sizes/speeds

3/12/19

Kubiatowicz CS162 ©UCB Spring 2019

Lec 13.42

### What Actually Happens on a TLB Miss? (1/2)

- Hardware traversed page tables:

- On TLB miss, hardware in MMU looks at current page table to fill TLB (may walk multiple levels)

- » If PTE valid, hardware fills TLB and processor never knows

- » If PTE marked as invalid, causes Page Fault, after which kernel decides what to do afterwards

- Software traversed Page tables (like MIPS):

- On TLB miss, processor receives TLB fault

- Kernel traverses page table to find PTE

- » If PTE valid, fills TLB and returns from fault

- » If PTE marked as invalid, internally calls Page Fault handler

- Most chip sets provide hardware traversal

- Modern operating systems tend to have more TLB faults since they use translation for many things

- Examples:

- » shared segments

- » user-level portions of an operating system

### What happens on a Context Switch?

- Need to do something, since TLBs map virtual addresses to physical addresses

- Address Space just changed, so TLB entries no longer valid!

- Options?

- Invalidate TLB: simple but might be expensive

- » What if switching frequently between processes?

- Include ProcessID in TLB

- » This is an architectural solution: needs hardware

- What if translation tables change?

- For example, to move page from memory to disk or vice versa...

- Must invalidate TLB entry!

- » Otherwise, might think that page is still in memory!

### Summary (1/2)

- Page Tables

- Memory divided into fixed-sized chunks of memory

- Virtual page number from virtual address mapped through page table to physical page number

- Offset of virtual address same as physical address

- Large page tables can be placed into virtual memory

- Multi-Level Tables

- Virtual address mapped to series of tables

- Permit sparse population of address space

- Inverted Page Table

- Use of hash-table to hold translation entries

- Size of page table ~ size of physical memory rather than size of virtual memory

Summary (2/2)

- The Principle of Locality:

- Program likely to access a relatively small portion of the address space at any instant of time.

- » Temporal Locality: Locality in Time

- » Spatial Locality: Locality in Space

- Three (+1) Major Categories of Cache Misses:

- Compulsory Misses: sad facts of life. Example: cold start misses.

- Conflict Misses: increase cache size and/or associativity

- Capacity Misses: increase cache size

- Coherence Misses: Caused by external processors or I/O devices

Kubiatowicz CS162 ©UCB Spring 2019

· Cache Organizations:

3/12/19

- Direct Mapped: single block per set

- Set associative: more than one block per set

- Fully associative: all entries equivalent

3/12/19 Kubiato

Kubiatowicz CS162 ©UCB Spring 2019

Lec 13.45

Lec 13.46