### **Vector Microprocessors**

by

Krste Asanović

B.A. (University of Cambridge) 1987

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

**Computer Science**

in the

GRADUATE DIVISION of the UNIVERSITY of CALIFORNIA, BERKELEY

Committee in charge:

Professor John Wawrzynek, Chair Professor David A. Patterson Professor David Wessel

Spring 1998

The dissertation of Krste Asanović is approved:

Chair Date

Date

Date

University of California, Berkeley

Spring 1998

### Vector Microprocessors

Copyright 1998 by Krste Asanović

### Abstract

Vector Microprocessors

by

Krste Asanović Doctor of Philosophy in Computer Science University of California, Berkeley Professor John Wawrzynek, Chair

Most previous research into vector architectures has concentrated on supercomputing applications and small enhancements to existing vector supercomputer implementations. This thesis expands the body of vector research by examining designs appropriate for single-chip full-custom *vector microprocessor* implementations targeting a much broader range of applications.

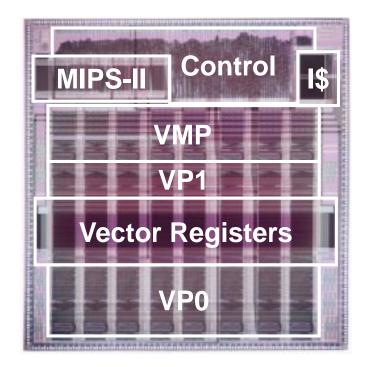

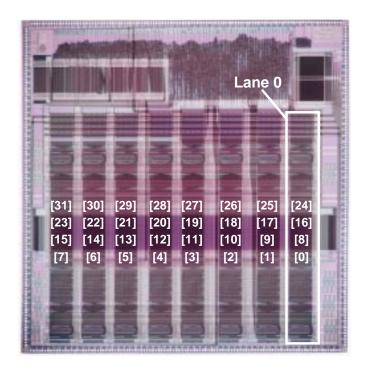

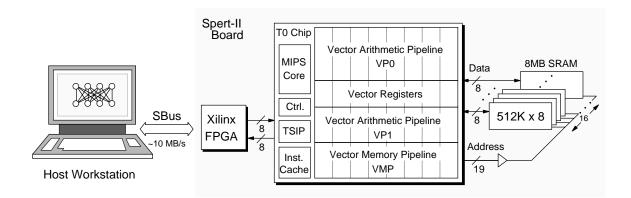

I present the design, implementation, and evaluation of T0 (Torrent-0): the first single-chip vector microprocessor. T0 is a compact but highly parallel processor that can sustain over 24 operations per cycle while issuing only a single 32-bit instruction per cycle. T0 demonstrates that vector architectures are well suited to full-custom VLSI implementation and that they perform well on many multimedia and human-machine interface tasks.

The remainder of the thesis contains proposals for future vector microprocessor designs. I show that the most area-efficient vector register file designs have several banks with several ports, rather than many banks with few ports as used by traditional vector supercomputers, or one bank with many ports as used by superscalar microprocessors. To extend the range of vector processing, I propose a vector flag processing model which enables speculative vectorization of "while" loops. To improve the performance of inexpensive vector memory systems, I introduce *virtual processor caches*, a new form of primary vector cache which can convert some forms of strided and indexed vector accesses into unit-stride bursts.

Professor John Wawrzynek Dissertation Committee Chair

# Contents

| List of Figures |                |                                                                 | ix |  |  |

|-----------------|----------------|-----------------------------------------------------------------|----|--|--|

| Li              | List of Tables |                                                                 |    |  |  |

| 1               | Intr           | oduction                                                        | 1  |  |  |

| 2               | Bacl           | kground and Motivation                                          | 5  |  |  |

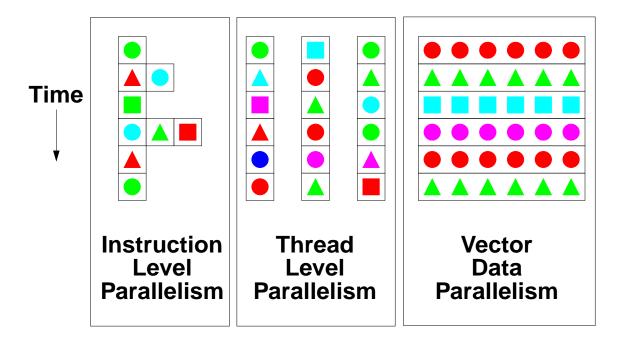

|                 | 2.1            | Alternative Forms of Machine Parallelism                        | 6  |  |  |

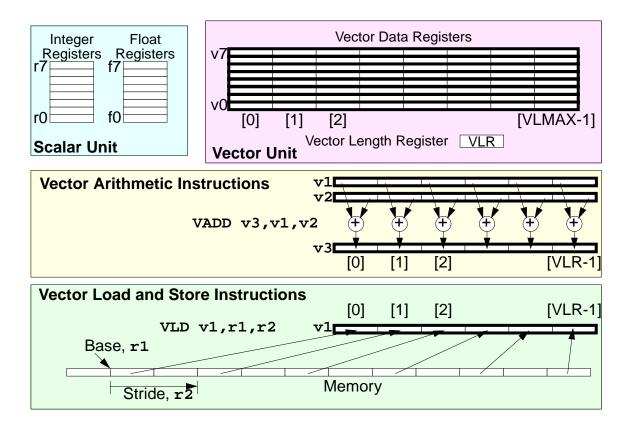

|                 | 2.2            | Vector Processing                                               | 8  |  |  |

|                 |                | 2.2.1 Vector Memory-Memory versus Vector Register Architectures | 8  |  |  |

|                 |                | 2.2.2 Vector Register ISA                                       | 9  |  |  |

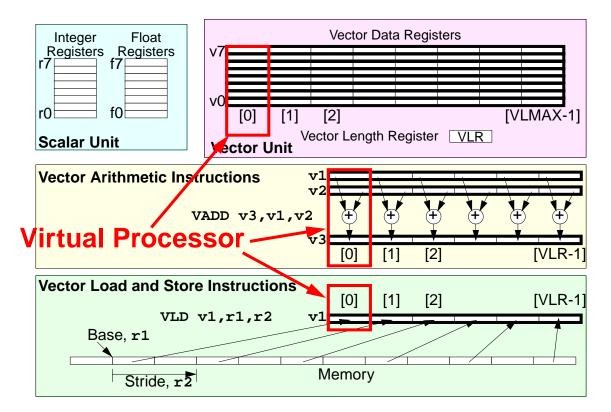

|                 |                | 2.2.3 The Virtual Processor View                                |    |  |  |

|                 |                | 2.2.4 Vector ISA Advantages                                     | 13 |  |  |

|                 | 2.3            | Applications                                                    | 14 |  |  |

|                 |                | 2.3.1 Software Effort                                           | 16 |  |  |

|                 |                | 2.3.2 The Continuing Importance of Assembly Coding              | 16 |  |  |

|                 | 2.4            | Scalar Performance                                              | 17 |  |  |

|                 |                | 2.4.1 Scalar Performance of Vector Supercomputers               | 19 |  |  |

|                 |                | 2.4.2 Scalar versus Vector Performance Tradeoff                 |    |  |  |

|                 | 2.5            | Memory Systems                                                  | 21 |  |  |

|                 |                | 2.5.1 STREAM Benchmark                                          |    |  |  |

|                 |                | 2.5.2 High Performance DRAM Interfaces                          | 24 |  |  |

|                 |                | 2.5.3 IRAM: Processor-Memory Integration                        |    |  |  |

|                 | 2.6            | Energy Efficiency                                               | 25 |  |  |

|                 | 2.7            | Summary                                                         |    |  |  |

|                 |                |                                                                 |    |  |  |

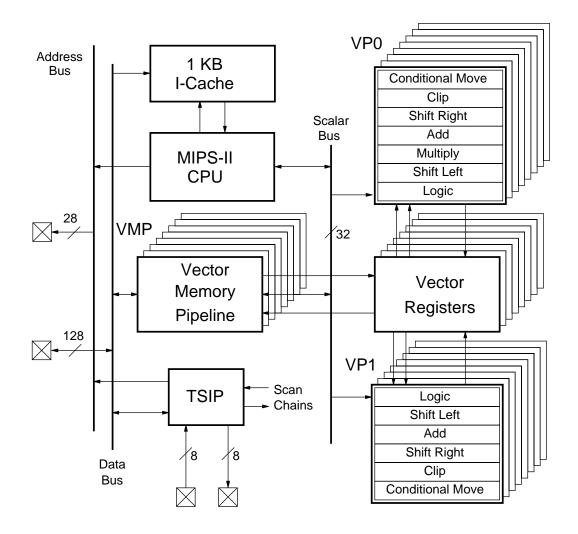

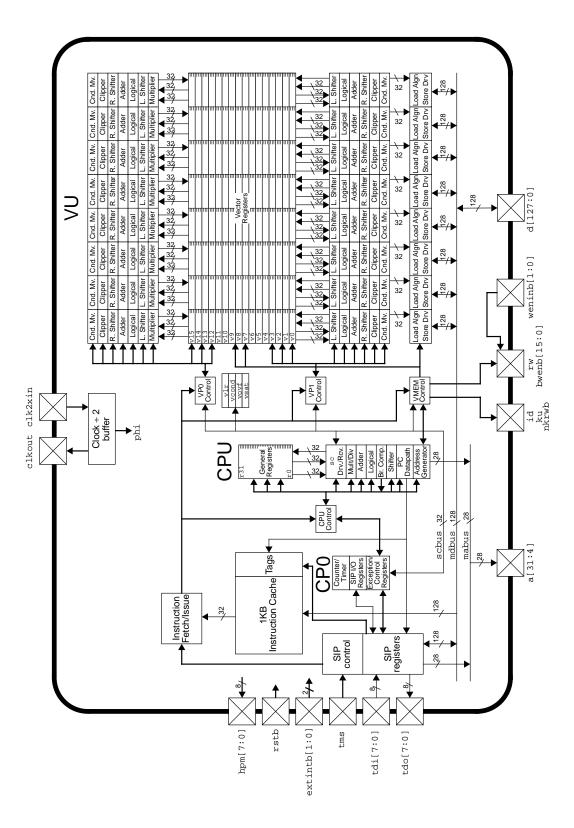

| 3               | Т0:            | A Vector Microprocessor                                         | 29 |  |  |

|                 | 3.1            | Project Background                                              | 29 |  |  |

|                 | 3.2            | Torrent Instruction Set Architecture                            | 31 |  |  |

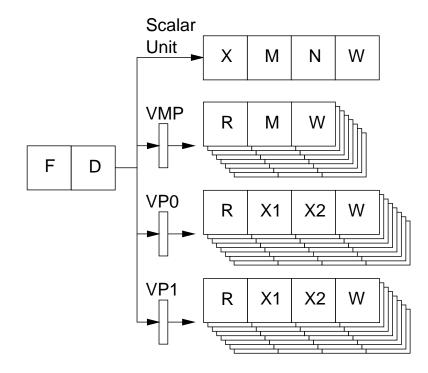

|                 | 3.3            | T0 Microarchitecture                                            | 32 |  |  |

|                 |                | 3.3.1 External Memory                                           | 32 |  |  |

|                 |                | 3.3.2 TSIP                                                      | 34 |  |  |

|                 |                | 3.3.3 Instruction Fetch and Decode                              | 35 |  |  |

|                 |                | 3.3.4 Scalar Unit                                               | 36 |  |  |

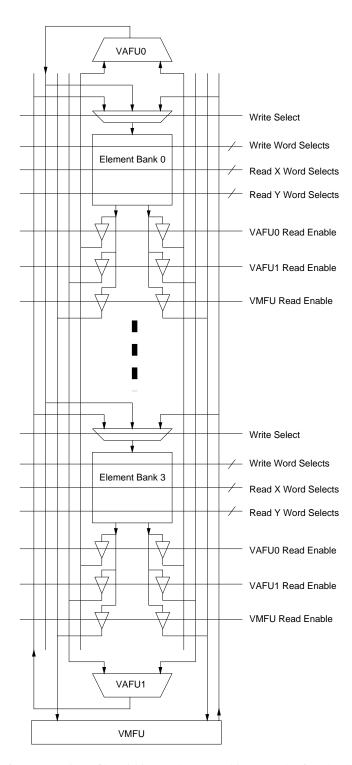

|                 |                | 3.3.5 Vector Register File                                      | 37 |  |  |

|                 |                | 3.3.6 Vector Memory Unit                                        | 37 |  |  |

|                 |                | 3.3.7 Vector Arithmetic Units                                   | 39 |  |  |

|                 |                | 3.3.8 Chaining                                                  | 42 |  |  |

|                 |                | 3.3.9 Exception Handling                                        | 43 |  |  |

|                 |                |                                                                 |    |  |  |

|   |      | 3.3.10 Hardware Performance Monitoring                                                                                           |

|---|------|----------------------------------------------------------------------------------------------------------------------------------|

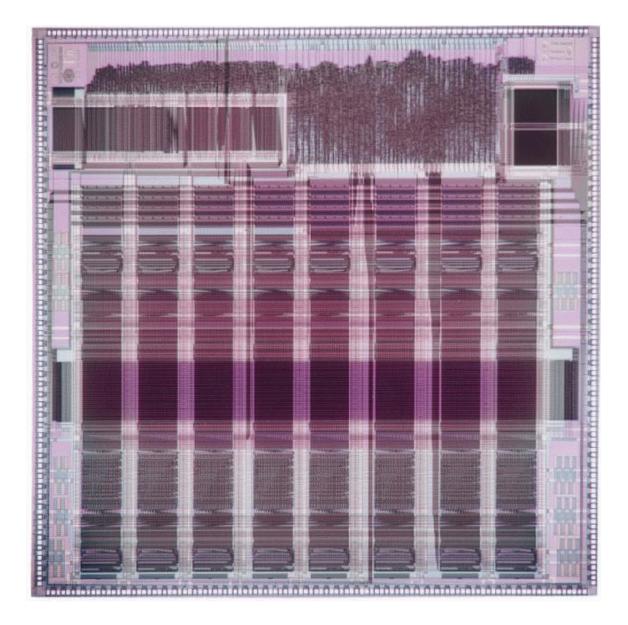

|   | 3.4  | T0 Implementation                                                                                                                |

|   |      | 3.4.1 Process Technology                                                                                                         |

|   |      | 3.4.2 Die Statistics                                                                                                             |

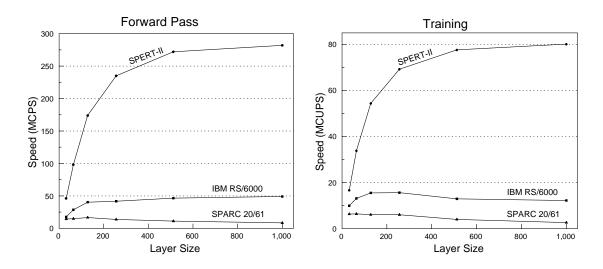

|   |      | 3.4.3 Spert-II System                                                                                                            |

|   | 3.5  | T0 Design Methodology                                                                                                            |

|   | 5.5  | 3.5.1 RTL Design                                                                                                                 |

|   |      | 3.5.2 RTL Verification                                                                                                           |

|   |      | 3.5.3 Circuit and Layout Design                                                                                                  |

|   |      | 3.5.4     Control Logic Design     52                                                                                            |

|   |      | 3.5.5     Timing Analysis     52                                                                                                 |

|   |      | 3.5.6     Timeline and Status     52                                                                                             |

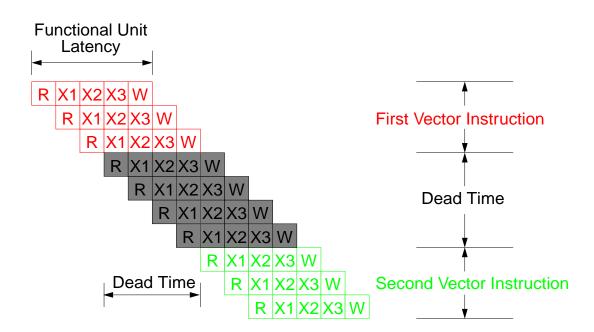

|   | 3.6  | Short Chimes         53                                                                                                          |

|   | 5.0  | Short Chillies                                                                                                                   |

| 4 | Vect | or Instruction Execution 57                                                                                                      |

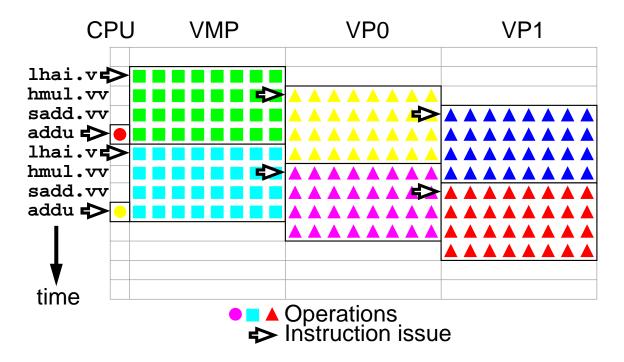

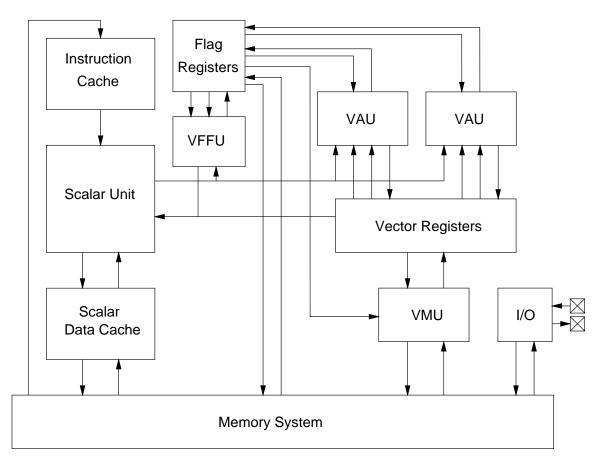

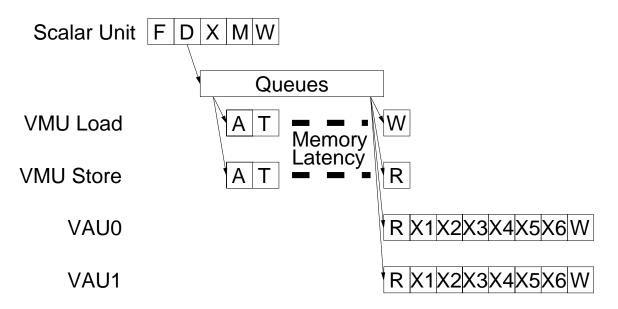

| - | 4.1  | Overall Structure of a Vector Microprocessor   58                                                                                |

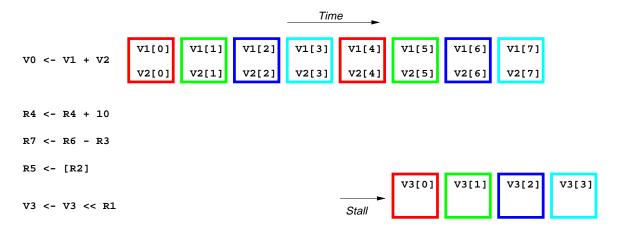

|   | 4.2  | Scalar Instruction Execution in a Vector Processor     59                                                                        |

|   | 4.3  | Vector Instruction Execution 60                                                                                                  |

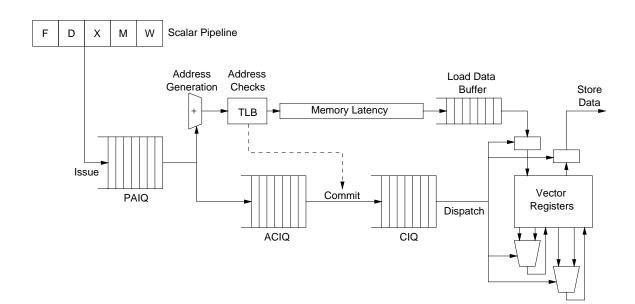

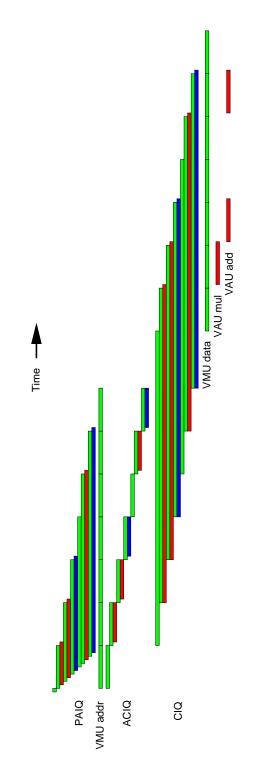

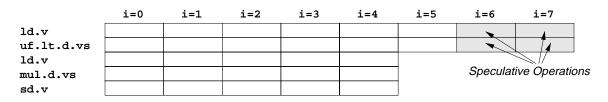

|   | 4.4  | Decoupled Vector Execution 62                                                                                                    |

|   | 4.5  | Out-of-Order Vector Execution     63                                                                                             |

|   | 4.6  | Exception Handling for Vector Machines 64                                                                                        |

|   | 4.0  | 4.6.1 Handling Vector Arithmetic Traps                                                                                           |

|   |      | 4.6.2       Handling Vector Data Page Faults       65                                                                            |

|   | 4.7  | Example Decoupled Vector Pipeline Design                                                                                         |

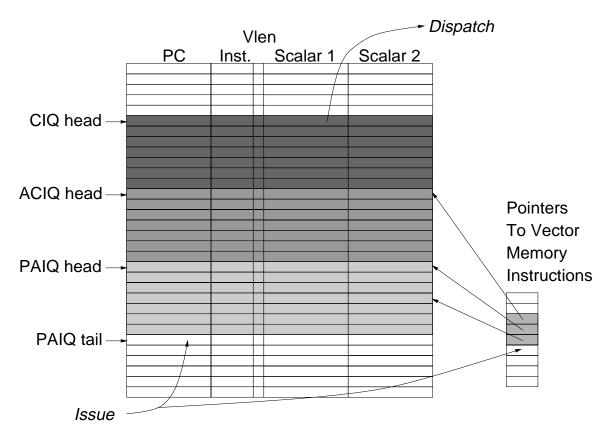

|   | 4.7  | 4.7.1     Instruction Queues     66                                                                                              |

|   |      | 4.7.1         Instruction Queues         60           4.7.2         Execution Example         69                                 |

|   |      | 1                                                                                                                                |

|   | 4.8  |                                                                                                                                  |

|   |      |                                                                                                                                  |

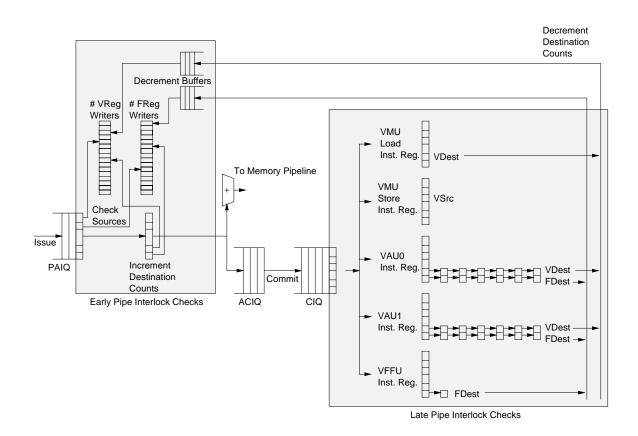

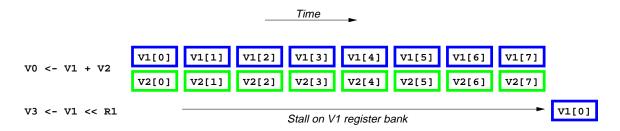

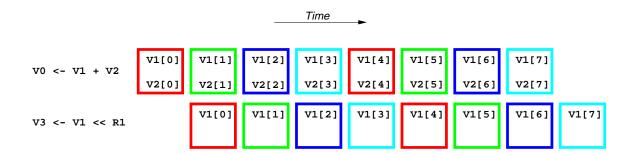

|   | 4.9  | Interlocking and Chaining 76                                                                                                     |

|   |      | 4.9.1 Types of Chaining 76                                                                                                       |

|   |      | 4.9.2 Interlock Control Structure 77                                                                                             |

|   |      | 4.9.3 Early Pipe Interlocks 78                                                                                                   |

|   |      | 4.9.4 Late Pipe Interlocks                                                                                                       |

|   |      | 4.9.5 Chaining Control 80                                                                                                        |

|   |      | 4.9.6 Interlocking and Chaining Summary                                                                                          |

| 5 | Vect | or Register Files 83                                                                                                             |

| • | 5.1  | Vector Register Configuration 83                                                                                                 |

|   | 2.1  | 5.1.1     Vector Register Length     83                                                                                          |

|   |      | 5.1.2     Number of Vector Registers     85                                                                                      |

|   |      | 5.1.2       Reconfigurable Register Files       87                                                                               |

|   |      | 5.1.4       Implementation-dependent Vector Register Length       87                                                             |

|   |      | 5.1.4     Implementation-dependent vector Register Length     87       5.1.5     Context-Switch Overhead     90                  |

|   |      | 5.1.6 Vector Register File Configuration for a Vector Microprocessor                                                             |

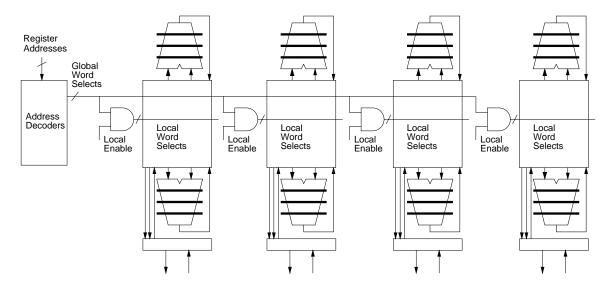

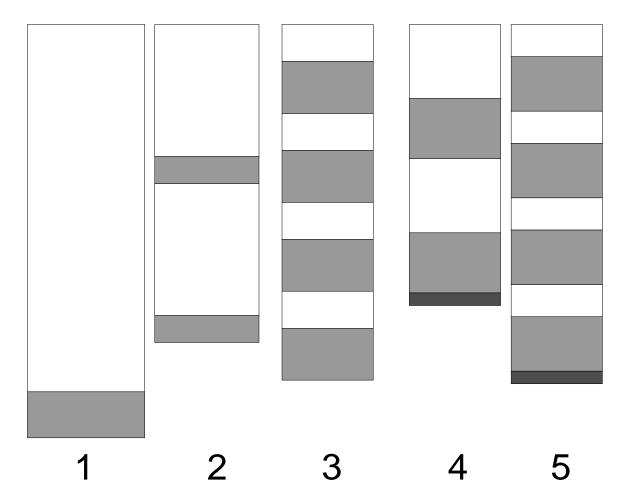

|   | 5.2  | Vector Register File Implementation 91                                                                                           |

|   | 5.2  | 5.2.1       Register-Partitioned versus Element-Partitioned Banks       93                                                       |

|   |      | 5.2.1       Register-Partitioned Versus Element-Partitioned Banks       95         5.2.2       Wider Element Bank Ports       97 |

|   |      |                                                                                                                                  |

|   |      | E I                                                                                                                              |

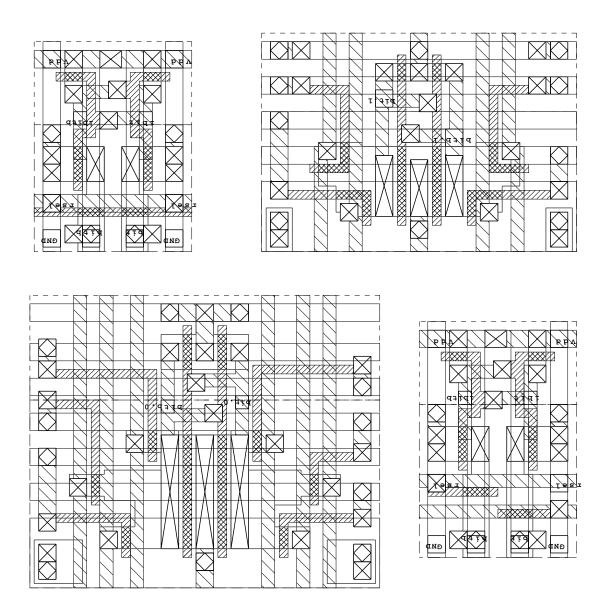

|   |      | 5.2.4 VLSI Implementation of Vector Register Files                                                                               |

v

| 6 | Vect    | or Flag Processing 10                                                                                 | 7 |

|---|---------|-------------------------------------------------------------------------------------------------------|---|

|   | 6.1     | Forms of Vector Conditional Execution 10                                                              |   |

|   | 6.2     | Vector Flag Register Organization 11                                                                  |   |

|   | 6.3     | Flag Combining Operations                                                                             | 1 |

|   | 6.4     | Masked Flag Generation 11                                                                             |   |

|   | 6.5     | Flag Load and Store                                                                                   | 3 |

|   | 6.6     | Flag to Scalar Unit Communication   11                                                                |   |

|   | 6.7     | Speculative Vector Execution 11                                                                       |   |

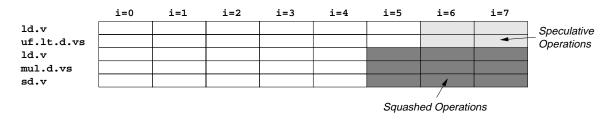

|   | 0.7     | 6.7.1 Speculative Overshoot                                                                           |   |

|   | 6.8     | Flag Priority Instructions   12                                                                       |   |

|   | 6.9     | Density-Time Implementations of Masked Vector Instructions                                            | - |

|   |         | Flag Latency versus Energy Savings   12                                                               |   |

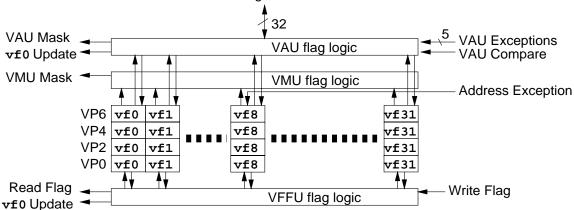

|   |         | Vector Flag Implementation                                                                            |   |

|   | 0.11    |                                                                                                       | 5 |

| 7 | Vect    | or Arithmetic Units 12                                                                                | 9 |

|   | 7.1     | Vector Arithmetic Pipelines                                                                           | 9 |

|   | 7.2     | Vector IEEE Floating-Point Support                                                                    |   |

|   | <i></i> | 7.2.1   Denormalized Arithmetic   13                                                                  |   |

|   |         | 7.2.2 User Floating-Point Trap Handlers                                                               |   |

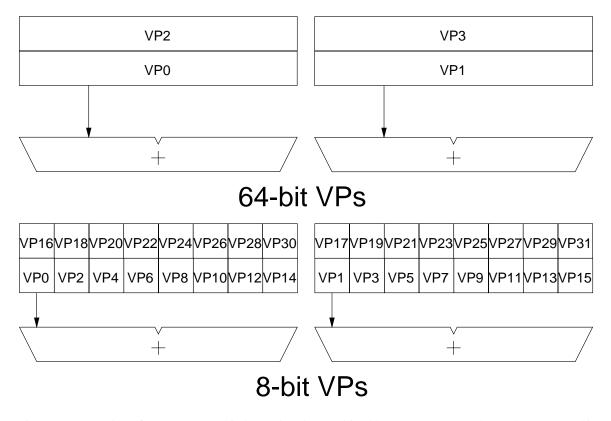

|   | 7.3     | Variable Width Virtual Processors                                                                     |   |

|   | 1.5     | 7.3.1         Setting VP Width         13                                                             |   |

|   |         | 7.3.1       Setting VF within       13         7.3.2       Narrow VPs and Address Generators       13 |   |

|   |         | 7.3.2       Flags and Variable-Width VPs       13                                                     |   |

|   | 7.4     |                                                                                                       |   |

|   | 7.4     | Comparison with Multimedia Extensions                                                                 | / |

| 8 | Vect    | or Memory System 13                                                                                   | 9 |

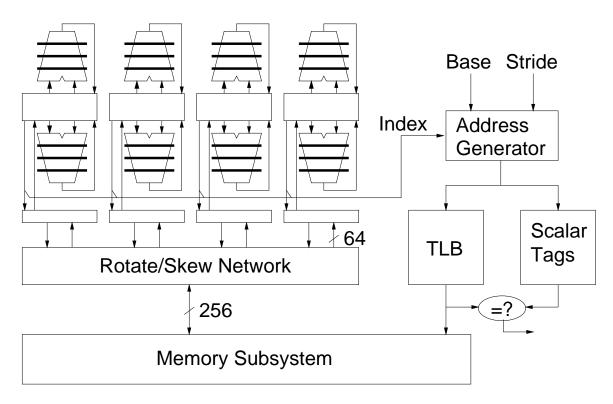

|   | 8.1     | Address Bandwidth                                                                                     | 0 |

|   | 8.2     | High-Level Vector Memory Access Patterns                                                              | 3 |

|   |         | 8.2.1 1D Strided Vectors                                                                              | 4 |

|   |         | 8.2.2 Permutations                                                                                    |   |

|   |         | 8.2.3 Lookup Tables                                                                                   | 4 |

|   |         | 8.2.4 Neighbor Accesses                                                                               | - |

|   |         | 8.2.5 Rakes                                                                                           | - |

|   |         | 8.2.6 Multi-Column Accesses                                                                           | - |

|   | 8.3     | Vector Memory Consistency Models                                                                      |   |

|   | 0.5     | 8.3.1 Inter-Processor Consistency 14                                                                  |   |

|   |         | 8.3.2       Inter-Instruction Consistency       14                                                    |   |

|   |         | 8.3.3       Intra-Instruction Consistency       15                                                    |   |

|   | 8.4     | Vector Memory Unit Implementation 15                                                                  |   |

|   | 0.4     | 8.4.1       Unit-Stride Accesses       15                                                             |   |

|   |         | 8.4.1       Onte-Stride Accesses       15         8.4.2       Strided and Indexed Accesses       15   |   |

|   |         |                                                                                                       |   |

|   | 05      |                                                                                                       |   |

|   | 8.5     | Memory Storage Technologies                                                                           |   |

|   |         | 8.5.1 On-chip SRAM                                                                                    |   |

|   |         | 8.5.2 Off-chip SRAM                                                                                   | - |

|   |         | 8.5.3 Off-chip DRAM                                                                                   | - |

|   | _       | 8.5.4 On-chip DRAM: IRAM                                                                              |   |

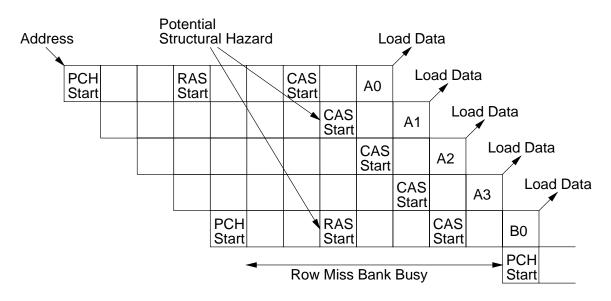

|   | 8.6     | Driving DRAM in a Vector Memory System                                                                |   |

|   |         | 8.6.1 DRAM Control Pipeline                                                                           |   |

|   | 8.7     | Vector Caches                                                                                         |   |

|   |         | 8.7.1 Using Scalar Secondary Cache to Cache Vector Data                                               | 0 |

|   |         | 8.7.2 Scalar-Vector Coherence                                                                         | 0 |

|    |                                                  | 8.7.3                                                                                                                                                                                                                               | Non-blocking Secondary Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50                                                                                          |

|----|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

|    |                                                  | 8.7.4                                                                                                                                                                                                                               | Transient Vector Caches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51                                                                                          |

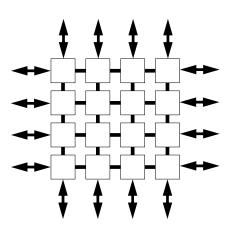

|    | 8.8                                              | Multip                                                                                                                                                                                                                              | ocessor Vector Machines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51                                                                                          |

| 9  | <b>X</b> 7:4-                                    | - al Dua a                                                                                                                                                                                                                          | essor Caches 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                             |

| 9  | <b>viru</b><br>9.1                               |                                                                                                                                                                                                                                     | ce Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |

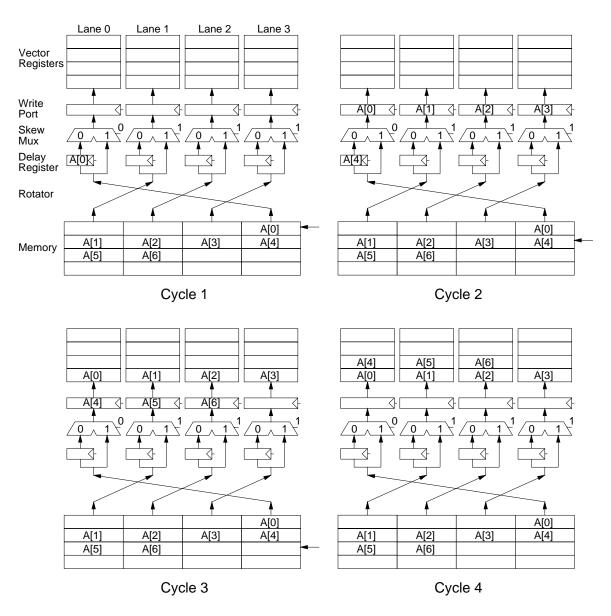

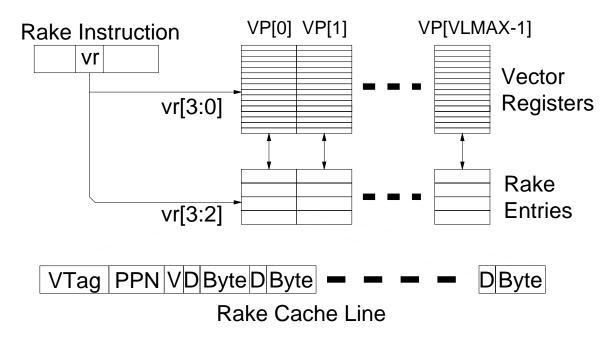

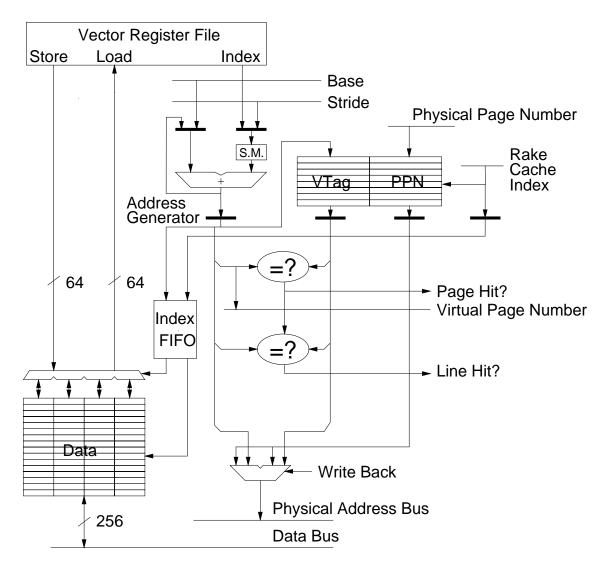

|    | 9.1                                              | 9.1.1                                                                                                                                                                                                                               | Rake Cache Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                             |

|    |                                                  | 9.1.1                                                                                                                                                                                                                               | Rake Cache Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                             |

|    |                                                  | 9.1.2                                                                                                                                                                                                                               | Rake Cache Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                             |

|    |                                                  | 9.1.3<br>9.1.4                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 70                                                                                          |

|    |                                                  | 9.1.4<br>9.1.5                                                                                                                                                                                                                      | Rake Cache Coherency and Consistency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                             |

|    |                                                  | 9.1.5<br>9.1.6                                                                                                                                                                                                                      | Rake Cache Performance   17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                             |

|    |                                                  | 9.1.0<br>9.1.7                                                                                                                                                                                                                      | Rake Cache Write Buffers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |

|    |                                                  | 9.1.7                                                                                                                                                                                                                               | Rake Cache Read Prefetch Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                             |

|    | 9.2                                              |                                                                                                                                                                                                                                     | togram Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                             |

|    | 9.2                                              | 9.2.1                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                             |

|    |                                                  |                                                                                                                                                                                                                                     | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                             |

|    | 0.2                                              | 9.2.2                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                             |

|    | 9.3                                              |                                                                                                                                                                                                                                     | ed Rake and Histogram Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                             |

|    | 9.4                                              | VP Cac                                                                                                                                                                                                                              | he Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50                                                                                          |

| 10 | Virtı                                            | ial Proc                                                                                                                                                                                                                            | essor Communication 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 33                                                                                          |

|    |                                                  |                                                                                                                                                                                                                                     | ons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33                                                                                          |

|    |                                                  |                                                                                                                                                                                                                                     | ss and Expand                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                             |

|    |                                                  | -                                                                                                                                                                                                                                   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 37                                                                                          |

|    | 10.3                                             |                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 37                                                                                          |

|    |                                                  |                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                             |

|    | A                                                |                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                             |

| 11 |                                                  | lications                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>J</b> 3                                                                                  |

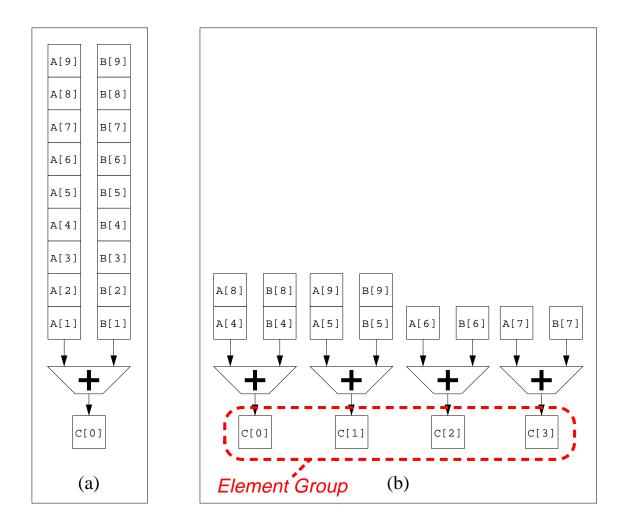

| 11 |                                                  | Linear .                                                                                                                                                                                                                            | Algebra Kernels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                           |

| 11 |                                                  | Linear .                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 93                                                                                          |

| 11 |                                                  | Linear .<br>11.1.1                                                                                                                                                                                                                  | Algebra Kernels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | )3<br>)3                                                                                    |

| 11 |                                                  | Linear .<br>11.1.1<br>11.1.2                                                                                                                                                                                                        | Algebra Kernels   19     Dot Product   19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | )3<br>)3<br>)5                                                                              |

| 11 | 11.1                                             | Linear .<br>11.1.1<br>11.1.2<br>11.1.3                                                                                                                                                                                              | Algebra Kernels   19     Dot Product   19     Matrix-Vector Multiply   19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | )3<br>)3<br>)5<br>)5                                                                        |

| 11 | 11.1                                             | Linear .<br>11.1.1<br>11.1.2<br>11.1.3<br>Image I                                                                                                                                                                                   | Algebra Kernels       19         Dot Product       19         Matrix-Vector Multiply       19         Matrix-Matrix Multiply       19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | )3<br>)3<br>)5<br>)5<br>)7                                                                  |

| 11 | 11.1                                             | Linear .<br>11.1.1<br>11.1.2<br>11.1.3<br>Image I<br>11.2.1                                                                                                                                                                         | Algebra Kernels       19         Dot Product       19         Matrix-Vector Multiply       19         Matrix-Matrix Multiply       19         Processing       19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | )3<br>)3<br>)5<br>)5<br>)7<br>)7                                                            |

| 11 | 11.1                                             | Linear 11.1.1<br>11.1.2<br>11.1.3<br>Image 1<br>11.2.1<br>11.2.2<br>11.2.3                                                                                                                                                          | Algebra Kernels19Dot Product19Matrix-Vector Multiply19Matrix-Matrix Multiply19Processing19Convolution19Compositing19Color Space Conversion19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | )3<br>)3<br>)5<br>)5<br>)7<br>)7<br>)7                                                      |

| 11 | 11.1                                             | Linear 11.1.1<br>11.1.2<br>11.1.3<br>Image I<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4                                                                                                                                                | Algebra Kernels19Dot Product19Matrix-Vector Multiply19Matrix-Matrix Multiply19Processing19Convolution19Compositing19Color Space Conversion19Discrete Cosine Transform for Image Compression20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-                          |

| 11 | 11.1                                             | Linear 11.1.1<br>11.1.2<br>11.1.3<br>Image I<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4                                                                                                                                                | Algebra Kernels19Dot Product19Matrix-Vector Multiply19Matrix-Matrix Multiply19Processing19Convolution19Compositing19Color Space Conversion19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | )<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>) |

| 11 | <ul><li>11.1</li><li>11.2</li><li>11.3</li></ul> | Linear .<br>11.1.1<br>11.1.2<br>11.1.3<br>Image I<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>Audio S                                                                                                                                | Algebra Kernels19Dot Product19Matrix-Vector Multiply19Matrix-Matrix Multiply19Processing19Convolution19Compositing19Color Space Conversion19Discrete Cosine Transform for Image Compression20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | )<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>) |

| 11 | 11.1<br>11.2<br>11.3<br>11.4                     | Linear<br>11.1.1<br>11.1.2<br>11.1.3<br>Image I<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>Audio S<br>IDEA                                                                                                                          | Algebra Kernels19Dot Product19Matrix-Vector Multiply19Matrix-Matrix Multiply19Processing19Convolution19Compositing19Color Space Conversion19Discrete Cosine Transform for Image Compression20Synthesis20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | - 3<br>- 3<br>- 3<br>- 3<br>- 3<br>- 3<br>- 3<br>- 3                                        |

| 11 | 11.1<br>11.2<br>11.3<br>11.4                     | Linear<br>11.1.1<br>11.1.2<br>11.1.3<br>Image I<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>Audio S<br>IDEA<br>Neural                                                                                                                | Algebra Kernels19Dot Product19Matrix-Vector Multiply19Matrix-Matrix Multiply19Processing19Convolution19Compositing19Color Space Conversion19Discrete Cosine Transform for Image Compression20Synthesis20Convolution20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                             |

| 11 | 11.1<br>11.2<br>11.3<br>11.4                     | Linear<br>11.1.1<br>11.1.2<br>11.1.3<br>Image I<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>Audio S<br>IDEA<br>Neural<br>11.5.1                                                                                                      | Algebra Kernels19Dot Product19Matrix-Vector Multiply19Matrix-Matrix Multiply19Processing19Convolution19Compositing19Color Space Conversion19Discrete Cosine Transform for Image Compression20Synthesis20Network Algorithms20Error Backpropagation Training20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | )<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>)<br>) |

| 11 | 11.1<br>11.2<br>11.3<br>11.4<br>11.5             | Linear<br>11.1.1<br>11.1.2<br>11.1.3<br>Image I<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>Audio S<br>IDEA<br>Neural<br>11.5.1<br>11.5.2                                                                                            | Algebra Kernels19Dot Product19Matrix-Vector Multiply19Matrix-Matrix Multiply19Processing19Convolution19Compositing19Color Space Conversion19Discrete Cosine Transform for Image Compression20Synthesis20Network Algorithms20Error Backpropagation Training20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | - 3<br>- 3<br>- 3<br>- 3<br>- 3<br>- 3<br>- 3<br>- 3                                        |

| 11 | 11.1<br>11.2<br>11.3<br>11.4<br>11.5             | Linear<br>11.1.1<br>11.1.2<br>11.1.3<br>Image I<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>Audio S<br>IDEA<br>Neural<br>11.5.1<br>11.5.2<br>SPECir                                                                                  | Algebra Kernels19Dot Product19Matrix-Vector Multiply19Matrix-Matrix Multiply19Processing19Convolution19Convolution19Color Space Conversion19Discrete Cosine Transform for Image Compression20Synthesis20Network Algorithms20Error Backpropagation Training20Kohonen Self-Organizing Feature Maps20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | - 3<br>- 3<br>- 3<br>- 3<br>- 3<br>- 3<br>- 3<br>- 3                                        |

| 11 | 11.1<br>11.2<br>11.3<br>11.4<br>11.5             | Linear<br>11.1.1<br>11.1.2<br>11.1.3<br>Image I<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>Audio S<br>IDEA<br>Neural<br>11.5.1<br>11.5.2<br>SPECir<br>11.6.1                                                                        | Algebra Kernels19Dot Product19Matrix-Vector Multiply19Matrix-Matrix Multiply19Processing19Convolution19Compositing19Color Space Conversion19Discrete Cosine Transform for Image Compression20Synthesis20Network Algorithms20Error Backpropagation Training20Kohonen Self-Organizing Feature Maps20t9520                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | - 3<br>- 3<br>- 3<br>- 3<br>- 3<br>- 3<br>- 3<br>- 3                                        |

| 11 | 11.1<br>11.2<br>11.3<br>11.4<br>11.5             | Linear<br>11.1.1<br>11.1.2<br>11.1.3<br>Image I<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>Audio S<br>IDEA<br>Neural<br>11.5.1<br>11.5.2<br>SPECirr<br>11.6.1<br>11.6.2                                                             | Algebra Kernels19Dot Product19Matrix-Vector Multiply19Matrix-Matrix Multiply19Processing19Convolution19Compositing19Color Space Conversion19Discrete Cosine Transform for Image Compression20Synthesis20Lerror Backpropagation Training20Kohonen Self-Organizing Feature Maps20Methodology20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | - 3<br>- 3<br>- 3<br>- 3<br>- 3<br>- 3<br>- 3<br>- 3                                        |

| 11 | 11.1<br>11.2<br>11.3<br>11.4<br>11.5             | Linear<br>11.1.1<br>11.1.2<br>11.1.3<br>Image I<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>Audio S<br>IDEA<br>Neural<br>11.5.1<br>11.5.2<br>SPECir<br>11.6.1<br>11.6.2<br>11.6.3                                                    | Algebra Kernels19Dot Product19Matrix-Vector Multiply19Matrix-Matrix Multiply19Processing19Convolution19Compositing19Color Space Conversion19Discrete Cosine Transform for Image Compression20Synthesis20Letror Backpropagation Training20Kohonen Self-Organizing Feature Maps20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20Methodology20 <tr< th=""><th>- 3<br/>- 3<br/>- 3<br/>- 3<br/>- 3<br/>- 3<br/>- 3<br/>- 3</th></tr<>               | - 3<br>- 3<br>- 3<br>- 3<br>- 3<br>- 3<br>- 3<br>- 3                                        |