# **Resilient Design Methodology for Energy-Efficient SRAM** by Brian Zimmer

# **Research Project**

Submitted to the Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, in partial satisfaction of the requirements for the degree of **Master of Science, Plan II**.

Approval for the Report and Comprehensive Examination:

## **Committee:**

Professor B. Nikolić Research Advisor

Date

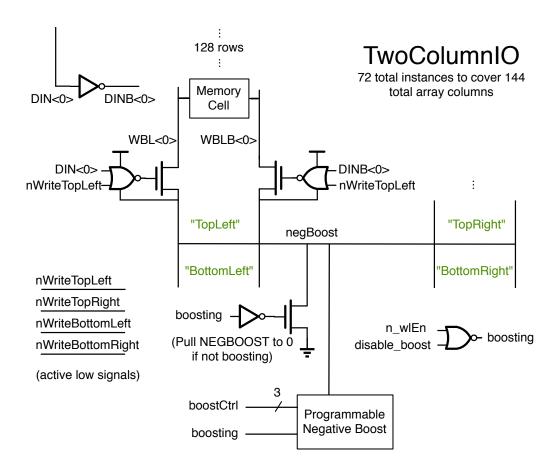

\* \* \* \* \* \*

Professor K. Asanović Research Advisor

Date

# Resilient Design Methodology for Energy-Efficient SRAM

Brian Zimmer bmzimmer@eecs.berkeley.edu

May 16, 2012

#### Abstract

Increasing process variability limits energy reduction in SRAM design by increasing the need for margining and preventing optimal supply voltage scaling. However, tolerating variability with resilient designs can prevent these limitations and enable future energy-efficiency improvements. Understanding resiliency requires understanding how design decisions affect error rates—therefore we propose a unified analytical framework for SRAM design that uses importance sampling of dynamic failure metrics to quantify the effect of different assist techniques, array organization, and timing on failure rates of a 28nm arrays at design-time. Dynamic voltage and frequency scaling (DVFS) systems show great potential to improve energy-efficiency, but require designs that are both operational and efficient over a wide range of supply voltages. We propose replica circuits that adapt array settings based on corners and supply voltage to optimize energy-efficiency over the entire supply voltage range. Last, we extend our results to improve micro-architectural design of an on-chip cache system.

# Contents

| 1                  | Introduction 5 |                                  |    |  |

|--------------------|----------------|----------------------------------|----|--|

| 2                  | Back           | ground                           | 6  |  |

| 2.1 SRAM Operation |                | SRAM Operation                   | 6  |  |

|                    |                | 2.1.1 6T Cell                    | 6  |  |

|                    |                | 2.1.2 8T Cell                    | 9  |  |

|                    | 2.2            | SRAM Array Organization          | 9  |  |

|                    |                | 2.2.1 6T Array                   | 9  |  |

|                    |                | 2.2.2 8T Array 1                 | 10 |  |

|                    | 2.3            | SRAM Failure                     | 11 |  |

|                    | 2.4            | Static vs. Dynamic Metrics       | 12 |  |

|                    | 2.5            | Readability Failure              | 13 |  |

|                    | 2.6            | Read Stability Failure           | 13 |  |

|                    | 2.7            | Writeability Failure             | 13 |  |

|                    | 2.8            | Hold Failure                     | 13 |  |

|                    | 2.9            | Leakage                          | 13 |  |

|                    | 2.10           | Other                            | 14 |  |

| 3                  | Anal           | ysis Methodology                 | 15 |  |

| U                  | 3.1            | Importance Sampling              |    |  |

|                    | 5.1            |                                  |    |  |

|                    |                |                                  | 15 |  |

|                    |                |                                  | 17 |  |

|                    |                | 3.1.3 Implementation             | 19 |  |

|                    |                | 3.1.4 Usage                      | 19 |  |

|                    |                | 3.1.5 Example: Analyzing results | 20 |  |

|                    |                | 3.1.6 Verification               | 21 |  |

|                    | 3.2            | SRAM Failure Analysis            | 21 |  |

|                    |                |                                  |    |  |

|   | 3.3  | Dynan  | nic Failure Metrics Test Chip                                       | 22 |

|---|------|--------|---------------------------------------------------------------------|----|

|   |      | 3.3.1  | 6T                                                                  | 22 |

|   |      | 3.3.2  | 8T                                                                  | 24 |

| 4 | SRA  | M Vmi  | in Analysis                                                         | 26 |

|   | 4.1  | Effect | of bitline capacitance on 6T SRAM failures                          | 26 |

|   | 4.2  | Effect | of bitline capacitance on 8T SRAM failures                          | 27 |

|   | 4.3  | Effect | of clock period on 6T SRAM failures                                 | 27 |

|   | 4.4  | Effect | of process corners                                                  | 28 |

|   | 4.5  | Effect | of sense amplifier offset on readability failure                    | 29 |

|   | 4.6  | Effect | of assist techniques on 6T SRAM failures                            | 29 |

|   |      | 4.6.1  | Effect of wordline boost as a readability and writeability assist   | 32 |

|   |      | 4.6.2  | Effect of wordline droop as a read stability assist                 | 34 |

|   |      | 4.6.3  | Effect of cell Vdd boost as a readability and read stability assist | 34 |

|   |      | 4.6.4  | Effect of cell Vdd collapse as a writeability assist                | 34 |

|   |      | 4.6.5  | Effect of cell GND boost as a writeability assist                   | 34 |

|   |      | 4.6.6  | Effect of negative bitline as a writeability assist                 | 35 |

|   |      | 4.6.7  | Effect of partial bitline precharge as a stability assist           | 35 |

|   |      | 4.6.8  | Effect of negative cell GND as a readability assist                 | 35 |

|   |      | 4.6.9  | Effect of other assist techniques                                   | 36 |

|   | 4.7  | Effect | of assist techniques on 8T SRAMs                                    | 37 |

|   |      | 4.7.1  | Leakage                                                             | 37 |

|   | 4.8  | Effect | of hierarchical bitlines                                            | 37 |

|   | 4.9  | Effect | of ECC                                                              | 37 |

|   |      | 4.9.1  | (9,8) Parity Detection                                              | 38 |

|   |      | 4.9.2  | ECC: (72,64) SEC-DED                                                | 39 |

|   | 4.10 | Compa  | arison of Scheme Effectiveness                                      | 40 |

|   | 4.11 | Effect | of Cell Sizing                                                      | 41 |

|   | 4.12 | 6T Overall Failure Minimization       | 41 |

|---|------|---------------------------------------|----|

|   | 4.13 | 8T Overall Failure Minimization       | 42 |

| _ |      |                                       | 42 |

| 5 | SRA  |                                       | 43 |

|   | 5.1  | Overview                              | 43 |

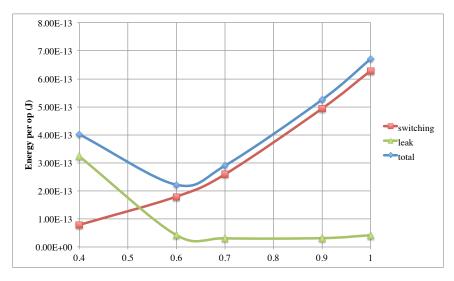

|   | 5.2  | Emin                                  | 43 |

|   | 5.3  | Energy measurement                    | 44 |

|   |      | 5.3.1 L1 Cache Data Array             | 44 |

|   |      | 5.3.2 L2 Cache Data Array             | 44 |

|   | 5.4  | Energy per read operation             | 45 |

|   |      | 5.4.1 Nominal                         | 45 |

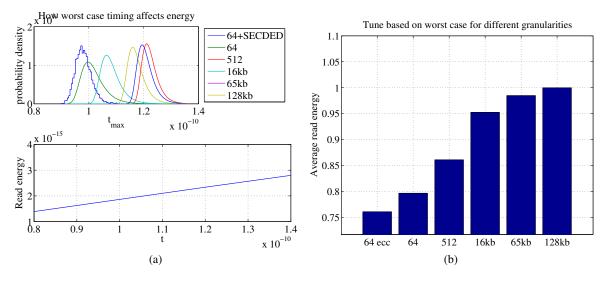

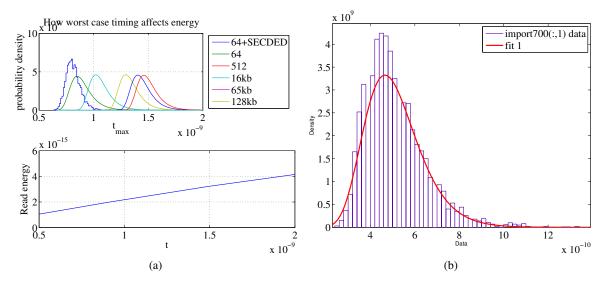

|   | 5.5  | Optimal read timing                   | 45 |

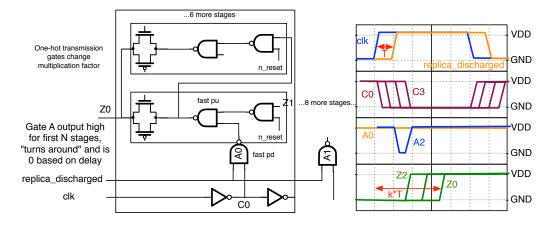

|   | 5.6  | Generating optimal read timing        | 47 |

|   | 5.7  | Hierarchical vs. timing               | 48 |

|   | 5.8  | Energy per write operation            | 48 |

|   |      | 5.8.1 Optimal write timing            | 49 |

|   |      | 5.8.2 Generating optimal write timing | 49 |

|   | 5.9  | Energy per inactive cycle             | 50 |

|   | 5.10 | Assist Overhead                       | 50 |

|   | 5.11 | Error Monitoring and Response Cost    | 51 |

|   |      | 5.11.1 BIST                           | 51 |

|   |      | 5.11.2 ECC                            | 51 |

|   | 5.12 | Adaptivity                            | 51 |

| 6 | Onti | mizing SRAM for caches                | 53 |

| U | Opu  |                                       |    |

|   | 6.1  | Necessity of Error Correction         | 53 |

|   | 6.2  | L1 Correction Methods                 | 53 |

|   | 6.3  | System Assumptions                    | 54 |

|   |      | 6.3.1 ECC Schemes                     | 55 |

| 8 | Con  | clusion                                        | 66 |

|---|------|------------------------------------------------|----|

|   |      | 7.3.1 Methods to respond to errors             | 65 |

|   | 7.3  | Methods to detect errors                       | 64 |

|   | 7.2  | Methods to reduce energy                       | 64 |

|   | 7.1  | Methods to reduce Vmin                         | 63 |

| 7 | SWA  | SWAAT: SRAM with Adaptive Assist Techniques    |    |

|   |      | 6.10.2 Summary of aggressive scaling in caches | 62 |

|   |      | 6.10.1 6T vs. 8T                               | 62 |

|   | 6.10 | Effect of performance on energy                | 60 |

|   | 6.9  | Effect of voltage scaling                      | 58 |

|   | 6.8  | Sensitivity of model to assumptions            | 58 |

|   | 6.7  | Write-back                                     | 57 |

|   | 6.6  | Write-through                                  | 57 |

|   | 6.5  | Design Intuition                               | 56 |

|   |      | 6.4.2 Write-back                               | 56 |

|   |      | 6.4.1 Write-through                            | 56 |

|   | 6.4  | Cache Simulator                                | 55 |

## **1** Introduction

Embedded memories are critical in CMOS integrated-circuit designs. Different memory options can be best differentiated by their speed, energy, and memory density characteristics. SRAM fills a sweet-spot between DRAM and flip-flops, and have moderate speed, density and energy. Improving all of these metrics in SRAM enables larger amounts of faster on-chip memory, which is particularly important for providing new opportunities in mobile devices. We investigate the effect of various design decisions on all three primary design metrics—speed, energy, and area density—with a specific focus on energy efficiency. Because many integrated circuits contain large SRAMs with many cells, failures caused by manufacturing variability become common, and a fourth metric—resiliency—must be considered. Through better understanding of failure cases and self-monitoring SRAM design, we can both remove the margins currently required to maintain error-free operation, and understand how design decisions can improve energy efficiency. We propose a methodology to quantify resiliency and use this to perform an extensive design space exploration of SRAM.

Previous works have investigated the various pieces necessary to understand how errors affect SRAM energy-efficiency, but none have combined the results to form a cohesive conclusion. Importance sampling has been used to estimate SRAM stability [1]. Recently, various types of assist circuitry have been proposed to enable low voltage operation [2], [3], [4], [5]. A comprehensive analysis comparing many different assist techniques has been performed, but used only static metrics [6]. The effect of error correction on cache energy has been studied, but does not account for correction cost and neglects details that have significant impact on final results [7].

Section 2 introduces SRAM design, discusses operation details, and defines metrics that measure SRAM failure.

Section 3 explains our resiliency measurement scheme, which allows for accurate analysis of rare failure events.

Using this resiliency measurement scheme, Section 4 examines how assist techniques, array organization, and error correction affect bit-error rate (BER) and minimum operating voltage (Vmin).

Section 5 extends our analysis to incorporate energy, and discusses possible methods to improve average energy per operation, and absolute minimum energy per operation (Emin).

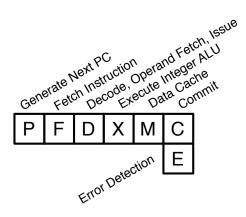

Using the methodology and modeling intuition developed, Section 6 serves as a case study to analyze how supply scaling and finite error rates affect cache design for a dynamic voltage and frquency scaling (DVFS) processor.

Finally, we use the results of our design exploration to propose a SRAM design that optimizes energy efficiency in Section 7. We optimize for use in a DVFS system, which requires dynamic configuration to obtain maximum energy efficiency over a wide range of possible supply voltages.

## 2 Background

### 2.1 SRAM Operation

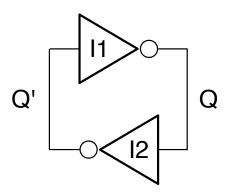

There are many different ways to design an SRAM cell, but almost every type of cell will always have a pair of cross-coupled inverters (I1/I2) that act as a storage element—holding both the true and complementary value of the data on two different nodes (Q/Q'), as shown in Figure 1.

Figure 1: Two inverters (I1/I2) form the storage element in an SRAM cell.

As long as the supply voltage remains high enough, any voltage change on either node will be counteracted by the feedback and tend to return to the original value. For example, if Q is at VDD and Q' is at 0, then any positive charge deposited on Q' will be discharged through the NMOS in I2. This feedback makes SRAM static, as opposed to other types of memory such as DRAM which rely on charge held on a floating capacitor.

Cell designs differ by how many devices provide access to these internal nodes, and are typically named by the total number of transistors in the cell. This paper will focus on the two most popular flavors–the 6T cell and the 8T cell.

#### 2.1.1 6T Cell

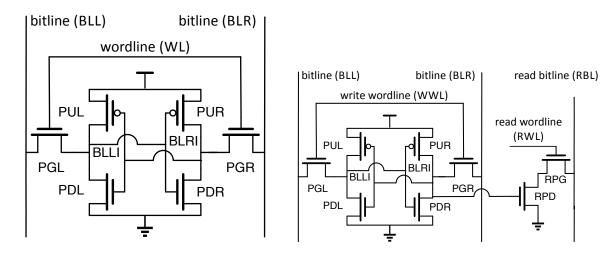

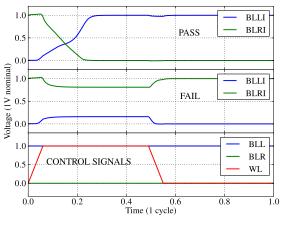

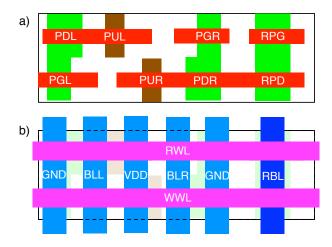

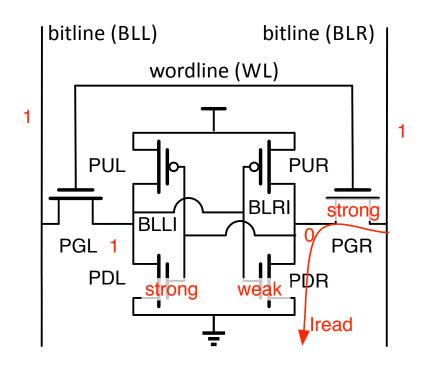

The 6T SRAM cell is shown in Figure 2a. Pull-up-left (PUL), pull-down-left (PDL), pull-up-right (PUR), and pull-down-right (PDR) together form the cross-coupled inverter pair. Two extra NMOS devices, pass-gate-left (PGL) and pass-gate-right (PGR), provide access to the internal nodes from two shared bitlines, bit-line-left (BLL) and bit-line-right (BLR).

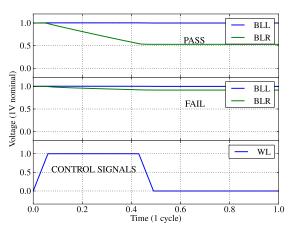

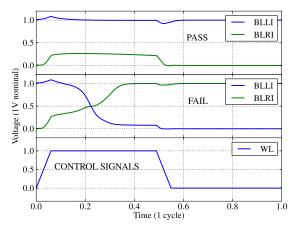

Figure 3a shows a read operation. During the read operation, both bitlines are precharged high, and then left to float. Their voltage is held by the wire capacitance of the bitlines combined with the diffusion capacitance of PGR or PGL. The gate of PGL and PGR will be turned on by driving the wordline high. Assuming BLLI is high and BLRI is low, then the gates of PDR and PGR will both be high, and together they will form a conductive path to decrease the voltage of BLR. External circuitry can then respond to the voltage difference between BLL and BLR to output the value of the cell if the cell established a large enough voltage difference

by the end of the cycle. The voltage at BLRI will be set by the relative strengths of PDR and PGR, and if this node jumps above the switching threshold of the PUL and PDL inverter, the value of the cell could accidentally flip, as shown in Figure 3b.

Figure 3c shows a write operation. During the write operation, one bitline is precharged high, while the other bitline is held at 0 through NMOS devices connected to ground. The pass-gate transistors PGL and PGR are turned on by raising the wordline voltage to VDD. Depending on the relative strengths of the NMOS pass-gate and PMOS pull-up, the internal node on the side where the bitline is at 0 should get pulled below the switching threshold of the inverter driving the other side of the memory cell, and positive feedback will flip the value stored in the cell. If the pass gate isn't sufficiently stronger than the pull-up device, then this node will not decrease enough to flip the value of the cell.

(a) Schematic of a six-transistor (6T) SRAM cell

(b) Schematic of an eight-transistor (8T) SRAM cell

Figure 2: SRAM Cell Schematics

(a) Example of SRAM readability.

(c) Example of SRAM writeability.

Figure 3: SRAM operation waveforms.

## 2.1.2 8T Cell

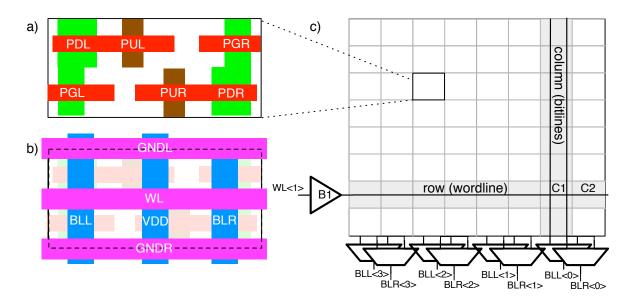

The 8T SRAM cell is shown in Figure 2b, and is identical to the 6T cell except for the addition of two extra devices, read-pull-down (RPD) and read-pass-gate (RPG). Write operations are performed in exactly the same way as in the 6T cell by turning on the write wordline. However, reads are done by turning on the read wordline (RWL) and leaving the write wordline (WWL) off. If BLRI is high, then RPD and RPG will both have a high voltage at their gates, and will discharge the read bitline. A skewed inverter connected to the read bitline can recognize this voltage drop and determine the correct read value. There are a few advantages to this approach. First, reads cannot upset the cell as RPD is decoupled from BLRI through a gate. Because of this, the pull down devices can be made minimum size because they don't need to be stronger than the pass gates to prevent a read upset. Second, the additional transistor allows a simultaneous read and write operation to the cell because the read and write bitlines are independent and are controlled by separate wordlines. Third, reads are no longer differential, whenever BLTI stores a 0, read bitline will not change voltage and therefore will not consume energy. When used as a cache, the realization that the majority of bits stored will be 0 allows the 8T SRAM to save energy during read operations [8].

## 2.2 SRAM Array Organization

SRAM cells are organized into arrays in order to share control circuitry. However, their organization will impact overall SRAM effectiveness. For example, when more cells share a bitline, there is a larger bitline capacitance that a pull-down transistor must discharge.

#### 2.2.1 6T Array

Figure 4c shows a small 8 by 8 array with 64 total cells. All cells on the same row share the same wordline (WL) wire. All cells on the same column share the same bitline (BLL and BLR) wires. Often the number of entries will be much larger than the word size, which would result in many rows (and very long bitlines) and few columns (and very short wordlines). To keep prevent excessive bitline capacitances, multiple columns are interleaved together. In this example, BLL[0] is connected to BLL for both cells in the column of C1 and C2 through a multiplexer. To read cell C1, the wordline will still be on for cell C2, in a state known as "half-write". For reads, every column's bitlines will experience a read due to an accessed cell on the wordline, but only one column will be connected to a sense amplifier through the multiplexer. In this case, the select signal for the multiplexer (or with column-specific circuitry), but all other cells on the activated wordline will be unintentionally reading.

Figure 4a shows the transistor layout for a given cell, where poly is red, NMOS active is green, and PMOS active is brown. Note that the pull-down devices are larger than the pass gates (to ensure read stability) and the pull-up devices are smaller than the pass gates (to ensure write-ability).

Figure 4b shows the metal layers that connect to each cell. The direction of metal wires will determine side effects for assist techniques discussed later. VDD runs vertically along a column, and GND is supplied from different wires for the left and right sides and is shared with the rows above and below.

Figure 4: (a) Layout of transistors in a 6T SRAM cell. (b) Layout of metal layers for a 6T SRAM cell. (c) Generic overview of SRAM array design.

## 2.2.2 8T Array

8T arrays are organized in the same manner as 6T arrays. Figure 5a shows transistor layout for an 8T cell. The six transistors in common with the 6T array have not changed, and the two additional devices are added to the right side of the device.

Figure 5b shows a very different wiring scheme than the 6T cell. Now that each row needs two separate wordlines, the horizontal GND wires have been moved to become vertical in the extra space provided by the wider cell. Also, the extra read bitline needed is routed vertically.

Figure 5: (a) Layout of transistors in a 8T SRAM cell. (b) Layout of metal layers for a 8T SRAM cell.

## 2.3 SRAM Failure

All transistors must be sized at design time to minimize failure. Unfortunately, there are many trade-offs that prevent an optimal cell size. One of the biggest constraints is area. For example, readability can be improved by making the PG and PD larger, but this increases the area of the cell. Also, the trade-off between read stability and writeability creates another constraint. The PG needs to be stronger than the PU to allow writeability, but needs to be weaker than the PD to prevent read stability problems. Incorrect sizing can produce cells that are much more likely to fail.

In addition, there are many non-idealities in silicon that can cause SRAM failure even for well-designed cells:

- Individual cell variability (eg. threshold voltage, width, length, etc)

- Systematic variability (eg. different corners)

- Random Telegraph Noise

- Sleep supply voltage

- Supply noise

- Aging

- Temperature

Beyond this, there are effects that can cause array failure even for well-behaving cells:

- Sense-amplifier offset

- Control-timing variation

- Cell leakage

In order for SRAMs to function, these effects must be margined, but margining will cause overhead. For example, an SRAM can be margined such that the bitline discharges more than needed for typical cells so that in the worst case the bitline discharge is still enough, but this wastes energy every cycle.

Ideally, the SRAM should adapt dynamically to remove the need for margining. But because cell sizing cannot be changed, other techniques must be used to change the strength of each device. In the past, body biasing has been used to change threshold voltages, but our simulations showed that this has very little effect in bulk 28nm. Therefore the only possible way to change strengths is to change the wordline voltage, bitline voltage, cell VDD, and cell GND. Also, these voltages can be set differently for different operations, which can decouple constraints in traditional SRAM design. For example, by changing the bitline voltage, the strength of the pass gate can be made different for read and write operations, and therefore remove the constraint between writeability and read stability.

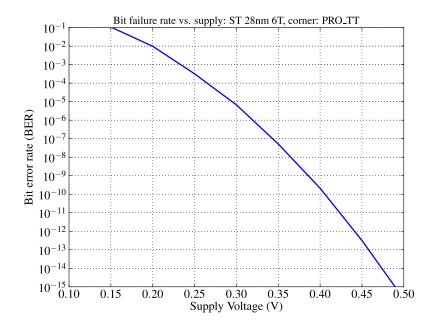

For an SRAM to operate correctly, failures need to be very rare events. The maximum probability of failure is set by both the number of cells on a chip and the required yield. The yield can be calculated with the following equation, where n is the number of bits on the chip and e is the probability that a bit causes an error (bit-error rate, also referred to as BER).

$$yield = (1 - e)^n \tag{1}$$

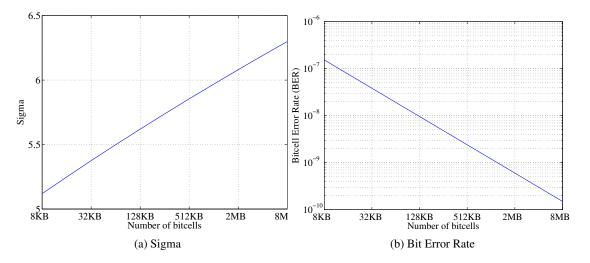

Traditionally, metrics that predict failure have been assumed to be Gaussian, and report the probability of failure in terms of  $\sigma$ . In order for a design to be considered functional, a metric's value must be considered passing under  $x \sigma$  (x being typically between 5 and 7) deviations from the mean. While this metric is intuitive, it complicates analysis for SRAMs with ECC, and assumes that the error distribution is Gaussian, so it will not be used. Figure 6 plots the BER (e) or  $\sigma$  required for 99% yield for different SRAM cell counts per chip. We will assume a BER of  $10^{-9}$  is required, but this rate can be as high as  $10^{-6}$  for small designs.

Figure 6: Effect of chip SRAM cell count on required failure probability.

#### 2.4 Static vs. Dynamic Metrics

There are four ways a cell can fail: it can fail to write (writeability error), fail to read (readability error), change values during a read (stability error), or change values during a retention state (retention error). Traditionally, static metrics (calculated as simulated DC operating points) have been used to quantify failure rates. For example, the static noise margin is defined as the size of the square inside the plot of the left and right-side transfer functions during a read [9], known as the Static Noise Margin (SNM). To find how likely failure is for a large array, a short Monte Carlo simulation is run to determine a distribution of SNM values, and the results are fit to a Gaussian distribution. The standard deviation  $\sigma$  is computed for the fit distribution, and the failure metric is extrapolated to N $\sigma$  (where N is typically between 5 and 7 depending on the target array size). If the SNM at N $\sigma$  from the mean is larger than 0, then a large array will not be functional. However, this approach suffers from two problems. First, SNM is a static metric that does not accurately track stability because it assumes infinite access time and does not account for any transient effects. Second, there is no guarantee that SNM is actually Gaussian at N $\sigma$  from the mean. Silicon measurements have shown that static read stability metrics overestimate failure rates while writeability metrics underestimate failure rates [10]. Writeability traditionally uses a static metric that measures how low the bitline voltage must be for the cell to change state. Note that readability does not have a corresponding static metric as readability strongly depends on the peripheral circuitry implementation. We will focus on the effect of design decisions on dynamic metrics and will use statistical sampling that does not assume Gaussian distributions and accounts for finite access times and transient effect.

## 2.5 Readability Failure

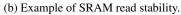

If a cell cannot be successfully read during a cycle, a readability failure has occurred. For a 6T SRAM, a read is successful if the voltage of the bitline on the side holding a 0 is more than  $\Delta V$  below the voltage of the other bitline when the wordline turns off. The offset of the sense amplifier sets the required  $\Delta V$ . Figure 3a shows both a successful and unsuccessful read. For an 8T SRAM, reads are single ended, so a read is successful if the read bitline drops below a predetermined switching threshold.

## 2.6 Read Stability Failure

If the value of a cell changes during a read cycle, a read-stability failure has occurred. Figure 3b shows a read with and without an upset. This type of failure can occur to any cell on the activated wordline. The worst read-stability case occurs when there are multiple read operations in a row, as the weakened cell can flip on the second cycle, so stability is checked after an additional read. We use this pessimistic measure of stability, which accounts for successive reads.

## 2.7 Writeability Failure

If the value of a cell cannot be changed during a write cycle, a writeability failure has occurred. Figure 3c shows both a successful and unsuccessful write operation. For marginally writeable cells, it is possible that by the end of a clock cycle, the value inside has not been completely written and is near the meta-stability point. An optimistic measure would wait a long period of time before checking the value of the internal nodes while a pessimistic measure would check the internal nodes immediately after the wordline turns off. If there is a read-after-write or write-after-write operation, an optimistic measure will be wrong. Therefore, we use a pessimistic measure by checking to make sure that the high internal node is within 30% of Vdd at the end of the write cycle. We found cells that met this target completed ultimately completed the correct write operation.

## 2.8 Hold Failure

One of the best ways to reduce energy consumption of an idle SRAM is to decrease leakage by decreasing the supply voltage. Because no read or write operations need to be performed while the array is idle, the minimum acceptable supply will be lower than Vmin (the minimum voltage required for error-free reads and writes) during lower operation. However, if the supply becomes too low, the feedback provided by the cross-coupled inverters becomes too weak and the cell can flip. The voltage at which cells begin to flip is known as the data retention voltage (DRV).

A dynamic test can also be implemented to measure the data retention voltage. Based on an assumption about the rise and fall times of the power rails, the supply is dropped from nominal to  $V_{TEST}$  for a long period of time (eg. 1ms) then raised again. If the cell does not retain the same value throughout the test an error is recorded. Figure 7 shows the result of this test. The DRV is about 375mV for a BER of  $10^{-9}$ .

## 2.9 Leakage

For our cell/technology, leakage is very low and has no effect on failures. However, for bitcells that leak, many more issues appear. For example, the readability of a cell becomes dependent on the value of the other cells on the same bitline, as leakage can pull down the bitline that should be left high and increase the amount of discharge needed on the other bitline in order to establish enough differential for the sense

Figure 7: Hold failure rate (data retention voltage) for a 6T SRAM.

amplifier. Also, leakage of the low node through the pull down can cause the entire array to draw a large amount of energy even during inactivity, so leakage reduction design techniques need to be investigated. Last, various assist techniques that affect the pass gate will have a strong effect on leakage, which will increase the probability that the assist causes a stability failure and increase the energy overhead.

#### 2.10 Other

Some assist techniques will create other possibilities for failure. If the value of an non-accessed cell changes during a write operation, a write-stability failure has occurred. This type of failure can occur on any column that is being written. Typically, it will only occur if a negative bitline assist is used as the overdrive of the PG on not accessed cells is not zero.

## 3 Analysis Methodology

SRAM arrays can fail if one out of millions of cells fail. Monte Carlo simulations can be used to measure the effect of variability, but in order to find failure events, hundreds of millions of simulations would be required, which would be unfeasible. If the quantity under measurement is known to be Gaussian, these results can be predicted with much less simulation time. A few simulations can be made to approximate the mean and deviation of the Gaussian distribution, and the probability of failure many  $\sigma$  from the mean (for example, six  $\sigma$ ) can be used to estimate what the actually failure rate will be if there were millions of cells. This has been done for metrics defining failure, such as Static Noise Margin, that look Gaussian. However the tails do not behave as Gaussian. Ideally we should run Monte Carlo only at the tail of the distribution, and then determine how the probability of failure at the tail relates to the nominal case—a process known as importance sampling [1].

This approach will not only determine failure probability, it will also determine the relative strengths of devices that cause failure, and therefore explains *why* a cell fails. From this information, interesting observations can be made about how cells fail that are often non-intuitive or contradictory to traditional explanations.

Most importantly, this algorithm can be adapted to different circuits with a different number of variables in a few lines of code. All that is needed is a netlist describing which variables should be part of the design space which returns a pass/fail signal for a given threshold shift.

## 3.1 Importance Sampling

## 3.1.1 Definition

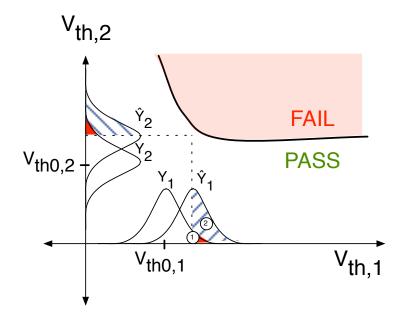

Figure 8 shows a graphical representation of the main idea behind importance sampling for a simplified case of two devices. The two axes represent the threshold voltages of the two devices, with their nominal values labeled as  $V_{th0,n}$ . Under the assumption that threshold voltage deviations due to random dopant fluctuation can be modeled with a Gaussian distribution, Monte Carlo will simulate the two-device circuit with threshold probability-density functions (PDF) given by  $Y_1$  and  $Y_2$ , where the mean is the device's nominal value, and the  $\sigma$  is given by  $\frac{A_{Vt}}{\sqrt{W*L}}$ . For this simplified example, assume the failure contour exists as shown in the upper right quadrant, where if both devices are weak, the metric represented by the failure contour fails. Ordinary Monte Carlo will only sample at a failure event for the very small probability shown by region (1).

Figure 8: Importance sampling provides more information about the failure region by shifting the mean of each device's threshold voltage.

For importance sampling, we will change the mean of  $Y_1$  and  $Y_2$  to create a new PDF, labeled  $\hat{Y}_1$  and  $\hat{Y}_2$ , so Monte Carlo samples failure events with the probability given by region (2). To determine how often these failures would occur without the artificial shift, we need to unbias these samples. If we define f(x) as the joint PDF of the original distribution, and  $\hat{f}(x)$  as the joint PDF of the shifted distribution, we can define the weight factor in Equation 4. Now, we can estimate the probability of failure as  $p_{IS}$ , and terminate sampling when  $\rho(\hat{p}_{IS})$  is < 0.1 as shown in Equation 6 [1].

$$f(x) = PDF \text{ of } Y_1, \cdots, Y_6 \tag{2}$$

$$\hat{f}(x) = PDF \text{ of } \hat{Y}_1, \cdots, \hat{Y}_6 \tag{3}$$

$$w(x) = \frac{f(x)}{\hat{f}(x)}, \text{ for all } x.$$

(4)

Now, we can estimate the probability of failure as:

$$p_{\rm IS} = \frac{1}{N} \sum_{i=1}^{N} \begin{cases} w(\hat{X}_i) \text{ if } \hat{X}_i \in A\\ 0 \text{ otherwise} \end{cases}$$

(5)

To determine when this estimate has reached the confidence levels required, we use the metric defined in [1] to track the variance of our estimate.

$$\rho(\hat{p}_{IS}) = \frac{\sqrt{VAR(\hat{p}_{IS})}}{\hat{p}_{IS}} \tag{6}$$

However, running importance sampling as described solves only half of the problem, as finding the sampling distribution  $\hat{f}(x)$  becomes complicated for a many-dimensional design space. This sampling distribution can be described as a set of *n* threshold voltage mean shifts for *n* devices, and can be described graphically as a point in an *n*-dimensional space of  $\Delta V_{th}$ .

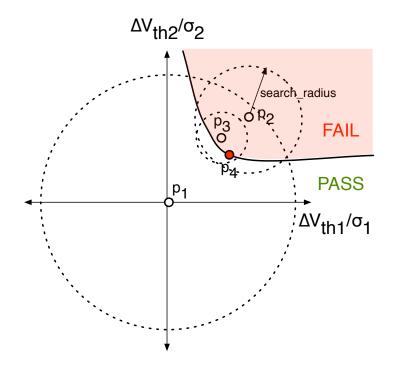

Figure 9: Graphical example of our variable-radius algorithm for hypothetical two-device circuit.

### 3.1.2 Algorithm

However, finding the optimal sampling distribution  $\hat{f}(x)$  becomes complicated for a multi-dimensional design space. For quick convergence, the set of mean shifts must be the multi-dimensional most probable failure point (MPFP), which is the point closest in distance to the origin. We propose an improvement that uses uniform sampling of a variable radius *n*-dimensional sphere around changing points with a similar idea to the method proposed in [11].

Pseudo-code for the algorithm is provided in Algorithm 1, and Figure 9 shows a simple case of a two-device circuit graphically. The space being searched is defined as shifts in thresholds for each device (normalized by their standard deviation), and the desired point is the closest point to the origin. Initially, a large search of  $5\sigma$  in all directions is uniformly sampled from the origin (p1) and the closest failure point p2 is found. Now, sampling continues with a decreased search space until no closer points are found. Last, importance sampling is run to determine the final bit error rate.

```

Algorithm 1 Find the BER for a given schematic

```

$\vec{p} = [0 \ 0 \dots 0]$  > Each entry in the vector represents the amount of threshold voltage shift (from the mean), in terms of  $\sigma_{Vt}$ , for each device.

**function** SAMPLE(*search\_radius*, *current\_shifts*, *num\_sims*)

#### repeat

For each entry in the vector  $\vec{p}$ , choose a shift from a random uniform distribution with endpoints equal to [current\_shift - search\_radius,current\_shift + search\_radius]

Run circuit simulator to determine whether metric is pass/fail for device thresholds given by chosen shift

until num\_sims simulations completed

```

return Failed point with smallest ||p||

end function

r = 7

while TRUE do

next_p = \text{SAMPLE}(r, \vec{p}, 1000)

if next_p empty then

r = 2 * r

else

r = \|p\| - \|next\_p\|

\vec{p} = ne\vec{x}t_{-}p

if r < 0.002 then

break

end if

end if

end while

Run Importance Sampling at \vec{p}

```

▷ didn't find a failure point

▷ no longer making progress

An alternative implementation uses sensitivity analysis to converge to the most probable failure point [12]. In the proposed algorithm and [11], only a binary result is determined—pass or fail. However, if a metric can be developed that has a numerical value, the sensitivities of this variable from each transistor can be calculated in order to move through the multidimensional sample space. For example, to test for read stability, at each point the critical wordline pulse needed to upset a cell can be measured. Then, each device threshold voltage is changed slightly (while the other devices remain at their nominal values), and the effect on the critical wordline pulse is measured. Using convex optimization, the total threshold shift of each device is minimized while the metric is kept close to the target. However, we found that importance sampling fails to complete in a reasonable time in about half of trials for this approach. An in-depth exploration of methods to improve this convergence found that due to the computational cost of calculating these sensitivities, the correlation between sensitivities, and widely varying start locations, even a heavily optimized (and no longer general) algorithm failed to outperform the variable scatter algorithm described here.

### 3.1.3 Implementation

Threshold voltage variation due to random dopant fluctuation has been shown to be the primary source of failure in SRAM cells. Therefore this algorithm models variability by changing the thresholds of all transistors in the SRAM cell. Other sources of variability, such as width, length, or mobility differences, could also be modeled using this same system by just increasing the number of variables, but would create a larger solution space and require more simulation time.

For each dynamic test (writeability, readability, and read stability) a small testbench is developed to measure for pass or failure through a transient simulation. This netlist is parameterized for different assist techniques and voltages, bitline capacitance, wordline pulse width, access time, sense amplifier offset, corners, and each device threshold mean and deviation can be set outside of the netlist.

A Matlab program runs importance sampling by changing the input to these netlists, running short bursts of Monte Carlo, then collects and parses the results to decide the next step in the algorithm.

#### 3.1.4 Usage

The importance sampling script infrastructure was designed to be as flexible as possible. In order to simulate failure rates, only three things are needed:

- 1) Model files that allow changing the mean and deviation of the threshold voltage

- 2) A simulation netlist that a) returns a pass/fail signal that is 1 for pass and 0 for fail b) parameters to each device whose variability needs to be simulated to set the mean and deviation c) returns the threshold voltages of each device under study

- 3) A function call sends a list of all devices to change the threshold for

This flexibility enables the in-depth study of SRAM failures in a short amount of time. One simulation point takes about 4 minutes on an 8-core machine. This code has been successfully extended to measure other circuits such as a sense-amplifier.

## 3.1.5 Example: Analyzing results

This methodology allows us to examine very specific failure mechanisms. For example, we will later show that read stability is worse in the FF corner than the FS corner. Traditional thinking suggests that the FF corner should be better due to the following scenario shown in Figure 10 and explained below.

Figure 10: A 6T cell that is very susceptible to a read stability upset.

BLRI holds a 0 and BLLI holds a 1. BLRI experiences a bump due to the voltage divider between PGR and PDR, and if PGR is strong and PDR is weak, this node unintentionally bumps even higher. Therefore PUL and PDL will both be on, especially if PDL is strong. This will cause a fight between PGL/PUL and PDL where PDL is unintentionally decreasing the node from 1. One might guess that the FF corner would be more stable than the FS corner (different PMOS strengths) because in the FF corner, PUL is stronger than PDL, so BLLI will be held high and the cell should be stable, while in the FS corner, PUL is weaker so it is easier for PDL to pull BLLI down and the cell to flip.

However, in reality, FS is a more stable case and importance sampling can explain why. For the FS corner, PUR is intrinsically weak because of the corner, and cannot complete the read stability upset regardless of how high BLLI jumps because it cannot pull BLRI high. So even though PUL cannot hold BLLI high, PUR also cannot pull BLRI high. This failure situation needs PUR to be strong in addition to the requirements shown in Figure 10, so is less likely to occur, and FS is more stable. Importance sampling provides a way to view waveforms at these failure points and determine actual causes for failure, yielding much more intuition about how to prevent SRAM failure.

### 3.1.6 Verification

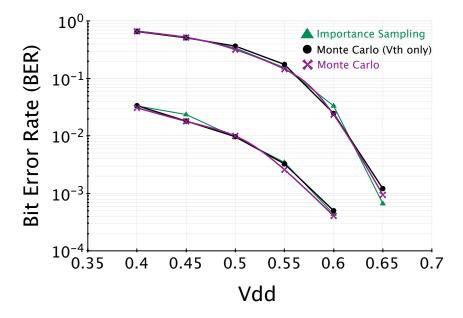

Figure 11: Comparison of predicted bit-error rates using both Monte Carlo and importance sampling for  $\rho < 0.1$  for both readability and writeability tests.

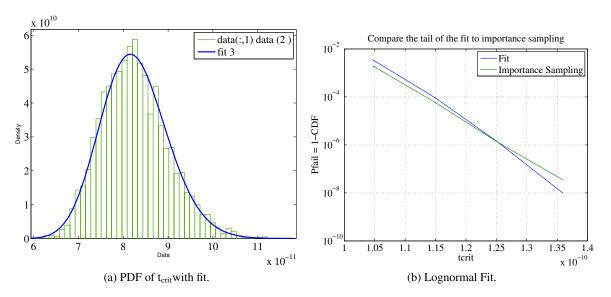

Our importance sampling results match closely with Monte Carlo simulation, as shown in Figure 11. Note that our IS implementation assumes that the only source of variation is Vth variation, yet can be seen to track full MC well. BER smaller than  $10^{-4}$  cause an excessive MC runtime. Other studies have shown that IS matches MC for longer simulations [1].

#### 3.2 SRAM Failure Analysis

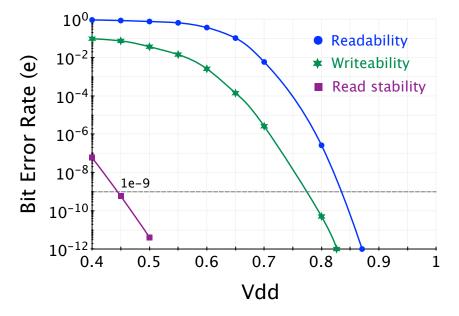

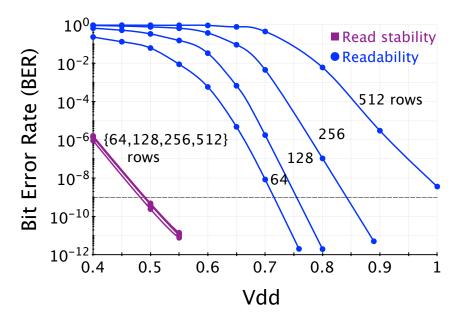

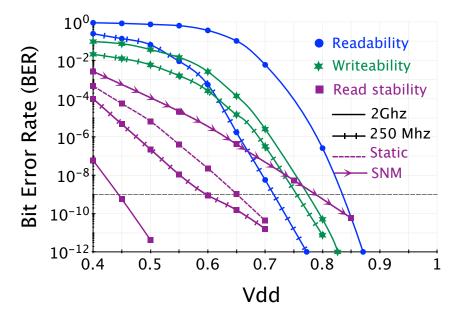

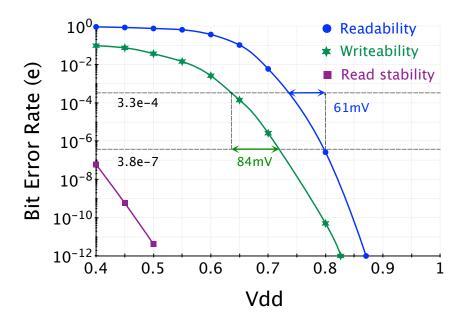

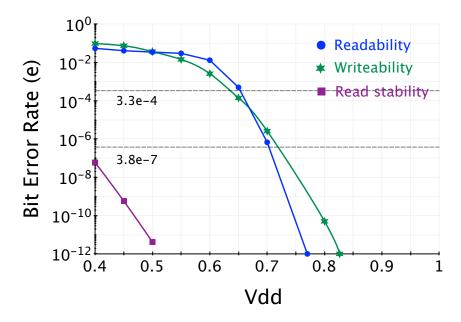

Figure 12 plots the failure rates for each mode of failure—readability, writeability, and read stability—versus supply voltage. Points at the top of the graph represent almost constant failures, while points at the bottom of the graph represent very improbable failures.

For an array to be considered working, both its read and write operations must fail less than some target BER (set by number of elements on a die and desired yield). In this paper,  $10^{-9}$  is commonly used. For the case of readability and writeability failure curves, the one with the highest BER (the closest to the top of the graph) is chosen to be dominant, because these operations are independent. However readability and read stability can both occur on the same cycle. Generally, the failure rate of one is orders of magnitude higher than the other, so will still assume that the highest BER dominates.

There are two ways to interpret this graph. First, for a given supply voltage, each mode of failure will occur with a different probability. Therefore to optimize the cell, the curves can be shifted up and down until the BER are similar for a given supply voltage. Second, for a given target BER, different designs will have different minimum voltages, so to enable a more energy-efficient operating point, the curves need to be moved to the left. Changing cell sizing, array design, and assist techniques can all move these curves and allow for cell optimization.

Vmin is defined as the voltage such that all failure metrics have a BER of less than  $10^{-9}$ . In this figure, Vmin is 830mV.

Figure 12: Readability, writeability, and read-stability failure rates for a 28nm 6T SRAM bitcell.

#### 3.3 Dynamic Failure Metrics Test Chip

While our estimates of the BER based on importance sampling are interesting, for them to be truly useful, we would like to verify the results in an actual silicon design. In addition, we also need to find the connection of assumptions used to calculate the BER, such as bitline capacitance and timing, with an actual SRAM design. Last, we would like to calculate accurate energy measurements, which requires an actual baseline SRAM design. For these reasons, we describe two baseline arrays, designed in bulk 28nm, and taped out in May 2011.

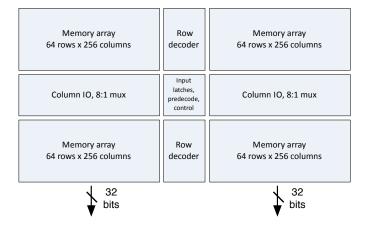

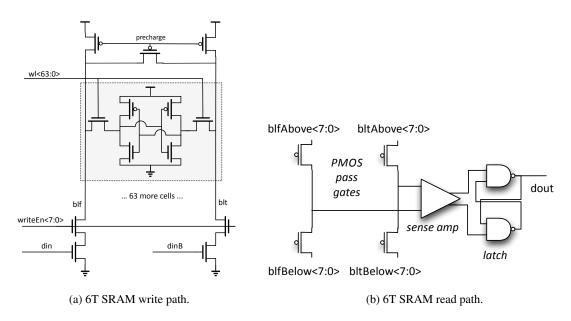

## 3.3.1 6T

The floorplan of our full array implementation is shown in Figure 13. It is formed by combining 4 subarrays of Figure 4 to form an 8kB memory. Based on the address, the predecoder and decoder will turn on the wordline of an entire row (including both the left and right sub-arrays connected to the decoder) to access 512 columns. The column IO performs 8 to 1 interleaving to read or write a 64 bit word. Note that the effective size of the array is 128 rows by 512 columns, yet both the wordline and bitline are split in half in this simple hierarchical implementation to reduce series resistance on the wordline, and to cut bitline capacitance in half.

Timing is controlled by the positive and negative edge of the clock. The positive edge of the clock turns on the wordline, and turns off precharge. The negative edge of the clock turns off the wordline, turns on the sense amplifier, and turns on precharge. All data is registered for the entire cycle, with the exception of

the address input, which is latched with a small transparent window before the clock edge so that addresses have time to propagate through the decoder.

Figure 13: Physical organization of our 6T SRAM.

The write path is shown in Figure 14a. writeEn selects the column to write and can be turned off by a write mask. Depending on the data, a single column is pulled down while the other remains high. An active wordline writes the cell.

Figure 14: 6T periphery circuitry for read and write operations.

The read path is shown in Figure 14b. Eight columns from above and eight columns from below are muxed together to a single shared node for both the true bitline and the complement bitline. Only PMOS pass gates are needed, as the sense amplifier compares values near Vdd. A StrongARM sense-amplifier reads the data, and stores it in a SR' latch. The sense amplifier differential pair uses non-minimum length transistors to reduce offset. All column IO must be bit pitch-matched in groups of eight columns.

## 3.3.2 8T

The floorplan of our 8T full array implementation is shown in Figure 15. Because the size of the cell is double that of the high-density cell, our wordlines can only have half the total number of cells before the series resistance becomes too large. Additionally, because this array is a two-port design, we need separate read and write decoders. Because each row now needs two wordline drivers, lack of space for wiring requires that the read and write row decoders drive the wordline from opposite ends of the array, so the wordline cannot be split in half and the size of the sub-array is 2kB.

| Read<br>row<br>decoder                     | Memory array<br>64 rows x 128 columns | Write<br>row<br>decoder                    |

|--------------------------------------------|---------------------------------------|--------------------------------------------|

| Input<br>latches,<br>predecode,<br>control | Column IO, 2:1 mux                    | Input<br>latches,<br>predecode,<br>control |

| Read<br>row<br>decoder                     | Memory array<br>64 rows x 128 columns | Write<br>row<br>decoder                    |

|                                            | 64<br>bits                            |                                            |

Figure 15: Physical organization of our 8T SRAM.

The write path is shown in Figure 16a. Writing is performed through blt and blf in the same manner as the 6T. An additional read bitline (blr) creates the separate read port.

The read path is shown in Figure 16b. Two columns from above and two columns from below (blrAbove and blrBelow are muxed together to a single shared read node. Before the read operation, the precharge signal (pre) precharges both the read bitline and the shared read node to Vdd. Transmission gates need to be used to ensure the domino-style read inverter can fully transition.

Figure 16: 8T periphery circuitry for read and write operations.

## 4 SRAM Vmin Analysis

Using importance sampling and simulation of an extracted baseline array, we can determine how a large variety of design decisions and techniques affect BER and Vmin. Each technique will be analyzed independently. In reality, more than one technique will be implemented and there will be an interaction between each that cannot be accurately predicted by independent studies. Instead, we hope to generate intuition about the sensitivity of BER to various techniques.

### 4.1 Effect of bitline capacitance on 6T SRAM failures

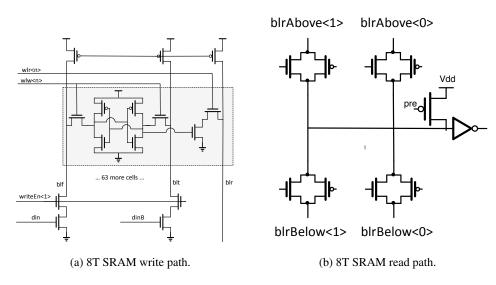

Figure 17 shows how different bitline capacitances (due to different number of rows) affects each mode of failure.

Figure 17: Effect of bitline capacitance on failure rates.

Bitline capacitance has no effect on writeability because writing is done through a bitline forced to ground, and the bitline floating high loses very little charge. Simulations with a floating bitline confirm this observation. Read stability is improved a little for bitlines with smaller capacitance because the dangerous internal node bump on the side holding a 0 decreases over time. However the high bitline loses charge slowly so this only has a minor effect on stability.

Smaller bitline capacitances drastically improve readability. Reads require a certain amount of charge to be removed from the bitline on the side reading a 0. The cell will always pull a constant current, but bitlines with more capacitance will need more charge removed to produce the same voltage differential as a bitline with less capacitance. Readability appears to be the dominant mode of failure unless the bitline capacitance is very small. As shown in Figure 17, the BER of readability and writeability for a target of  $10^{-9}$  will be equal for a bitline capacitance of 15fF.

This finding suggests that creating a small number of rows (short columns) is critical to improving low-

voltage operation of SRAMs. However, this increases area overhead, because column and control circuity can be amortized over less cells.

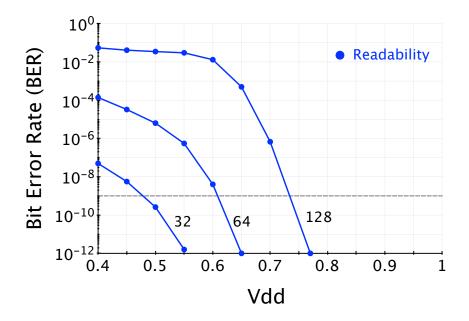

#### 4.2 Effect of bitline capacitance on 8T SRAM failures

For an 8T SRAM, there are two different bitline capacitances–the write bitline (equivalent to the bitlines in the 6T array) and the read bitline. For the write bitline, the effect of capacitance for read stability and writeability will be exactly the same as for the 6T case, even though absolute results will differ a little due to different cell sizing. Read stability failures will only occur for arrays with interleaving.

Figure 18 shows how different read bitline capacitances effect single-ended readability. In this case, a domino read is required, so a pass metric requires an 80% transition past the buffer. The read bitline has slightly higher capacitance than the 6T case, because the pass gate for the read port is larger, however there is less wiring capacitance because the wires can be spaced further apart. In comparison to the 6T, the dedicated read port of the 8T enables a Vmin decrease of around 100mV for a domino read. If single-ended sensing is used, Vmin can decrease even further as bitline discharge requirement is lowered.

Figure 18: Effect of read bitline capacitance on 8T readability failure rates.

#### 4.3 Effect of clock period on 6T SRAM failures

The SRAM arrays under analysis are assumed to be synchronous memories that must return one read or one write during a single clock period. For failure analysis, the wordline is assumed to be on for half of the nominal clock period (and the other half assumed to be used for precharge and margins).

Figure 19 shows failure rates for SRAMs with clock frequencies ranging from 250Mhz (4e-9) to 2Ghz (5e-10).

Figure 19: Effect of clock period on failure rates.

Both readability and writeability improve with longer clock periods because more time is allowed to discharge a bitline (read) or flip a cell (write). Read stability worsens with longer clock periods, as more time is given to accidentally flip the cell, but for this cell/technology, its failure rate is dominated by the other modes of failure so should be ignored for design decisions.

Most importantly, note the large discrepancy of Vmin in this figure between traditional metrics and our methodology's read stability. At 2Ghz, Vmin for read stability is about 450mV, while a static test would predict a Vmin of 650mV. Furthermore, if we fit a Gaussian distribution to the SNM instead of using importance sampling, we would predict a Vmin of 800mV. Designing using pessimistic metrics such as SNM and distribution approximations results in a drastic overdesign of the bitcell for stability.

Notice that readability is much more sensitive to the nominal period than writeability. After a write, a bitline needs to be charged from 0 to Vdd while after a read, a bitline only needs to be charged from Vdd-Vread to Vdd (for example, 150mV). Therefore it would make sense to turn on the wordline for longer during a read cycle, as less time is needed for precharge, and readability will be dramatically improved.

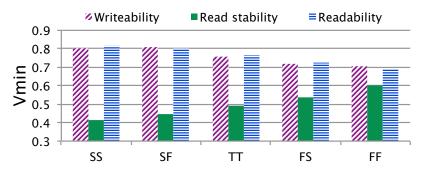

## 4.4 Effect of process corners

So far we have been studying inter-device variation, as these variations introduce strong mismatches between devices within an SRAM cell and can increase the probability of failure. But due to variability in processing, there can also be variation that affects each type of device on the die uniformly. This variability would correspond to shifting the mean of the thresholds of NMOS devices by an amount and PMOS devices by another amount. For example, SF represents NMOS devices which are on average slower by 3  $\sigma$  and PMOS devices that are faster by 3  $\sigma$ . By changing the average behavior of a device, we also change the BER of reads and writes.

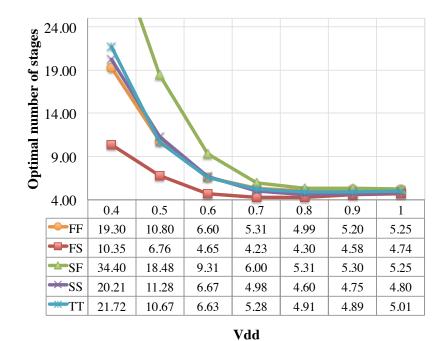

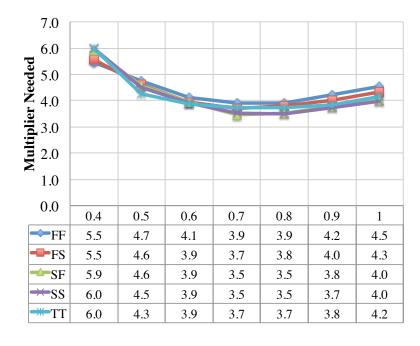

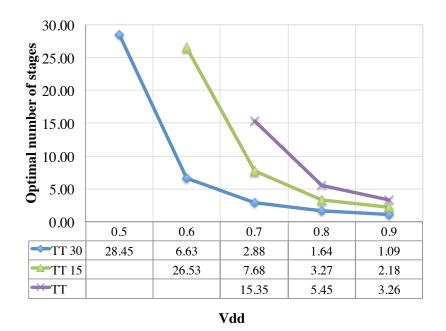

The Vmin of the high-density cell for different process corners is summarized in Figure 20.

Figure 20: Effect of process corners on BER.

There are a few interesting observations that can be made from these plots. As a primary effect, faster NMOS reduce BER for a given supply for both readability and writeability. For readability, this makes sense as faster PD and PG improve the speed at which charge can be pulled off of the bitline. For writeability, the PG becomes stronger than the PU which makes it easier to change the internal node of a cell.

As a secondary effect, faster PMOS also reduce BER for both readability and writeability. For writeability writeability, faster PMOS helps because it becomes easier for the write to complete. For readability, a better PMOS holds the half of the cell holding a 1 high better, so that the bitline connected to the half holding a 0 needs to be less discharged for the same bitline differential to be established.

Faster NMOS hurts stability, because a voltage bump on the side holding a 0 turns on the pull-down for the side holding a 1. A stronger device is more likely to pull this node down and flip the cell. Additionally, stronger PMOS hurts stability as well because a strong PMOS is needed to pull the 0 node high to complete the stability upset.

## 4.5 Effect of sense amplifier offset on readability failure

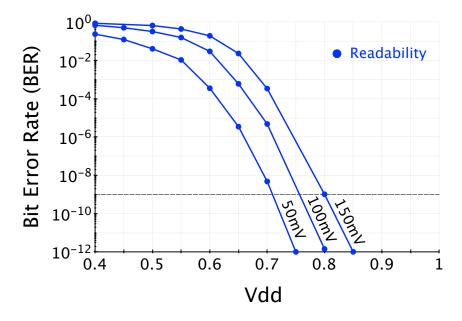

Two main components determine readability—the read current that discharges the bitline, and the sense amplifier offset that measures this discharge. Figure 21 shows how different sense amplifier offsets affect readability. Larger sense amplifiers improve matching in the differential pair and can lower the offset, enabling a significant Vmin reduction.

## 4.6 Effect of assist techniques on 6T SRAM failures

Up until this point, we have analyzed how array organization (eg. clock period, bitline capacitance, etc) affects failure rate. Circuit techniques known as assist techniques can be used on cycle-by-cycle basis to improve Vmin. A comprehensive analysis of the effectiveness of assist techniques was performed in [6], but static metrics were used to quantify effectiveness, which have been shown to be a poor match to silicon failures [10].

For the investigation of each assist technique in this section, the following assumptions were made:

- Corner: TT

- Design: 28nm High-Density 6T Cell

- Voltage: 1V

Figure 21: Effect of sense amplifier offset on readability.

- Period: 50 FO4 ( $\approx$  1ns at 1V)

- Wordline Pulse Period: 25FO4

- Sense-amplifier offset at  $3\sigma$ : 0.1V

- Bitline capacitance: 15fF (128 cells)

The effect of changing all of the above assumptions have been investigated in earlier sections. Note that the period increases with the FO4 as the supply is reduced to track the assumption that the SRAM operating frequency will be set by the critical path of a processor.

Different degrees of assist are defined as a proportion of the supply voltage (and not an absolute quantity) because assist voltages are generally set with voltage dividers or charge redistribution. However, stronger assists are needed at lower voltages, so routing a constant supply could improve assists at low voltage for less capacitor area.

Also to determine the side effects of each assist technique, the following assumptions were made about SRAM layout. The reason for these assumptions can be seen in the cell layout in Figure 4.

- Vdd runs vertically (parallel with bitlines)

- Gnd runs horizontally (parallel with wordlines), and is shared between two adjacent cells

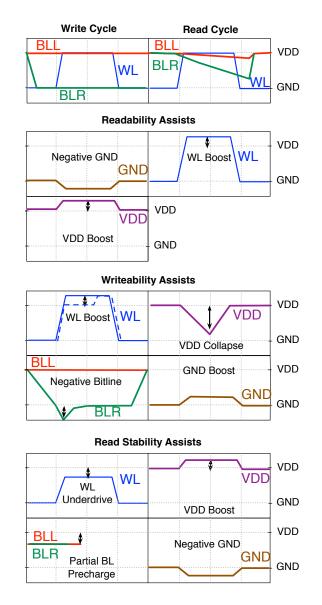

The voltage waveforms for a variety of assist techniques that target each mode of failure—readability, writeability, and read stability—are summarized in Figure 22.

Figure 22: Summary of assist techniques: Negative GND, GND boost, WL boost, WL underdrive, Vdd boost, Vdd collapse, negative bitline, partial bitline precharge.

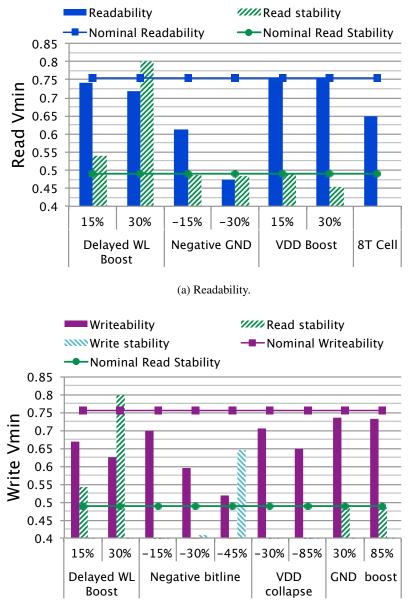

We have completed a thorough design-space exploration of popular or effective assist techniques. Our results are summarized in Figure 23 for readability and writeability assists, and explanations of each method are described in the following subsections. For our technology/cell, stability assists were rare enough to not warrant investigation. Each Vmin measure also includes any stability consequences caused by the assist. Overall Vmin will be determined by the maximum of Vmin for writeability and Vmin for readability. Because all assists can be applied on a per-operation basis, our results for Vmin are independent.

(b) Writeability.

Figure 23: Impact of assist techniques on Vmin.

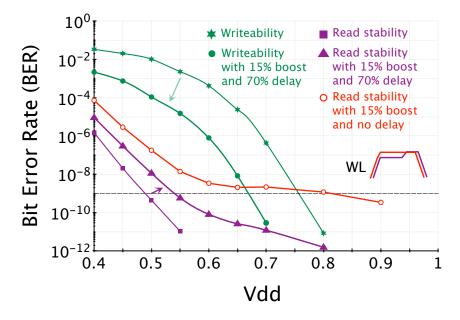

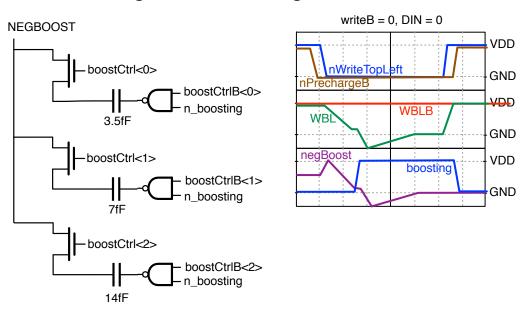

### 4.6.1 Effect of wordline boost as a readability and writeability assist

Using a wordline boost can improve both the readability and writeability of cells, but if an array is interleaved, it will diminish the read stability of all half-selected cells, as shown in Figure 24. To avoid the half-select issue, [4] starts the boost part of the way through the wordline pulse, so that half-selected cells have already begun to read and the bitline voltage matches the internal voltage more closely. Figure 24 shows that while this helps, the trade-off between writeability and read stability remains very sensitive for wordline boosting. Adaptive circuitry must be used in order to tune this circuitry, as done in [5].

Figure 24: Wordline boost improves writeability while reducing read stability.

- **Operation**: During reads or writes, use of a larger wordline voltage to drive the access transistors along a single row.

- **Implementation**: One possible implementation is to use a separate supply for the wordline buffers, but this requires an extra supply, and up-sizing the buffers to maintain the same wordline buffer strength. Also, all off-row drivers will have a non-zero Vsg, causing short circuit current. Full level-shifting circuits are required to avoid this, but will increase the cycle time of the SRAM.

To avoid a second supply, capacitive boost can be used on the Vdd node of the row drivers. This capacitor can be shared with multiple rows, yet the more rows it is shared between, the more parasitic source capacitance needs to be moved for the same boost—increasing the size requirement of the boost capacitor.

- **Pros**: The overdrive is increased on the pass-gates, making both stronger than the pull-ups and therefore improving the writeability of the cell. Both the pass-gate and pull-down need to be strong to improve readability. Since the pass-gate is smaller than the pull-down, a weak pass-gate is much more likely to limit readability. Therefore assists that improve the pass-gate (such as wordline boost), are more effective than assists that improve the pull-down (such as Vdd boost).

- **Cons**: As this assist is applied to a row, all other non-accessed cells on the same row will be reading, and a stronger PG will hurt the ratio between the PG and PD and diminish read stability.

This assist can be very dangerous once we account for the effect of corners, as read stability is very sensitive to changes in wordline boost. As seen in Figure 24, any wordline boost larger than 15% will push the read stability BER above the  $10^{-9}$  limit. The FF corner increases failure rate by more than 3 orders of magnitude over the TT corner. Applying even a 15% boost to help the TT case will break all FF cases. Therefore some adaptive scheme that can determine read stability failure rates is needed to tune the boost. Other assists can avoid this problem by targeting a single mode of failure without affecting other modes, and would not need a complicated control loop.

• **Overhead**: An energy overhead will be caused by a larger voltage on the wordline capacitance, the overhead needed to implement the boost (either flying capacitors charging parasitic source nodes or an additional supply), and the extra discharge caused by improved reads on half-selected columns.

## 4.6.2 Effect of wordline droop as a read stability assist

Activating the wordline with a voltage less than nominal ( $V_{WL} < V_{DD}$ ) can improve the read stability of a cell by decreasing the strength of the PG, but will dramatically worsen readability and writeability. For this cell/technology, this technique is not needed and will not be analyzed further, but it could potentially be used for cells that were skewed to be unstable or in combination with other assist techniques. For example, using negative bitline will counteract the wordline droop's effect on the pass-gate to keep writeability for accessed cells the same, but will increase stability on half-select columns.

#### 4.6.3 Effect of cell Vdd boost as a readability and read stability assist

Increasing a cell's Vdd voltage should improve both readability and read stability by increasing the strength of the pull-down transistor. Vdd boost helps read stability a lot, but does not appear to help readability. Readability failures occur most often if the pull-down device is weak or if the pass-gate is weak. However, if we use Vdd boost, the pull-down devices are always strong, and failures will occur only if the pass-gate is weak. So as a very approximate explanation, only half of the failure conditions are now avoided, so the BER changes by less than a factor of 2 compared to other assist techniques that generally change by orders of magnitude.

This suggests that cell sizing will affect the results of this study. If the pass-gate was made stronger, then Vdd boost would actually improve readability because the pass-gate is no longer constraining the results.

#### 4.6.4 Effect of cell Vdd collapse as a writeability assist

Vdd collapse decreases write Vmin by decreasing the strength of the cross-coupled inverters, but not as much as expected from [5]. Since we analyze a bulk (not tri-gate) device with different sizing characteristics, differing results can be expected.

The dangerous consequence of Vdd collapse is potential violation of the data retention voltage of accessed SRAMs in the same column. However, our IS tests of this condition show a BER  $< 10^{-9}$  for all cases of interests. [5] also found negligible errors for reasonably short access times.

#### 4.6.5 Effect of cell GND boost as a writeability assist

GND boost weakens the cross-coupled inverters, improving writeability [13]. However, the effect of a large GND boost saturates after 30%, because the NMOS PG must pull the low internal node high for this assist to work, but can only pull up to around Vdd-Vth. This limitation does not exist for Vdd collapse, as NMOS can pass low voltages without limitation. So while Vdd collapse and GND boost both weaken the cross-coupled pair, the limitations imposed by the PG make Vdd collapse more effective.

## 4.6.6 Effect of negative bitline as a writeability assist

Negative bitline improves writeability by increasing the Vgs on the PG [3]. Our IS simulation uses a flying capacitor as opposed to a negative regulated voltage to accurately match typical implementations. However, by decreasing one of the bitlines below GND, a non-zero Vgs will appear across the PG of non-accessed rows. If the internal node of an non-accessed bitcell on this side is high, then the value of the cell could flip, causing a write stability error. We generated an IS test to determine the probability of this occurrence and found that the BER was  $< 10^{-9}$  for boost amounts <= 30%. As this assist is applied only during writes to only the columns being written, it does not affect readability or read stability.

- **Operation**: During writes only, a negative voltage is applied to the bitline which is writing a false value while the wordline is high.

- **Implementation**: In general, the negative voltage is usually generated by charging a capacitor, then connecting it to the bitline with a flipped polarity. The degree of assist (how negative the bitline goes) can be controlled at design-time by changing the capacitor size, and at run-time by pre-discharging the capacitor before connecting it to the bitline.

- **Pros**: The overdrive is increased on PG, making it stronger than PU and therefore improving the writeability of the cell for more negative bitline voltages.

- **Cons**: Write stability of cells on the same column is diminished because a negative bitline causes a small overdrive on all other PG on the same column which are supposed to remain off. If the PG has a low-enough threshold, the cell could be accidentally written. But for this cell/technology, importance sampling analysis determined it was not a problem.

- Overhead: Energy overhead is minimal due to only a slightly large change in bitline voltage.

## 4.6.7 Effect of partial bitline precharge as a stability assist

Precharging bitlines to around 70% of Vdd with a regulator has been shown to improve yield from 5 to 5.7  $\sigma$ , or equivalently, from a BER of 2.87e-7 to 6e-9 [2]. Importance-sampling analysis of read stability confirmed their results, with a BER improvement of around 1.5 orders of magnitude at 0.7V. But the assist becomes less helpful at low supplies and only achieves a Vmin reduction of 25mV. While this technique causes less of a bump on the side holding a 0, the opposite side pass-gate is less helpful in holding that node at 0 which offsets part of the advantage. Note that readability is slightly diminished due to the decreased Vds on the PG.

### 4.6.8 Effect of negative cell GND as a readability assist

Reducing the voltage of GND has been shown to improve readability. [3]. Negative GND is the most effective of all readability-assist techniques as it increases the Vgs on both the PD and PG by pulling the internal node holding 0 below ground.

Unfortunately, this technique has a very high energy cost for 6T arrays, because each cell has two GND wires running horizontally, and the GND wire is coupled into the internal node of non-accessed cells. Also, all read current will flow through the GND wire, so a charge pump used to generate a negative voltage will need to sink all current flowing off of the bitlines. For 8T arrays, the GND wire is routed vertically and

many of these problems are somewhat reduced. Cells on rows above and below will have different GND voltages for either side and could cause a stability issue, yet simulation showed BER lower than  $10^{-9}$  for all relevant configurations.

- **Operation**: During reads, the GND of an entire row of cells is pulled below ground. A negative GND increases the  $V_{GS}$  on the PD devices, and also pulls the low node below ground as well, which increases the  $V_{GS}$  on the PG as well. These two transistors are responsible for discharging a bitline capacitance as fast as possible, so their increased strength improves readability.

- **Implementation**: A charge pump can be used to generate a negative voltage in the same manner as the negative bitline assist.

- **Pros**: Vdd boost was shown to not help readability because it only strengths the PD but not the PG, and either device can cause failure if it is weak. Negative GND helps both devices.

- **Cons**: One internal node in each cell is coupled to the GND wire through the pull-down device on the side holding a 0. Therefore, moving GND requires moving all internal nodes along an entire row. Also, each cell uses two separate horizontal ground lines (see Figure 4), both lines need to be made negative, and this disturbs all cells above and below the target row. For the side of the cell holding a 1, the PD device has 0 at its gate. But the source of PD will get pulled below ground, accidentally turning on the pull-down device and possibly flipping the contents of the cell (because the PD device is much stronger than the PU device). But this has been simulated and even with the maximum degree of assist, the BER is less than 10<sup>-15</sup> at all supplies, so for this cell/technology, it is not a major concern.

- **Overhead**: In addition to the large capacitance of the GND wire, any read assist will have a large energy overhead because the assist will have a strong effect on how much a cell discharges a bitline during a read cycle.

The overhead will be increased by both the voltage change on GND, and the extra discharge caused by improved reads on half-selected columns. Note that the capacitance of the GND wire will be similar to the wordline, as the wire length is the same, and GND is connected to two gates.

Note that negative GND slightly improves read stability Vmin. To understand why negative GND does not change the active row read stability, consider a situation where BLLI is logical 1 and BLRI is logical 0. Three components are needed for a cell to flip: PGR must be strong and PDR must be weak to pull BLRI high, and PDL must be strong to pull BLLI low to compete the stability upset. A negative GND boost increases the Vgs on PDR, strengthening this device and helping to prevent flips, however it will also increase the Vgs on PDL, which will help cause flips, and these effects cancel.

## 4.6.9 Effect of other assist techniques

We have only discussed assist techniques that are effective, or assist techniques published in literature which appear to not be as effective as predicted. Assists that change the body voltage were ineffective due to the low body-effect coefficient in this technology. New technologies such as FDSOI would allow a resurgence of body biasing, however substrates generally have a large capacitance so body techniques would be better used to offset process variations than to optimize cycle-by-cycle for read or write operations as other assists do.

There are also many potential combinations of assists. For example, during a write, the wordline can be drooped to improve stability of half-selected cells while negative bitline can be used on only the columns

being written to undo the effect of the wordline droop for cells that actually need to be written. Also, these effects can be used in combination with cell sizing. For example, the PD device can be made smaller to save area, and negative GND can be used to overcome this weakness during read operations. The analysis

## 4.7 Effect of assist techniques on 8T SRAMs

8T bitcells have the same writeability assists as 6T bitcells. If 8T cells are interleaved, half-select during write operations will cause read stress on half-selected cells, producing the same read stability trade-offs as the 6T cell. Readability assists are generally no longer needed, due to the much-improved read path. Figure 23a compares readability of the reference 6T array and bitcell to a domino-style read for an 8T cell with the same number of bitcells on a column.

methodology explained above can be used to quantify the result of any design decision on failure rates.

Because cell sizing and array layout is different for 8T arrays, results differ in a few cases. Note that for an 8T array, GND runs along a column and is shared with all three pull-down devices, so unlike the 6T case, only one GND wire needs to be pulled negative instead of two. In our cell, the read stack shares GND with the pull-down devices, but there is wiring room for these to be split into two wires to reduce the capacitive load of a negative ground assist. However, by keeping both GND connected to the same negative voltage, the RPD for cells holding low on the read side will maintain a  $V_{GS} = 0$  as intended. If the GND wire was split, the RPD will have a nonzero  $V_{GS}$  in this case and the wrong value will be read.

## 4.7.1 Leakage

Our technology is a low-power process, so leakage was negligible even for a worst-case column of 512 cells. However, leakage can easily be taken into account by this methodology by using Monte Carlo to characterize the leakage current of N worst case cells as a Gaussian, and including it into IS as an additional variable described by the fit distribution.

### 4.8 Effect of hierarchical bitlines

Hierarchical bitlines improve cell operation and energy-efficiency while increasing area overhead. Because the devices that couple local to global bitlines can be made larger, variability will have little effect, and analysis of the effect of hierarchical bitlines on failure and energy can be made within the existing infrastructure just by decreasing the number of cells on each row and column to their respective local sizes. Then by multiplying these results by appropriate factor, we can compare a hierarchical design to a non-hierarchical one. However, the main consequence of hierarchical bitlines is area, and this is heavily dependent on layout design rules for a specific process, so a general observation on their effectiveness is difficult.

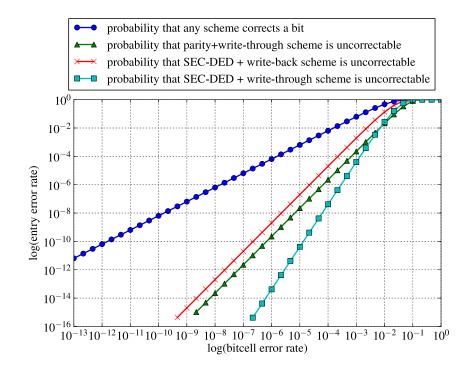

## 4.9 Effect of ECC

Error-correcting codes (ECC) are commonly used in memories to prevent bit failures from causing system failures. Different ECC schemes are commonly characterized by both the number of bits errors per word that they can correct and the number of bit errors that they can detect. So far, all analysis has focused on biterror rate (BER). However, the system using an SRAM array (and possibly ECC) only cares about codeword error rate (CWER)–the probability that an entire group of bits has a certain error rate.

The probability that a n-bit codeword without ECC fails when each bit has an error probability e is given by

Equation 7:

$$p_{fail} = 1 - (1 - e)^k \tag{7}$$

So the probability of failure is one minus the probability that all bits are correct.

A common ECC scheme known as a Hamming code can correct a single error. The probability that a n-bit Hamming covered codeword fails is given by Equation 8:

$$p_{fail} = 1 - \left[ (1-e)^k + \binom{n}{1} * e * (1-e)^{n-1} \right]$$

(8)

Now there are two different conditions for success. The first condition is 0 errors, and this is represented by the first term. The second condition is 1 error, and a combination is used because it doesn't matter which bit it is (in this case, there are n different ways one bit can be wrong).

This equation can be extended for more any number of errors by adding more terms. The probability of failure with ECC that can correct K errors is given by Equation 9.

$$p_{fail} = 1 - \left[\sum_{k=0}^{K} \binom{n}{k} * e^k * (1-e)^{n-k}\right]$$

(9)

In this section, we explore the relationship between bit error probability, operation error probability, and Vmin for different detection/correction schemes inside of a hypothetical cache system. In particular, the two schemes we investigate are (74,64) SEC-DED and (9,8) parity. We chose these two schemes because they are area neutral—they both require the same number of checkbits—for protection of a 64 bit word.

#### 4.9.1 (9,8) Parity Detection

This common detection scheme XORs eight bits to generate a parity bit. Eight sets of these groups covers a 64 bit word. During a read, the bits are XORed again, then compared to this parity bit. If they are different, then the scheme has detected an error. We use an RTL implementation that produces one parity bit for every 8 bits. Synthesis in 28nm LVT process produces the following result:

| Encoding delay:                | 8.0 FO4             |

|--------------------------------|---------------------|

| Decoding detection delay:      | 12.1 FO4            |

| Decoding correciton delay:     | L2 latency          |

| Encoding energy/op:            | 0.07 pJ/op @ 1V     |

| Decoding (no error) energy/op: | 0.186 pJ/op @ 1V    |

| Decoding (error) energy/op:    | allocation cost     |

| Checkbit overhead:             | (8/64) = 12.5%      |

| Encoding Gates                 | 8x 9-input XOR gate |

| Decoding Gates                 | 8x 9-input XOR gate |

Table 1: 8x(9,8) parity characterization in 28nm.

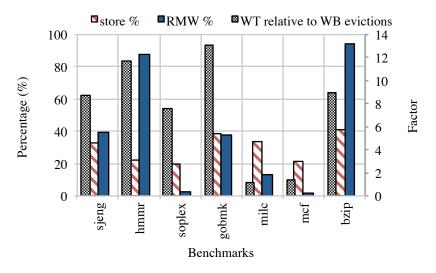

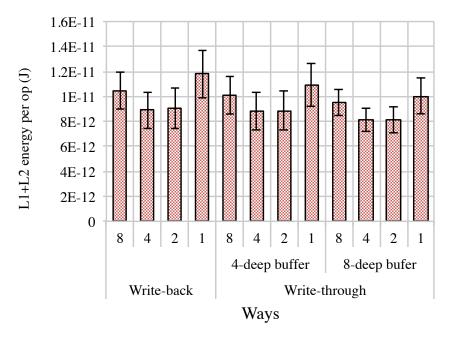

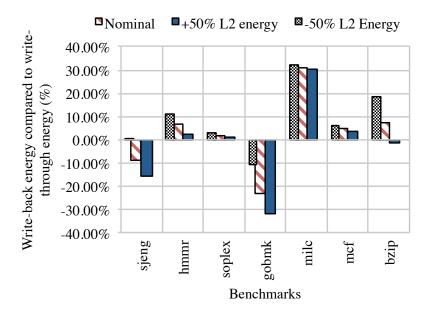

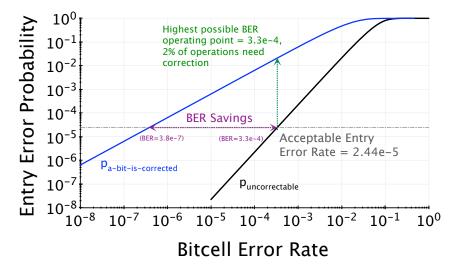

The probability that a bit needs correction and a bit error is uncorrectable is shown below for different bitcell error rates, and is plotted in Figure 25.