# Torrent Architecture Manual

Krste Asanović David Johnson

TR-96-056

December 1996

# Abstract

This manual contains the specification of the Torrent Instruction Set Architecture (ISA). Torrent is a vector ISA designed for digital signal processing applications. Torrent is based on the 32-bit MIPS-II ISA, and this manual is intended to be read as a supplement to the book "MIPS RISC Architecture" by Kane and Heinrich. Torrent is the ISA of the T0 vector microprocessor which is described in the separate "T0 Engineering Data" technical report.

# 1 Introduction

Torrent is a vector processor instruction set architecture (ISA) designed for digital signal processing applications. The Torrent ISA allows for a range of implementations performing differing numbers of operations per clock cycle, depending on available technology.

Torrent is based on the 32 bit MIPS-II ISA. The scalar unit is MIPS-compliant, with coprocessor instruction extensions for the vector unit. This manual is intended to be read as a supplement to the book "MIPS RISC Architecture" by Kane and Heinrich.

To date, the only implementation of Torrent is T0. T0 is described in detail in the "T0 Engineering Data" document.

# 2 CPU

The Torrent CPU runs the MIPS-II standard ISA. Future Torrent implementations may adopt further extensions to the MIPS ISA standard.

The MIPS-II SYNC instruction forces all previous memory operations to complete before allowing further memory operations. SYNC instructions may be required on some Torrent implementations to synchronize memory references between the vector and scalar processors, or between separate vector memory pipelines.

# 3 System Control Coprocessor (CP0)

The system control coprocessor is the standard location for registers dealing with memory management and exception handling. The contents of CP0 are implementation dependent.

# 4 Floating Point Coprocessor (CP1)

Torrent employs the standard MIPS floating point coprocessor instruction set. If an implementation does not provide hardware floating point, these instructions cause a trap to software emulation.

# 5 Vector Unit (CP2)

The Torrent vector unit (VU) is implemented as coprocessor 2 for the MIPS CPU.

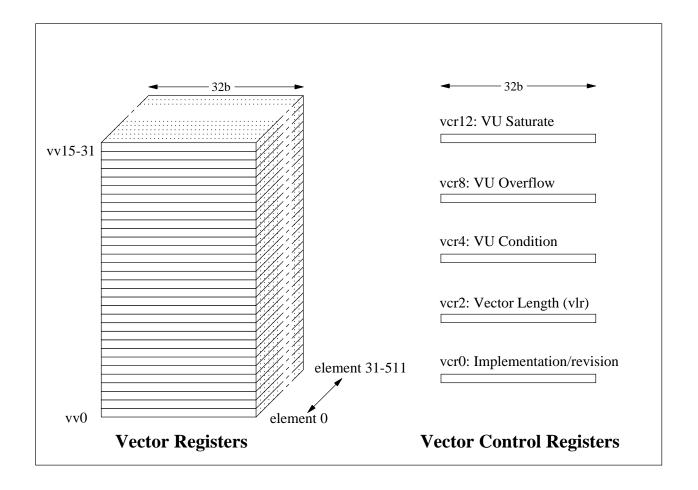

#### Vector registers

Figure 1 shows the registers contained within the vector coprocessor. The VU ISA allows up to 32 vector registers, \$vr0-\$vr31<sup>1</sup>

The first implementation, T0, provides only 16 vector registers, \$vr0-\$vr15. All elements of vector register \$vr0 are defined to hold the constant zero. Writes to \$vr0 are ignored, and reads of \$vr0 return 0.

Each vector element is 32b wide. The first implementation, T0, provides 32 elements per vector. Future implementations may provide longer vectors.

# Control registers

Five VU control registers are defined in the coprocessor control register space. These are accessed using the standard ctc2/cfc2 instructions.

An implementation will typically include additional VU control registers to handle exceptions. These are implementation dependent and will normally only be accessible from kernel mode.

#### VU Instructions

The VU extends the MIPS-II instruction set by adding coprocessor instructions that perform vector operations. The VU is a load/store vector-register architecture. Vector instructions are divided into 2 major groups: vector load/store op-

erations, and vector arithmetic operations. Vector load/store operations move vectors between vector registers and memory, while vector arithmetic instructions operate on vectors in registers.

Each vector register holds a vector of 32b values. A single vector instruction specifies a sequence of operations, and may run for many cycles. The maximum length of a vector is limited by the implementation, but shorter vectors can be specified using the vector length register.

Scalar operands for vector-scalar operations are obtained from the CPU general purpose registers.

There are three varieties of vector load/stores: unit stride, arbitrary stride, and indexed. Unit stride load/stores can specify a post-increment for the scalar address register. Arbitrary stride load/stores transfer elements stored at addresses that form an arithmetic progression. Indexed vector load/stores (gather/scatter) allow indirect memory accesses to be vectorized.

Vector memory operations can transfer bytes, halfwords, and words. Bytes and halfwords are optionally sign-extended to 32b when loaded, and the least significant byte or halfword of a vector element is used for a byte or halfword store.

Vector 32b integer and 32b logical operations are defined. In addition, fixed point instructions are defined to support scaled fixed-point arithmetic. These instructions allow the multiple steps required for a scaled, rounded, fixed-point addition or multiplication to be performed within a single vector instruction.

Conditional vector operations are supported with vector conditional move instructions. A set of vector flag instructions allow a vector condition to be represented as a bit vector that can be read into a scalar register for further processing.

<sup>&</sup>lt;sup>1</sup>The Torrent Architecture extends the MIPS register naming scheme. The vector registers are defined by the assembler as \$vr0-\$vr31, but are usually referred to by the aliases vv0-vv31 in user code.

Figure 1: Vector unit registers.

# 5.1 Vector Unit Control Registers

The vector unit control registers are listed in Table 1.

| Number | Register | Description             |

|--------|----------|-------------------------|

| vcr0   | vrev     | Implementation/revision |

| vcr1   | vcount   | Free running counter    |

| vcr2   | vlr      | Vector length           |

| vcr4   | vcond    | Vector condition flags  |

| vcr8   | vovf     | Vector overflow flags   |

| vcr12  | vsat     | Vector saturation flags |

Table 1: Vector unit control registers.

# 5.1.1 VU Implementation and Revision Number (VCR0)

|   | 31 | 16 | 15 | 8 | 7   | 0 |

|---|----|----|----|---|-----|---|

|   | 0  |    | In | р | Rev |   |

| ۰ | 1  | 6  | 8  |   |     | 8 |

Figure 2: VU Implementation and Revision Register Format

The vrev register is a 32b read only register that contains the implementation and revision number of the VU. These values can be used by configuration and diagnostic software.

The vrev register format is shown in Figure 2. Bits 15–8 define the implementation number, and bits 7–0 define the revision number. The implementation number can be used by user software to detect changes in instruction set or performance. The revision number identifies mask revisions of a given implementation.

Implementation field values are given in Table 2.

| Imp. Number | Vector Unit |

|-------------|-------------|

| 0           | Т0          |

| 1-255       | reserved    |

Table 2: VU Implementation types.

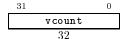

### 5.1.2 Vector Count Register (VCR1)

Figure 3: Vector Count Register Format

The vector count register, vcount, is a 32b read only register formatted as shown in Figure 3.

The value in the vcount register is guaranteed to increase linearly with time, although the rate of increase is unspecified. When it reaches a maximum value of 0xffffffff, the count register will reset to 0 and continue incrementing. Its purpose is to allow relative comparison of small periods of elapsed time for performance analysis.

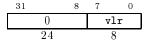

### 5.1.3 Vector Length Register (VCR2)

Figure 4: Vector Length Register Format

The length of a vector operation is specified in an 8b vector length register, vlr. If a vector instruction is issued when the value in vlr is 0, no operation is performed. If a vector instruction is issued when the value in vlr is greater than the implementation's maximum vector length, a vector operation exception is raised. Implementations provide at least 32 elements per vector.

Reads or writes of the vector length register do not affect vector instructions in progress.

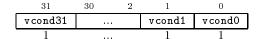

### 5.1.4 VU Condition Register (VCR4)

Figure 5: Vector Condition Register Format

The VU condition register, vcond, is a 32b read/write register formatted as shown in Figure 5.

The vcond register holds the VU condition flags, which reflect the result of the last conditional flag instruction. There is one flag bit corresponding to each vector element, with the least significant bit representing the condition for vector element zero. The register is only altered by conditional flag instructions (set less than, set less than unsigned, set equal) and writes to vcond.

Reads of vcond are interlocked and are guaranteed to return the most recent value. Writes to vcond are not affected by previously issued vector instructions which may still be executing.

Future implementations with greater than 32 elements per vector register may provide additional control registers to hold the extra conditional bits. Future implementations may also add further vcond registers to permit better scheduling of parallel conditional operations.

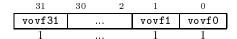

### 5.1.5 VU Overflow Register (VCR8)

Figure 6: Vector Overflow Register Format

The VU overflow register, vovf, is a 32 bit read/write register formatted as shown in Figure 6.

The vovf register holds the VU overflow flags. The overflow flags are sticky bits which are set when any vector arithmetic operation causes an overflow. There is one flag bit corresponding to each vector element, with the least significant bit representing the overflow status for vector element zero. The register is only altered by overflowing arithmetic operations (add, sub) and writes to vovf.

Reads of vovf are interlocked and are guaranteed to return the most recent value. Writes to vovf are not affected by previously issued vector instructions which may still be executing.

Implementations that have greater than 32 elements per vector register have additional overflow registers to hold the extra overflow bits.

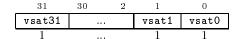

# 5.1.6 VU Saturate Register (VCR12)

Figure 7: Vector Saturate Register Format

The VU saturate register, vsat, is a 32 bit read/write register formatted as shown in Figure 7.

The vsat register holds the VU saturate flags. The saturate flags are sticky bits which are set when any vector arithmetic operation causes a saturated result value. There is one flag bit corresponding to each vector element, with the least significant bit representing the saturation status for vector element zero. The register is only altered by vector fixed-point operations and writes to vsat.

Reads of vsat are interlocked and are guaranteed to return the most recent value. Writes to vsat are not affected by previously issued vector instructions which may still be executing.

Implementations that have greater than 32 elements per vector register have additional saturation registers to hold the extra saturation bits.

#### 5.2 Instruction Overview

#### **VU** Instruction Classes

Instructions affecting the vector unit are divided into several classes:

- Control Register instructions that read and write VU coprocessor control registers.

- Move instructions that move data between vector registers, and between the CPU general registers and the vector registers.

- Load/Store instructions that move vectors of data between vector registers and memory.

- Integer Arithmetic instructions that provide integer arithmetic, shift, logical, compare and conditional operations on vector register contents.

- **Fixed-point** instructions that provide scaled and rounded fixed point arithmetic operations on vector register contents.

#### **VU** Instruction Formats

The VU control register read/write instructions use the standard MIPS coprocessor instruction encodings.

The move, load/store, integer, and fixed-point arithmetic instructions are encoded using the standard MIPS coprocessor operate instruction. These all use the base instruction format shown in Figure 8

The *format* field is encoded as shown in Table 3. The *format* field encodes the class of instruction and also the operand sources, either vector-vector or vector-scalar.

The *opers* field defines the order of operands for non-commutative operations. If *opers* is zero, the

|   | 31  | 26       | $^{25}$ | 21          | 20 16 | 15 11            | 10    | 9 5 | 4 0 |

|---|-----|----------|---------|-------------|-------|------------------|-------|-----|-----|

| ſ | CC  | )P2      | fori    | $_{ m nat}$ | rt/vt | $^{\mathrm{rd}}$ | opers | VW  | vd  |

|   | 010 | 010      | 1x      | xxx         |       |                  |       |     |     |

|   | (   | <u> </u> | Ę       | 5           | 5     | 5                | 1     | 5   | 5   |

Figure 8: Vector unit base instruction format.

|   | Format | Operation type  | Operands      |

|---|--------|-----------------|---------------|

|   | 10000  | Insert/extract  | Vector-Vector |

|   | 10001  | Insert/extract  | Vector-Scalar |

|   | 10010  | Memory          | Vector-Vector |

|   | 10011  | Memory          | Vector-Scalar |

|   | 10100  | Integer/logical | Vector-Vector |

|   | 10101  | Integer/logical | Vector-Scalar |

|   | 10110  | reserved        |               |

|   | 10111  | reserved        |               |

|   | 11000  | Add fixed       | Vector-Vector |

|   | 11001  | Add fixed       | Vector-Scalar |

|   | 11010  | Sub fixed       | Vector-Vector |

|   | 11011  | Sub fixed       | Vector-Scalar |

|   | 11100  | Multiply fixed  | Vector-Vector |

|   | 11101  | Multiply fixed  | Vector-Scalar |

|   | 11110  | reserved        |               |

| L | 11111  | reserved        |               |

Table 3: Format field decoding.

operands are vector/vector or vector/scalar. If opers is one, the operands are scalar/vector.

# 5.3 VU Control Register Instructions

The vector control register instructions move values between the scalar CPU registers and the vector control registers. These operations use the standard MIPS coprocessor control register operations.

These operations are unpredictable if the coprocessor control register field is not one of the valid coprocessor control register numbers as listed in Table 1.

# CFVU Move Control Word From VU

|   | 31  | 26  | 25  | 21       | 20 16 | 15 13 | 1 10 | 0       |

|---|-----|-----|-----|----------|-------|-------|------|---------|

| Γ | СО  | P2  | С   | F        | rt    | cs    |      |         |

|   | 010 | 010 | 000 | 010      |       |       | 0000 | 0000000 |

|   | 6   | i   |     | <u> </u> | 5     | 5     |      | 11      |

#### Format:

CFVU rt, cs

# Description:

The contents of vector unit control register cs are copied into scalar register rt.

This operation is only defined when cs is a valid coprocessor control register.

# Operation:

r[rt] = vcr[cs];

# Exceptions:

Coprocessor unusable exception.

# CTVU Move Control Word To VU

| 31 	 2 | 26 | $^{25}$ | 21  | $20 \ 16$ | 15 11 | 10   | 0        |

|--------|----|---------|-----|-----------|-------|------|----------|

| COP    | 2  | C'      | Τ   | rt        | cs    |      |          |

| 01001  | 0  | 001     | 110 |           |       | 0000 | 00000000 |

| 6      |    | 5       | í   | 5         | 5     |      | 11       |

# Format:

CTVU rt, cs

# Description:

The contents of scalar register rt are copied into vector unit control register cs.

This operation is only defined when cs is a valid coprocessor control register.

# Operation:

# Exceptions:

Coprocessor unusable exception.

### 5.4 Vector Insert/Extract Instructions

The insert and extract instructions are used to form vectors from scalars, or to break vectors down into scalars or smaller vectors.

The extract vector instruction transfers elements from the end of one vector register to the start of another. A scalar register gives a start index into the source register. This instruction can be used to speed reduction operations.

The scalar insert/extract instructions transfer an element between the scalar register file and a vector register. A scalar register gives the index.

The insert/extract instruction encoding is shown in Table 4.

#### VEXT.V Extract Vector To Vector

| 31 	 26 | 25 - 21 | $20 \ 16$ | $15 \ 11$        | 10 | 9 5   | 4 0 |

|---------|---------|-----------|------------------|----|-------|-----|

| COP2    | IXV     | vt        | $^{\mathrm{rd}}$ | VS | EXTV  | vd  |

| 010010  | 10000   |           |                  | 0  | 01011 |     |

| 6       | 5       | 5         | 5                | 1  | 5     | 5   |

# Format:

vext.v vd, vt, rd

# Description:

The vlr register is read to give, n, the number of elements to be moved. Starting from the index in scalar register rd, n elements from vector register vt are copied into the first n elements of vector register vd.

If the lower 8 bits of the sum of vlr and rd are greater than the maximum vector length, a vector operation exception is raised.

# Operation:

# **Exceptions:**

| Format | vw    | Opers | Mnemonic | Description                      |

|--------|-------|-------|----------|----------------------------------|

| 10000  | 01011 | 0     | vext.v   | Extract from vector into vector. |

| 10001  | 10011 | 0     | vins.s   | Insert into vector from scalar.  |

| 10001  | 11011 | 0     | vext.s   | Extract from vector into scalar. |

Table 4: Insert/extract instruction encoding.

#### VINS.S Insert Into Vector From Scalar

| 31 	 26 | 25 	 21 | 20 16      | $15 \ 11$        | 10 | 9 5   | 4 0 |

|---------|---------|------------|------------------|----|-------|-----|

| COP2    | IXS     | $_{ m rt}$ | $^{\mathrm{rd}}$ | VS | INSS  | vd  |

| 010010  | 10001   |            |                  | 0  | 10011 |     |

| 6       | 5       | 5          | 5                | 1  | 5     | 5   |

### Format:

vins.s rt, vd, rd

# Description:

The value of scalar register rt is copied to element rd of vector register vd.

If the lower eight bits of scalar register rd are greater than or equal to the maximum vector length, a vector operation exception is raised.

# Operation:

# **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception.

#### VEXT.S Extract From Vector To Scalar

| 31 	 26 | 25 	 21 | 20 16      | $15 \ 11$        | 10 | 9 5   | 4 0 |

|---------|---------|------------|------------------|----|-------|-----|

| COP2    | IXS     | $_{ m rt}$ | $^{\mathrm{rd}}$ | VS | EXTS  | vd  |

| 010010  | 10001   |            |                  | 0  | 11011 |     |

| 6       | 5       | 5          | 5                | 1  | 5     | 5   |

#### Format:

vext.s rt, vd, rd

# Description:

The value of element rd of vector register vd is copied to scalar register rt.

If the lower 8 bits of scalar register rd are greater than or equal to the maximum vector length, a vector operation exception is raised.

# Operation:

# **Exceptions:**

# 5.5 Vector Load/Store Instructions

Vector loads and stores transfer bytes, halfwords, and words between vector register elements and memory. Bytes and halfwords are sign-extended when loaded into vector elements. Stores always transfer the least significant bits of an element to memory. Addresses for the memory transfers are taken from the scalar registers.

There are three classes of vector loads and stores: unit-stride, arbitrary stride, and vector indexed. The unit-stride operations transfer vectors whose elements are held in contiguous locations in memory. The unit-stride operations allow a post-increment of the base address register. The arbitrary stride operations transfer vectors to or from memory at addresses that form an arithmetic progression. The vector indexed operations transfer vectors whose elements are located at offsets from a base address, with the offsets specified by the contents of an index vector.

Table 5 shows the encoding for vector load/store operations.

| Format | vw    | Opers | Mnemonic          | Description                                                    |

|--------|-------|-------|-------------------|----------------------------------------------------------------|

| 10010  | 0xxxx | 0     | reserved          | •                                                              |

| 10010  | 10000 | 0     | lbx.v             | Load signed byte vector indexed.                               |

| 10010  | 10001 | 0     | lhx.v             | Load signed halfword vector indexed.                           |

| 10010  | 10010 | 0     | reserved          | Ŭ .                                                            |

| 10010  | 10011 | 0     | lwx.v             | Load word vector indexed.                                      |

| 10010  | 10100 | 0     | lbux.v            | Load unsigned byte vector indexed.                             |

| 10010  | 10101 | 0     | lhux.v            | Load unsigned halfword vector indexed.                         |

| 10010  | 1011x | 0     | reserved          |                                                                |

| 10010  | 11000 | 0     | sbx.v             | Store byte vector indexed.                                     |

| 10010  | 11001 | 0     | shx.v             | Store halfword vector indexed.                                 |

| 10010  | 11010 | 0     | reserved          |                                                                |

| 10010  | 11011 | 0     | swx.v             | Store word vector indexed.                                     |

| 10010  | 111xx | 0     | reserved          |                                                                |

| 10011  | 00000 | 0     | lbai.v            | Load unit-stride signed byte vector with auto-increment.       |

| 10011  | 00001 | 0     | lhai.v            | Load unit-stride signed halfword vector with auto-increment.   |

| 10011  | 00010 | 0     | reserved          |                                                                |

| 10011  | 00011 | 0     | lwai.v            | Load unit-stride word vector with auto-increment.              |

| 10011  | 00100 | 0     | lbuai.v           | Load unit-stride unsigned byte vector with auto-increment.     |

| 10011  | 00101 | 0     | lhuai.v           | Load unit-stride unsigned halfword vector with auto-increment. |

| 10011  | 0011x | 0     | reserved          |                                                                |

| 10011  | 01000 | 0     | sbai.v            | Store unit-stride byte vector with auto-increment.             |

| 10011  | 01001 | 0     | shai.v            | Store unit-stride halfword vector with auto-increment.         |

| 10011  | 01010 | 0     | reserved          |                                                                |

| 10011  | 01011 | 0     | swai.v            | Store unit-stride word vector with auto-increment.             |

| 10011  | 011xx | 0     | reserved          |                                                                |

| 10011  | 10000 | 0     | lbst.v            | Load signed byte vector with stride.                           |

| 10011  | 10001 | 0     | lhst.v            | Load signed halfword vector with stride.                       |

| 10011  | 10010 | 0     | reserved          |                                                                |

| 10011  | 10011 | 0     | lwst.v            | Load word vector with stride.                                  |

| 10011  | 10100 | 0     | lbust.v           | Load unsigned byte vector with stride.                         |

| 10011  | 10101 | 0     | lhust.v           | Load unsigned halfword vector with stride.                     |

| 10011  | 1011x | 0     | reserved          |                                                                |

| 10011  | 11000 | 0     | sbst.v            | Store byte vector with stride.                                 |

| 10011  | 11001 | 0     | $\mathrm{shst.v}$ | Store halfword vector with stride.                             |

| 10011  | 11010 | 0     | reserved          |                                                                |

| 10011  | 11011 | 0     | swst.v            | Store word vector with stride.                                 |

| 10011  | 111xx | 0     | reserved          |                                                                |

| 1001x  | XXXXX | 1     | reserved          |                                                                |

Table 5: Vector load/store instruction encoding.

# LxAI.V Load Auto-Increment Vector

####

| 31 | 26    | $^{25}$ | 21  | 20 16 | $15 \ 11$        | 10 | 9   | 5  | 4 0 |   |

|----|-------|---------|-----|-------|------------------|----|-----|----|-----|---|

| С  | OP2   | ME      | MS  | rt    | $^{\mathrm{rd}}$ | VS | LH  | ΑI | vd  | 1 |

| 01 | .0010 | 100     | )11 |       |                  | 0  | 000 | 01 |     |   |

|    | 6     |         | ó   | 5     | 5                | 1  | 5   |    | 5   |   |

| 31  | 26  | 25  | 21  | 20 16 | 15 11            | 10 | 9   | 5  | 4 0 |

|-----|-----|-----|-----|-------|------------------|----|-----|----|-----|

| CC  | P2  | ME  | MS  | rt    | $^{\mathrm{rd}}$ | VS | LW  | AΙ | vd  |

| 010 | 010 | 100 | 011 |       |                  | 0  | 000 | 11 |     |

| (   | j   | Ę   | 5   | 5     | 5                | 1  | 5   |    | 5   |

#### Format:

lbai.v vd, rd, rt lhai.v vd, rd, rt lwai.v vd, rd, rt

# Description:

The vlr register is read to give, n, the number of elements to be loaded. Starting from the base address in scalar register rd, n contiguous elements are loaded from memory, sign-extended to 32b (if necessary), and placed in the first n consecutive elements of the vector register vd. The value of rd is post-incremented by the value of rt. This post-increment is treated as unsigned addition and does not generate an overflow. The result of the instruction is undefined if rd is the same as rt.

A vector address exception occurs if the instruction loads halfwords and the least significant bit of the rd register is non-zero. A vector address exception occurs if the instruction loads words and either of the two least significant bits of the rd register are non-zero. A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

#### Operation:

```

for (i=0; i<vlr; i++)

v[vd][i] = extend(m[r[rd]+i*elsize]);

r[rd] += r[rt];</pre>

```

### **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception. Vector address exception.

# LxUAI.V Load Unsigned Auto-Increment Vector

| 31  | 26  | $^{25}$ | 21       | $20 \ 16$           | $15 \ 11$        | 10 | 9   | 5   | 4 0 |   |

|-----|-----|---------|----------|---------------------|------------------|----|-----|-----|-----|---|

| CO  | P2  | ME      | MS       | $\operatorname{rt}$ | $^{\mathrm{rd}}$ | VS | LBU | JAI | vd  | 1 |

| 010 | 010 | 100     | )11      |                     |                  | 0  | 001 | .00 |     |   |

|     | ;   | ŗ       | <u> </u> | 5                   | 5                | 1  | ŗ   | `   | 5   |   |

| 31  | 26  | $^{25}$ | 21  | $20 \ 16$ | 15 11            | 10 | 9   | 5                                            | 4 0 |

|-----|-----|---------|-----|-----------|------------------|----|-----|----------------------------------------------|-----|

| CC  | P2  | ΜE      | MS  | rt        | $^{\mathrm{rd}}$ | VS | LHU | JAI                                          | vd  |

| 010 | 010 | 100     | )11 |           |                  | 0  | 001 | .01                                          |     |

| (   | j   | Ę       | ó   | 5         | 5                | 1  | C.  | <u>,                                    </u> | 5   |

#### Format:

lbuai.v vd, rd, rt lhuai.v vd, rd, rt

### Description:

The vlr register is read to give, n, the number of elements to be loaded. Starting from the base address in scalar register rd, n contiguous elements are loaded from memory, zero extended to 32b, and placed in the first n consecutive elements of the vector register vd. The value of rd is post-incremented by the value of rt. This post-increment is treated as unsigned addition and does not generate an overflow. The result of the instruction is undefined if rd is the same as rt.

A vector address exception occurs if the instruction loads halfwords and the least significant bit of the rd register is non-zero. A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

# **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception. Vector address exception.

# LxX.V Load Indexed Vector

| 31  | 26  | 25  | 21  | $20 \ 16$ | $15 \ 11$        | 10 | 9   | 5  | 4 0 |

|-----|-----|-----|-----|-----------|------------------|----|-----|----|-----|

| CC  | )P2 | ME  | MV  | vt        | $^{\mathrm{rd}}$ | VS | LB  | X  | vd  |

| 010 | 010 | 100 | 010 |           |                  | 0  | 100 | 00 |     |

| (   | ĵ   | ļ   | 5   | 5         | 5                | 1  | 5   |    | 5   |

| 31  | 26  | 25  | 21  | $20 \ 16$ | $15 \ 11$        | 10 | 9   | 5  | 4 0 |   |

|-----|-----|-----|-----|-----------|------------------|----|-----|----|-----|---|

| CC  | )P2 | ME  | MV  | vt        | $^{\mathrm{rd}}$ | VS | LH  | X  | vd  | 1 |

| 010 | 010 | 100 | 010 |           |                  | 0  | 100 | 01 |     |   |

| (   | ĵ   | ļ   | 5   | 5         | 5                | 1  | 5   |    | 5   |   |

| 31   | 26  | 25  | 21  | 20 16 | 15 11            | 10 | 9   | 5  | 4 0 |   |

|------|-----|-----|-----|-------|------------------|----|-----|----|-----|---|

| СО   | P2  | ME  | MV  | vt    | $^{\mathrm{rd}}$ | VS | LW  | ΥX | vd  | 1 |

| 0100 | 010 | 100 | 010 |       |                  | 0  | 100 | 11 |     |   |

| 6    | j   | ļ   | 5   | 5     | 5                | 1  | 5   |    | 5   |   |

### Format:

lbx.v vd, rd, vt lhx.v vd, rd, vt lwx.v vd, rd, vt

# Description:

This is a gather operation. The vlr register is read to give, n, the number of elements to be loaded. The scalar register rd is read to give the base address. The first n elements of vt are then added to rd to give n effective addresses. The vector of effective addresses is used to load n elements from memory which are then sign-extended to 32b, and placed into the first n elements of vd.

A vector address exception occurs if the instruction loads halfwords and the least significant bit of any effective address is zero. A vector address exception occurs if the instruction loads words and either of the two least significant bits of any effective address are non-zero. A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

#### Operation:

# **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception. Vector address exception.

# LxUX.V Load Unsigned Indexed Vector

| 31  | 26  | 25  | 21  | $20 \ 16$ | $15 \ 11$        | 10 | 9   | 5   | 4 0 |

|-----|-----|-----|-----|-----------|------------------|----|-----|-----|-----|

| CC  | P2  | ME  | MV  | vt        | $^{\mathrm{rd}}$ | VS | LBI | UX  | vd  |

| 010 | 010 | 100 | 010 |           |                  | 0  | 101 | .00 |     |

|     | ì   |     | ī.  | 5         | 5                | 1  | 5   |     | 5   |

|   | 31  | 26  | $^{25}$ | 21  | $20 \ 16$ | 15 11      | 10 | 9   | 5   | 4 0 |

|---|-----|-----|---------|-----|-----------|------------|----|-----|-----|-----|

| ſ | CC  | P2  | ME      | MV  | vt        | $^{ m rd}$ | VS | LH  | UX  | vd  |

|   | 010 | 010 | 100     | 010 |           |            | 0  | 101 | .01 |     |

|   | (   | 3   | ļ       | 5   | 5         | 5          | 1  | CH  | j . | 5   |

#### Format:

lbux.v vd, rd, vt lhux.v vd, rd, vt

#### Description:

This is a gather operation. The vlr register is read to give, n, the number of elements to be loaded. The scalar register rd is read to give the base address. The first n elements of vt are then added to rd to give n effective addresses. The vector of effective addresses is used to load n elements from memory which are zero extended to 32b, and placed into the first n elements of vd.

A vector address exception occurs if the instruction loads halfwords and the least significant bit of any effective address is zero. A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

#### Operation:

```

for (i=0; i<vlr; i++)

v[vd][i] = m[r[rd]+v[vt][i]];</pre>

```

#### **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception. Vector address exception.

LxST.V Load Strided Vector

| 31  | 26  | $^{25}$ | 21                    | $20 \ 16$           | $15 \ 11$        | 10 | 9   | 5   | 4 0 |

|-----|-----|---------|-----------------------|---------------------|------------------|----|-----|-----|-----|

| CC  | )P2 | ME      | $^{\circ}\mathrm{MS}$ | $\operatorname{rt}$ | $^{\mathrm{rd}}$ | VS | LB  | ST  | vd  |

| 010 | 010 | 100     | 011                   |                     |                  | 0  | 100 | 000 |     |

| (   | 6   | į       | 5                     | 5                   | 5                | 1  |     | í   | 5   |

|   | 31  | 26  | 25  | 21  | $20 \ 16$ | 15 11            | 10 | 9   | 5  | 4 0 |

|---|-----|-----|-----|-----|-----------|------------------|----|-----|----|-----|

| Γ | CC  | P2  | ME  | MS  | rt        | $^{\mathrm{rd}}$ | VS | LHS | ST | vd  |

|   | 010 | 010 | 100 | 011 |           |                  | 0  | 100 | 01 |     |

|   | (   | j   | į   | 5   | 5         | 5                | 1  | 5   |    | 5   |

| 31  | 26  | $^{25}$ | 21  | $20 \ 16$ | $15 \ 11$        | 10 | 9   | 5  | 4 0 |

|-----|-----|---------|-----|-----------|------------------|----|-----|----|-----|

| CC  | P2  | ME      | MS  | rt        | $^{\mathrm{rd}}$ | VS | LW  | ST | vd  |

| 010 | 010 | 100     | 011 |           |                  | 0  | 100 | 11 |     |

| (   | ĵ   |         | 5   | 5         | 5                | 1  | 5   |    | 5   |

#### Format:

lbst.v vd, rd, rt lhst.v vd, rd, rt lwst.v vd, rd, rt

### Description:

The vlr register is read to give, n, the number of elements to be loaded. The scalar register rt is read to give the byte stride of the accesses. The first operand is loaded from the address given in rd, sign-extended to the vector element width (if necessary), and placed in the first element of vd. The  $k^{th}$  element of vd is loaded from address

$$rd + rt \times (k-1)$$

A vector address exception occurs if the instruction loads halfwords and the least significant bit of any effective address is non-zero. A vector address exception occurs if the instruction loads words and either of the two least significant bits of any effective address is non-zero. A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

### **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception. Vector address exception.

### LxUST.V Load Unsigned Strided Vector

#### 26 20 16 $^{21}$ 15 11 10 COP2 LBUST MEMS rd $\overline{VS}$ vd rt 010010 10011 0 10100

| 31  | 26  | 25  | 21  | $20 \ 16$  | $15 \ 11$        | 10 | 9   | 5   | 4 0 |

|-----|-----|-----|-----|------------|------------------|----|-----|-----|-----|

| CO  | P2  | ME  | MS  | $_{ m rt}$ | $^{\mathrm{rd}}$ | VS | LHU | JST | vd  |

| 010 | 010 | 100 | 11  |            |                  | 0  | 101 | 101 |     |

| (   | ĵ   |     | j . | 5          | 5                | 1  |     | j . | 5   |

#### Format:

lbust.v vd, rd, rt lhust.v vd, rd, rt

# Description:

The vlr register is read to give, n, the number of elements to be loaded. The scalar register rt is read to give the byte stride of the accesses. The first operand is loaded from the address given in rd, zero extended to the vector element width (if necessary), and placed in the first element of vd. The k<sup>th</sup> element of vd is loaded from address

$$rd + rt \times (k-1)$$

A vector address error exception occurs if the instruction loads halfwords and the least significant bit of any effective address is non-zero. A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

## **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception. Vector address exception.

SxAI.V Store Auto-Increment Vector

| 31  | 26  | $^{25}$ | 21  | $20 \ 16$  | $15 \ 11$        | 10 | 9   | 5                                              | 4 0 |   |

|-----|-----|---------|-----|------------|------------------|----|-----|------------------------------------------------|-----|---|

| CC  | )P2 | ME      | MS  | $_{ m rt}$ | $^{\mathrm{rd}}$ | VS | SB  | ΑI                                             | vd  | 1 |

| 010 | 010 | 100     | 011 |            |                  | 0  | 010 | 000                                            |     |   |

| (   | ĵ   | į       | 5   | 5          | 5                | 1  |     | <u>,                                      </u> | 5   | _ |

| 31  | 26  | $^{25}$ | 21  | $20 \ 16$  | 15 11            | 10 | 9   | 5  | 4 0 |   |

|-----|-----|---------|-----|------------|------------------|----|-----|----|-----|---|

| CC  | )P2 | ME      | MS  | $_{ m rt}$ | $^{\mathrm{rd}}$ | VS | SH  | ΑI | vd  | 1 |

| 010 | 010 | 100     | 011 |            |                  | 0  | 010 | 01 |     |   |

| (   | ŝ   | ļ       | j . | 5          | 5                | 1  | 5   |    | 5   |   |

| 31  | 26  | $^{25}$ | 21  | $20 \ 16$  | $15 \ 11$        | 10 | 9   | 5        | 4 0 |   |

|-----|-----|---------|-----|------------|------------------|----|-----|----------|-----|---|

| CC  | )P2 | ME      | MS  | $_{ m rt}$ | $^{\mathrm{rd}}$ | VS | SW  | ΆΙ       | vd  | 1 |

| 010 | 010 | 100     | 011 |            |                  | 0  | 010 | 11       |     |   |

| (   | 6   | Į       | 5   | 5          | 5                | 1  | 5   | <u> </u> | 5   |   |

#### Format:

sbai.v vd, rd, rt shai.v vd, rd, rt swai.v vd, rd, rt

# Description:

The vlr register is read to give, n, the number of elements to be stored. The first n consecutive elements of the vector register vd are stored in consecutive memory locations starting at the base address in scalar register rd. The rd register is post-incremented by the contents of the rt register. This post-increment is treated as unsigned addition and does not generate an overflow. The result of the instruction is undefined if rd is the same as rt. Implementations do not guarantee the order in which vector elements are written within a single vector store instruction.

A vector address exception occurs if the instruction stores halfwords and the least significant bit of the rd register is non-zero. A vector address exception occurs if the instruction stores words and either of the two least significant bits of the rd register is non-zero. A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

```

for (i=0; i<vlr; i++)

m[r[rd]+i*elsize] = v[vd][i];

r[rd] += r[rt];</pre>

```

# **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception. Vector address exception.

# SxX.V Store Indexed Vector

| 31  | 26  | 25  | 21  | $20 \ 16$ | $15 \ 11$        | 10 | 9   | 5  | 4 0 |   |

|-----|-----|-----|-----|-----------|------------------|----|-----|----|-----|---|

| CC  | )P2 | ME  | MV  | vt        | $^{\mathrm{rd}}$ | VS | SB  | Χ  | vd  | 1 |

| 010 | 010 | 100 | 010 |           |                  | 0  | 110 | 00 |     |   |

|     | ĵ   |     | j i | 5         | 5                | 1  | 5   |    | 5   | _ |

| 31  | 26  | 25  | 21  | $20 \ 16$ | $15 \ 11$        | 10 | 9   | 5  | 4 0 |

|-----|-----|-----|-----|-----------|------------------|----|-----|----|-----|

| CC  | )P2 | ME  | MV  | vt        | $^{\mathrm{rd}}$ | VS | SH  | Χ  | vd  |

| 010 | 010 | 100 | 010 |           |                  | 0  | 110 | 01 |     |

| (   | ĵ   | Į   | 5   | 5         | 5                | 1  | 5   |    | 5   |

| 31  | 26  | 25  | 21  | $20 \ 16$ | $15 \ 11$        | 10 | 9   | 5  | 4 0 |   |

|-----|-----|-----|-----|-----------|------------------|----|-----|----|-----|---|

| CC  | )P2 | ME  | MV  | vt        | $^{\mathrm{rd}}$ | VS | SW  | /X | vd  | 1 |

| 010 | 010 | 100 | 010 |           |                  | 0  | 110 | 11 |     | l |

| (   | ĵ   | ļ   | 5   | 5         | 5                | 1  | 5   | )  | 5   | • |

#### Format:

sbx.v vd, rd, vt shx.v vd, rd, vt swx.v vd, rd, vt

# Description:

This is a scatter operation. The vlr register is read to give, n, the number of elements to be stored. The scalar register rd is read to give the base address. The first n elements of vt are then added to rd to give n effective addresses. The first n elements of vd are written to memory using the vector of effective addresses. Implementations do not guarantee the order in which individual vector elements are written within a single vector store instruction.

A vector address exception occurs if the instruction stores halfwords and the least significant bit any effective address is non-zero. A vector address exception occurs if the instruction stores words and either of the two least significant bits of any effective address is non-zero. A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

```

for (i=0; i<vlr; i++)

m[r[rd]+v[vt][i]] = v[vd][i];</pre>

```

### **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception. Vector address exception.

# SxST.V Store Strided Vector

| 31  | 26  | $^{25}$ | 21  | $20 \ 16$ | $15 \ 11$        | 10 | 9   | 5  | 4 0 |

|-----|-----|---------|-----|-----------|------------------|----|-----|----|-----|

| CC  | )P2 | ME      | MS  | rt        | $^{\mathrm{rd}}$ | VS | SB  | ST | vd  |

| 010 | 010 | 100     | 011 |           |                  | 0  | 110 | 00 |     |

| (   | ĵ   | Į       | 5   | 5         | 5                | 1  | 5   |    | 5   |

| 31  | 26  | $^{25}$ | 21  | $20 \ 16$           | $15 \ 11$        | 10 | 9   | 5  | 4 0 |

|-----|-----|---------|-----|---------------------|------------------|----|-----|----|-----|

| CC  | P2  | ΜE      | MS  | $\operatorname{rt}$ | $^{\mathrm{rd}}$ | VS | SH  | ST | vd  |

| 010 | 010 | 100     | 011 |                     |                  | 0  | 110 | 01 |     |

| (   | j   | Ę       | 5   | 5                   | 5                | 1  | -   | ó  | 5   |

| 31  | 26  | 25  | 21                | 20 16 | 15 11            | 10 | 9   | 5  | 4 0 |

|-----|-----|-----|-------------------|-------|------------------|----|-----|----|-----|

| CO  | P2  | ME  | $^{\mathrm{LMS}}$ | rt    | $^{\mathrm{rd}}$ | VS | SW  | ST | vd  |

| 010 | 010 | 100 | 011               |       |                  | 0  | 110 | 11 |     |

| f   | ì   |     | <u> </u>          | 5     | 5                | 1  | т.  | í  | 5   |

#### Format:

sbst.v vd, rd, rt shst.v vd, rd, rt swst.v vd, rd, rt

# Description:

The vlr register is read to give, n, the number of elements to be stored. The scalar register rt is read to give the byte stride of the accesses. The first element of vd is stored to the address given in the scalar register rd. The  $k^{\text{th}}$  element of vd is stored at address

$$rd + rt \times (k-1)$$

Implementations do not guarantee the order in which vector elements are written within a single vector store instruction.

A vector address exception occurs if the instruction stores halfwords and the least significant bit of any effective address is non-zero. A vector address exception occurs if the instruction stores words and either of the two least significant bits of any effective address is non-zero. A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

#### Operation:

# Exceptions:

Reserved instruction exception.

Coprocessor unusable exception.

Vector operation exception.

Vector address exception.

# 5.6 Vector Integer ALU Operations

All vector integer and logical computational instructions are available in both vector-vector and vector-scalar forms. The rd field is used to encode the integer function.

The vector-vector instructions specify a vector of binary operations, with the first operand taken from vector register vd, the second operand from vector register vt, and the result placed in vector register vw. Vector-scalar instructions specify a vector of binary operations, with the first operand taken from vector register vd, the second operand from scalar register vt, and the result placed in vector register vd.

A few non-commutative operations have scalarvector forms where the first operand is rt and the second operand is vs.

Table 6 shows the encoding of the available integer computational operations.

#### Vector arithmetic and logical instructions

The vector unit implements numerous arithmetic and logical operations, including variable displacement shifts. Signed and unsigned addition and subtraction are provided — the fixed point instructions (see Section 5.7) can be used to perform signed and unsigned 16 bit multiplication.

An overflow status register, vovf, is updated by integer arithmetic operations and can be accessed in coprocessor 2. One "sticky" overflow bit is provided for each vector element. Overflowing operations set these bits, but they can only be cleared by explicit writes to the overflow register.

#### Vector conditional instructions

To compare vectors, there are conditional set instructions "set less than" and "set equal". These instructions produce a vector of boolean results, and in the set less than case the comparison can be signed or unsigned. Both are available in vector-vector and vector-scalar forms, with set less than also having a scalar-vector form.

To compare vectors and produce results for manipulation in the scalar unit, there are "flag less than" and "flag equal" instructions. The vector unit maintains a condition flag register, with one condition bit for each vector register element. This register is updated by the flag instructions, and is accessed as a coprocessor 2 control register. To perform conditional branches on vector operations, this register is copied to a scalar CPU register where any MIPS-II conditional branch can be used. Implementations with greater than 32 elements per vector register provide additional condition flag registers.

The vector unit implements vector conditional moves, in both vector-vector and vector-scalar forms. The first operand is compared against zero; if the comparison succeeds, the destination element is updated with the second operand, otherwise the destination element is unaffected. Note that a scalar-vector form is not required, as a scalar condition can always be replaced with a branch in the CPU.

The conditional moves can be made unconditional if the condition vector register is \$vr0. In this way, scalar register values can be broadcast into a vector register, and vectors of values can be copied between vector registers.

| Format | rd    | Opers | Mnemonic                   | Description                                  |

|--------|-------|-------|----------------------------|----------------------------------------------|

| 1010v  | 00000 | W     | $\mathrm{sub}.yy$          | Subtract signed (flag overflow).             |

| 1010v  | 00001 | W     | $\mathrm{subu}.yy$         | Subtract unsigned (no overflow).             |

| 1010x  | 00010 | X     |                            | reserved                                     |

| 1010x  | 00011 | X     |                            | reserved                                     |

| 1010v  | 00100 | W     | $\mathrm{flt}.yy$          | Flag less than (update condition).           |

| 1010v  | 00101 | W     | ${ m fltu}.yy$             | Flag less than unsigned (update condition).  |

| 1010v  | 00110 | 0     | feq. yy                    | Flag equal (update condition).               |

| 1010x  | 00111 | X     |                            | reserved                                     |

| 1010v  | 01000 | W     | $\mathrm{sllv}.yy$         | Shift left logical variable.                 |

| 1010v  | 01001 | W     | $\mathrm{srlv}.yy$         | Shift right logical variable.                |

| 1010x  | 01010 | X     |                            | reserved                                     |

| 1010v  | 01011 | W     | $\operatorname{srav}.yy$   | Shift right arithmetic variable.             |

| 1010v  | 01100 | W     | slt.yy                     | Set less than.                               |

| 1010v  | 01101 | W     | $\mathrm{sltu}.yy$         | Set less than unsigned.                      |

| 1010v  | 01110 | 0     | seq.yy                     | Set equal.                                   |

| 1010x  | 01111 | X     |                            | reserved                                     |

| 1010v  | 10000 | 0     | add.yy                     | Add signed (flag overflow).                  |

| 1010v  | 10001 | 0     | $\operatorname{addu}.yy$   | Add unsigned (no overflow).                  |

| 1010x  | 10010 | X     |                            | reserved                                     |

| 1010x  | 10011 | X     |                            | reserved                                     |

| 1010v  | 10100 | 0     | and. $yy$                  | Bitwise logical AND.                         |

| 1010v  | 10101 | 0     | or. $yy$                   | Bitwise logical OR.                          |

| 1010v  | 10110 | 0     | xor.yy                     | Bitwise logical XOR.                         |

| 1010v  | 10111 | 0     | $\operatorname{nor}.yy$    | Bitwise logical NOR.                         |

| 1010x  | 11000 | X     |                            | reserved                                     |

| 1010v  | 11001 | 0     | ${ m cmvnez}.yy$           | Conditional move not equal zero.             |

| 1010v  | 11010 | 0     | ${ m cmvgez}.yy$           | Conditional move greater than or equal zero. |

| 1010v  | 11011 | 0     | $\mathrm{cmvlez}.yy$       | Conditional move less than or equal zero.    |

| 1010x  | 11100 | x     |                            | reserved                                     |

| 1010v  | 11101 | 0     | ${ m cmveqz}.yy$           | Conditional move equal zero.                 |

| 1010v  | 11110 | 0     | $\operatorname{cmvltz}.yy$ | Conditional move less than zero.             |

| 1010v  | 11111 | 0     | ${ m cmvgtz}.yy$           | Conditional move greater than zero.          |

# Note:

When format is 11110 and opers is 0, yy is "vv"

When format is 11111 and opers is 0, yy is "vs"

When format is 11111 and opers is 1, yy is "sv"

All other encodings are reserved.

Table 6: Field encoding for integer register-register instructions.

#### AND.VV

#### And Vector-Vector

| 31 	 26 | 25 21 | $20 \ 16$ | 15 11 | 10 | 95 | 4 0 |

|---------|-------|-----------|-------|----|----|-----|

| COP2    | IVV   | vt        | AND   | VS | VW | vd  |

| 010010  | 10100 |           | 10100 | 0  |    |     |

| 6       | 5     | 5         | 5     | 1  | 5  | 5   |

# Format:

and.vv vw, vd, vt

# Description:

The vector register vlr is read to give n the number of elements to compute. The first n elements of vector register vt are combined with first n elements of vector register vd in a bitwise logical AND operation. The results are placed in the first n elements of vector register vw.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

#### **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception.

#### AND.VS

#### And Vector-Scalar

|   | 31 	 26 | 25 21 | $20 \ 16$  | 15 11 | 10 | 9 5 | 4 0 |

|---|---------|-------|------------|-------|----|-----|-----|

| ı | COP2    | IVS   | $_{ m rt}$ | AND   | VS | vw  | vd  |

|   | 010010  | 10101 |            | 10100 | 0  |     |     |

|   | 6       | 5     | 5          | 5     | 1  | 5   | 5   |

#### Format:

and.vs vw, vd, rt

# Description:

The vector register vlr is read to give n the number of elements to compute. The first n elements of vector register vd are combined with scalar register rt in a bitwise logical AND operation. The results are placed in the first n elements of vector register vw.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

#### **Exceptions:**

#### OR.VV

### Or Vector-Vector

| 31 	 26 | 25 	 21 | 20 16 | 15 11 | 10 | 9 5 | 4 0 |

|---------|---------|-------|-------|----|-----|-----|

| COP2    | IVV     | vt    | OR    | VS | VW  | vd  |

| 010010  | 10100   |       | 10101 | 0  |     |     |

| 6       | 5       | 5     | 5     | 1  | 5   | 5   |

# OR.VS

#### Or Vector-Scalar

| 31 	 26 | 25 21 | $20 \ 16$           | 15 11 | 10 | 9 5 | 4 0 |

|---------|-------|---------------------|-------|----|-----|-----|

| COP2    | IVS   | $\operatorname{rt}$ | OR    | VS | VW  | vd  |

| 010010  | 10101 |                     | 10101 | 0  |     |     |

| 6       | 5     | 5                   | 5     | 1  | 5   | 5   |

#### Format:

or.vv vw, vd, vt

# Description:

The vector register vlr is read to give n the number of elements to compute. The first n elements of vector register vd are combined with first n elements of vector register vt in a bitwise logical OR operation. The results are placed in the first n elements of vector register vw.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

#### **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception.

# Format:

or.vs vw, vd, rt

# Description:

The vector register vlr is read to give n the number of elements to compute. The first n elements of vector register vd are combined with scalar register rt in a bitwise logical OR operation. The results are placed in the first n elements of vector register vw.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

#### Exceptions:

#### XOR.VV

#### Xor Vector-Vector

| 31 2  | 6 | $^{25}$ | 21  | $20 \ 16$ | 15  | 11  | 10 | 9 5 | 4 0 |

|-------|---|---------|-----|-----------|-----|-----|----|-----|-----|

| COP   | 2 | IV      | V   | vt        | X(  | DR  | VS | vw  | vd  |

| 01001 | 0 | 101     | 100 |           | 101 | 110 | 0  |     |     |

| 6     |   | ļ.      | í   | 5         |     | 5   | 1  | 5   | 5   |

# Format:

xor.vv vw, vd, vt

# Description:

The vector register vlr is read to give n the number of elements to compute. The first n elements of vector register vd are combined with first n elements of vector register vt in a bitwise logical XOR operation. The results are placed in the first n elements of vector register vw.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

#### **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception.

#### XOR.VS

#### Xor Vector-Scalar

| 31  | 26  | 25  | 21  | 20 16               | 15 | 11  | 10 | 95 | 4 0 |

|-----|-----|-----|-----|---------------------|----|-----|----|----|-----|

| СО  | P2  | ΙV  | /S  | $\operatorname{rt}$ | Χ( | OR  | VS | vw | vd  |

| 010 | 010 | 101 | 101 |                     | 10 | 110 | 0  |    |     |

| - 6 | ;   | ļ   | j j | 5                   | ļ  | j j | 1  | 5  | 5   |

#### Format:

xor.vs vw, vd, rt

# Description:

The vector register vlr is read to give n the number of elements to compute. The first n elements of vector register vd are combined with scalar register rt in a bitwise logical XOR operation. The results are placed in the first n elements of vector register vw.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

#### **Exceptions:**

#### NOR.VV

# Nor Vector-Vector

| 31    | 26 | $^{25}$ | 21  | $20 \ 16$ | 15 | 11  | 10 | 9 5 | 4 0 |

|-------|----|---------|-----|-----------|----|-----|----|-----|-----|

| COP   | 2  | IV      | 'V  | vt        | N( | ΟR  | VS | VW  | vd  |

| 01003 | 10 | 101     | 100 |           | 10 | 111 | 0  |     |     |

| 6     |    |         | í   | 5         |    | ă.  | 1  | 5   | 5   |

#### Format:

nor.vv vw, vd, vt

# Description:

The vector register vlr is read to give n the number of elements to compute. The first n elements of vector register vd are combined with first n elements of vector register vt in a bitwise logical NOR operation. The results are placed in the first n elements of vector register vw.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

Note: the operation "nor.vv vw, vd, \$vr0" performs a vector bitwise NOT operation.

# Operation:

# **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception.

#### NOR.VS

#### Nor Vector-Scalar

|   | 31 	 26 | 25 - 21 | $20 \ 16$  | 15 11 | 10 | 9 5 | 4 0 |

|---|---------|---------|------------|-------|----|-----|-----|

|   | COP2    | IVS     | $_{ m rt}$ | NOR   | VS | VW  | vd  |

| I | 010010  | 10101   |            | 10111 | 0  |     |     |

|   | 6       | 5       | 5          | 5     | 1  | 5   | 5   |

#### Format:

nor.vs vw, vd, rt

# Description:

The vector register vlr is read to give n the number of elements to compute. The first n elements of vector register vt are combined with scalar register rt in a bitwise logical NOR operation. The results are placed in the first n elements of vector register vw.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

```

for (i=0; i<vlr; i++)

v[vw][i] = v[vd][i] nor r[rt];</pre>

```

#### **Exceptions:**

#### ADD.VV

#### Add Vector-Vector

| 31 	 26 | 25 	 21 | $20 \ 16$ | 15 11 | 10 | 9 5 | 4 0 |

|---------|---------|-----------|-------|----|-----|-----|

| COP2    | IVV     | vt        | ADD   | VS | VW  | vd  |

| 010010  | 10100   |           | 10000 | 0  |     |     |

| 6       | 5       | 5         | 5     | 1  | 5   | 5   |

#### Format:

add.vv vw, vd, vt

# Description:

The vector register vlr is read to give n the number of elements to be added. The first n elements of vector register vt are added to the first n elements of vector register vd and the results are placed in the first n elements of vector register vw.

The input elements are treated as signed integers. The appropriate bit in vovf is set for any result that overflows.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

```

for (i=0; i<vlr; i++)

{

v[vw][i] = v[vd][i] + v[vt][i];

if (overflow_on_add(v[vd][i],v[vt][i]))

vcr[VOVF] |= (1<<i);

}</pre>

```

# **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception.

#### ADD.VS

#### Add Vector-Scalar

| 31   | 26  | $^{25}$ | 21  | $20 \ 16$           | 15  | 11  | 10 | 9 5 | 4 0 |

|------|-----|---------|-----|---------------------|-----|-----|----|-----|-----|

| СО   | P2  | IV      | /S  | $\operatorname{rt}$ | Al  | DD  | VS | VW  | vd  |

| 0100 | 010 | 101     | 101 |                     | 100 | 000 | 0  |     |     |

| 6    |     | Ę       | 5   | 5                   | į.  | 5   | 1  | 5   | 5   |

#### Format:

add.vs vw, vd, rt

# Description:

The vector register vlr is read to give n the number of elements to be added. The first n elements of vector register vd are added to the scalar register rt and the results are placed in the first n elements of vector register vw.

The input elements are treated as signed integers. The appropriate bit of vovf is set for any result that overflows.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

```

for (i=0; i<vlr; i++)

{

v[vw][i] = v[vd][i] + r[rt];

if (overflow_on_add(v[vd][i],r[rt]))

vcr[VOVF] |= (1<<i);

}</pre>

```

# Exceptions:

### ADDU.VV Add Unsigned Vector-Vector

| 31 	 26 | 25 	 21 | $20 \ 16$ | 15 11 | 10 | 9 5 | 4 0 |

|---------|---------|-----------|-------|----|-----|-----|

| COP2    | IVV     | vt        | ADDU  | VS | vw  | vd  |

| 010010  | 10100   |           | 10001 | 0  |     |     |

| 6       | 5       | 5         | 5     | 1  | 5   | 5   |

#### Format:

addu.vv vw, vd, vt

# Description:

The vector register vlr is read to give n the number of elements to be added. The first n elements of vector register vt are added to the first n elements of vector register vd and the results are placed in the first n elements of vector register vw.

The input elements are treated as unsigned integers. Overflows are ignored.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

```

for (i=0; i<vlr; i++)

{

v[vw][i] = v[vd][i] + v[vt][i];

}</pre>

```

# **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception.

### ADDU.VS Add Unsigned Vector-Scalar

| 31 	 26 | 25 	 21 | $20 \ 16$ | 15 11 | 10 | 9 5 | 4 0 |

|---------|---------|-----------|-------|----|-----|-----|

| COP2    | IVS     | rt        | ADDU  | VS | vw  | vd  |

| 010010  | 10101   |           | 10001 | 0  |     |     |

| 6       | 5       | 5         | 5     | 1  | 5   | 5   |

#### Format:

addu.vs vw, vd, rt

# Description:

The vector register vlr is read to give n the number of elements to be added. The first n elements of vector register vd are added to the scalar register rt and the results are placed in the first n elements of vector register vw.

The input elements are treated as unsigned integers. Overflows are ignored.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

```

for (i=0; i<vlr; i++)

{

v[vw][i] = v[vd][i] + r[rt];

}</pre>

```

# **Exceptions:**

# SUB.VV

# Subtract Vector-Vector

| 31 	 26 | 25 	 21 | $20 \ 16$ | 15 11 | 10 | 9 5 | 4 0 |

|---------|---------|-----------|-------|----|-----|-----|

| COP2    | IVV     | vt        | SUB   | VS | VW  | vd  |

| 010010  | 10100   |           | 00000 | 0  |     |     |

| 6       | 5       | 5         | 5     | 1  | 5   | 5   |

#### Format:

sub.vv vw, vd, vt

# Description:

The vector register vlr is read to give n the number of elements to be subtracted. The first n elements of vector register vt are subtracted from the first n elements of vector register vd and the results are placed in the first n elements of vector register vw.

The input elements are treated as signed integers. The appropriate bit of vovf is set for any result that overflows.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

Note: the operation "sub.vv vw, \$vr0, vt" performs a vector negate operation.

#### Operation:

```

for (i=0; i<vlr; i++)

{

v[vw][i] = v[vd][i] - v[vt][i];

if (overflow_on_sub(v[vd][i],v[vt][i]))

vcr[VOVF] |= (1<<i);

}</pre>

```

# **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception.

#### SUB.VS

#### Subtract Vector-Scalar

| 31   | 26     | $^{25}$ | 21  | $20 \ 16$           | 15  | 11  | 10 | 9 5 | 4 0 |

|------|--------|---------|-----|---------------------|-----|-----|----|-----|-----|

| COP2 |        | IVS     |     | $\operatorname{rt}$ | SU  | JB  | VS | VW  | vd  |

| 0100 | 010010 |         | 101 |                     | 000 | 000 | 0  |     |     |

| 6    |        | 5 5     |     | 5                   | 5   |     | 1  | 5   | 5   |

#### Format:

sub.vs vw, vd, rt

# Description:

The vector register vlr is read to give n the number of elements to be subtracted. The scalar register rt is subtracted from the first n elements of vector register vd and the results are placed in the first n elements of vector register vw.

The input elements are treated as signed integers. The appropriate bit of vovf is set for any result that overflows.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

```

for (i=0; i<vlr; i++)

{

v[vw][i] = v[vd][i] - r[rt];

if (overflow_on_sub(v[vd][i],r[rt]))

vcr[VOVF] |= (1<<i);

}</pre>

```

# **Exceptions:**

### SUB.SV

# Subtract Scalar-Vector

| 31 	 26 | 25 	 21 | $20 \ 16$ | 15 - 11 | 10 | 9 5 | 4 0 |

|---------|---------|-----------|---------|----|-----|-----|

| COP2    | IVS     | rt        | SUB     | SV | VW  | vd  |

| 010010  | 10101   |           | 00000   | 1  |     |     |

| 6       | 5       | 5         | 5       | 1  | 5   | 5   |

#### Format:

sub.sv vw, rt, vd

# Description:

The vector register vlr is read to give n the number of elements to be subtracted. The first n elements of vector register vd are subtracted from the scalar register rt and the results are placed in the first n elements of vector register vw.

The input elements are treated as signed integers. The appropriate bit of vovf is set for any result that overflows.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

```

for (i=0; i<vlr; i++)

{

v[vw][i] = r[rt] - v[vd][i];

if (overflow_on_sub(r[rt],v[vd][i]))

vcr[VOVF] |= (1<<i);

}</pre>

```

## **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception.

#### SUBU.VV

# Subtract Unsigned Vector-Vector

| 31 	 26 | 25 	 21 | $20 \ 16$ | 15 11 | 10 | 9 5 | 4 0 |

|---------|---------|-----------|-------|----|-----|-----|

| COP2    | IVV     | vt        | SUBU  | VS | vw  | vd  |

| 010010  | 10100   |           | 00001 | 0  |     |     |

| 6       | 5       | 5         | 5     | 1  | 5   | 5   |

#### Format:

subu.vv vw, vd, vt

# Description:

The vector register vlr is read to give n the number of elements to be subtracted. The first n elements of vector register vt are subtracted from the first n elements of vector register vd and the results are placed in the first n elements of vector register vw.

The input elements are treated as unsigned integers. Overflows are ignored.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

## Operation:

```

for (i=0; i<vlr; i++)

{

v[vw][i] = v[vd][i] - v[vt][i];

}</pre>

```

# **Exceptions:**

# SUBU.VS

# Subtract Unsigned Vector-Scalar

| 31 20  | 25 21 | 20 16 | 15 11 | 10 | 9 5 | 4 0 |   |

|--------|-------|-------|-------|----|-----|-----|---|

| COP2   | IVS   | rt    | SUBU  | VS | vw  | vd  |   |

| 010010 | 10101 |       | 00001 | 0  |     |     |   |

| 6      | 5     | 5     | 5     | 1  | 5   | 5   | • |

#### Format:

subu.vs vw, vd, rt

# Description:

The vector register vlr is read to give n the number of elements to be subtracted. The scalar register rt is subtracted from the first n elements of vector register vd and the results are placed in the first n elements of vector register vw.

The input elements are treated as unsigned integers. Overflows are ignored.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

```

for (i=0; i<vlr; i++)

{

v[vw][i] = v[vd][i] - r[rt];

}</pre>

```

## **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception.

# SUBU.SV

# Subtract Unsigned Scalar-Vector

| 31 	 26 | 25 	 21 | $20 \ 16$ | 15 11 | 10 | 9 5 | 4 0 |

|---------|---------|-----------|-------|----|-----|-----|

| COP2    | IVS     | rt        | SUBU  | SV | vw  | vd  |

| 010010  | 10101   |           | 00001 | 1  |     |     |

| 6       | 5       | 5         | 5     | 1  | 5   | 5   |

#### Format:

subu.sv vw, rt, vd

# Description:

The vector register vlr is read to give n the number of elements to be subtracted. The first n elements of vector register vd are subtracted from the scalar register rt and the results are placed in the first n elements of vector register vw.

The input elements are treated as unsigned integers. Overflows are ignored.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

```

for (i=0; i<vlr; i++)

{

v[vw][i] = r[rt] - v[vd][i];

}</pre>

```

## **Exceptions:**

# SLLV.VV Shift Left Logical Variable Vector-Vector

| 31 	 26 | 25 	 21 | $20 \ 16$ | 15 11 | 10 | 9 5 | 4 0 |

|---------|---------|-----------|-------|----|-----|-----|

| COP2    | IVV     | vt        | SLLV  | VS | vw  | vd  |

| 010010  | 10100   |           | 01000 | 0  |     |     |

| 6       | 5       | 5         | 5     | 1  | 5   | 5   |

## Format:

sllv.vv vw, vd, vt

# Description:

The vector register vlr is read to give n the number of elements to shift. The first n elements of vector register vd are shifted left by the number of bits given in the least significant 5 bits of the first n elements of vector register vt. Zeros are inserted into the low order bits. The results are placed in the first n elements of vector register vw.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

## Operation:

# **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception.

# SLLV.VS Shift Left Logical Variable Vector-Scalar

| 31 	 26 | 25 21 | $20 \ 16$  | 15 11 | 10 | 9 5 | 4 0 |

|---------|-------|------------|-------|----|-----|-----|

| COP2    | IVS   | $_{ m rt}$ | SLLV  | VS | vw  | vd  |

| 010010  | 10101 |            | 01000 | 0  |     |     |

| 6       | 5     | 5          | 5     | 1  | 5   | 5   |

#### Format:

sllv.vs vw, vd, rt

# Description:

The vector register vlr is read to give n the number of elements to shift. The first n elements of vector register vd are shifted left by the number of bits given in the least significant 5 bits of scalar register rt. Zeros are inserted into the low order bits. The results are placed in the first n elements of vector register vw.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

```

for (i=0; i<vlr; i++)

v[vw][i] = v[vd][i] << (r[rt] & Ox1f);</pre>

```

### **Exceptions:**

# SLLV.SV Shift Left Logical Variable Scalar-Vector

| 31 	 26 | 25 	 21 | $20 \ 16$ | 15 11 | 10 | 9 5 | 4 0 |

|---------|---------|-----------|-------|----|-----|-----|

| COP2    | IVS     | rt        | SLLV  | SV | vw  | vd  |

| 010010  | 10101   |           | 01000 | 1  |     |     |

| 6       | 5       | 5         | 5     | 1  | 5   | - 5 |

#### Format:

sllv.sv vw, rt, vd

# Description:

The vector register vlr is read to give n the number of elements to shift. The scalar register rt is shifted left by the number of bits given in the least significant 5 bits of the first n elements of vector register vd. Zeros are inserted into the low order bits. The results are placed in the first n elements of vector register vw.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

### **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception.

# SRAV.VV Shift Right Arithmetic Variable Vector-Vector

| 31 26  | 3 	 25 	 21 | $20 \ 16$ | 15 11 | 10 | 9 5 | 4 0 |

|--------|-------------|-----------|-------|----|-----|-----|

| COP2   | IVV         | vt        | SRAV  | VS | VW  | vd  |

| 010010 | 10100       |           | 01011 | 0  |     |     |

| 6      | 5           | 5         | 5     | 1  | 5   | 5   |

#### Format:

srav.vv vw, vd, vt

# Description:

The vector register vlr is read to give n the number of elements to shift. The first n elements of vector register vd are shifted right by the number of bits given in the least significant 5 bits of the first n elements of vector register vt. The high order bits are sign-extended. The results are placed in the first n elements of vector register vw.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

```

for (i=0; i<vlr; i++)

v[vw][i] = v[vd][i] shra (v[vt][i] & 0x1f);</pre>

```

### **Exceptions:**

# SRAV.VS Shift Right Arithmetic Variable Vector-Scalar

| 31 	 26 | 25 21 | $20 \ 16$  | 15 11 | 10 | 95 | 4 0 |

|---------|-------|------------|-------|----|----|-----|

| COP2    | IVS   | $_{ m rt}$ | SRAV  | VS | vw | vd  |

| 010010  | 10101 |            | 01011 | 0  |    |     |

| 6       | 5     | 5          | 5     | 1  | 5  | 5   |

### Format:

srav.vs vw, vd, rt

# Description:

The vector register vlr is read to give n the number of elements to shift. The first n elements of vector register vd are shifted right by the number of bits given in the least significant 5 bits of scalar register rt. The high order bits are sign-extended. The results are placed in the first n elements of vector register vw.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

### **Exceptions:**

Reserved instruction exception. Coprocessor unusable exception. Vector operation exception.

# SRAV.SV Shift Right Arithmetic Variable Scalar-Vector

|   | 31 	 26 | 25 	 21 | $20 \ 16$ | 15 11 | 10 | 9 5 | 4 0 |

|---|---------|---------|-----------|-------|----|-----|-----|

| ı | COP2    | IVS     | rt        | SRAV  | SV | vw  | vd  |

|   | 010010  | 10101   |           | 01011 | 1  |     |     |

|   | 6       | 5       | 5         | 5     | 1  | 5   | 5   |

#### Format:

srav.sv vw, rt, vd

# Description:

The vector register vlr is read to give n the number of elements to shift. The scalar register rt is shifted right by the number of bits given in the least significant 5 bits of the first n elements of vector register vd. The high order bits are signextended. The results are placed in the first n elements of vector register vw.

A vector operation exception is raised if vlr is larger than the implementation's maximum vector length.

# Operation:

```

for (i=0; i<vlr; i++)

v[vw][i] = r[rt] shra (v[vd][i] & Ox1f);</pre>

```

### **Exceptions:**

# SRLV.VV Shift Right Logical Variable Vector-Vector

| 31 	 26 | 25 	 21 | $20 \ 16$ | 15 11 | 10 | 9 5 | 4 0 |

|---------|---------|-----------|-------|----|-----|-----|

| COP2    | IVV     | vt        | SRLV  | VS | vw  | vd  |

| 010010  | 10100   |           | 01001 | 0  |     |     |

| 6       | 5       | 5         | 5     | 1  | 5   | 5   |

#### Format:

srlv.vv vw, vd, vt

# Description: