# A Low-Power 32 bit Datapath Design

by

# Seongmoo Heo

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Master of Science in Electrical Engineering and Computer Science

at the

## MASSACHUSETTS INSTITUTE OF TECHNOLOGY

August 2000

©2000 Massachusetts Institute of Technology All rights reserved.

Department of Electrical Engineering and Computer Science August 15, 2000

Certified by .....

Krste Asanović Assistant Professor Thesis Supervisor

Accepted by .....

Arthur C. Smith Chairman, Department Committee on Graduate Students

### A Low-Power 32 bit Datapath Design

by

### Seongmoo Heo

Submitted to the Department of Electrical Engineering and Computer Science on August 15, 2000, in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering and Computer Science

#### Abstract

In this thesis, we design a low-power 32 bit datapath with a five-stage pipeline for a single-issue MIPS RISC microprocessor. We compare various designs of flipflops, latches, and muxes in terms of power, delay, and PDP (Power-Delay Product) since they are the most common building blocks in the datapath. We develop new precise analytic energy models for flipflops, latches, and muxes.

We develop a new simulation-based energy model, the *net-transition energy model*, to calculate energy consumption quickly and accurately. The energy model combines effective capacitance values extracted from layout and transition counts obtained from a simulator to estimate energy dissipation. We build a *capacitance merging method* to extract precise effective capacitance values from layouts. Also, we model the short-circuit energy for an inverter.

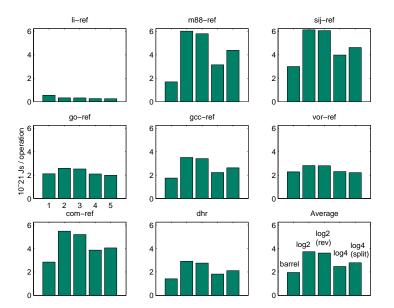

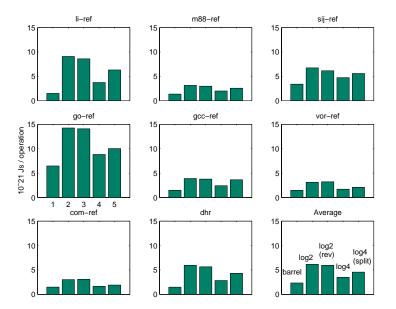

We custom-design the prototype datapath for a 0.25  $\mu$ m TSMC process. We show design decisions on metal allocation, floor planning, and an adder — one of the most important blocks in the datapath. We develop an area-efficient logic unit design. Also, we explore shifter designs – a simple but essential block in the datapath – including our new shifter design, a *split log shifter* using SPECint95 and Dhrystone benchmarks. We find that the barrel shifter is a better choice than any log shifter.

Finally, we analyze the datapath energy consumption using our energy model. We show energy breakdowns by components and functional blocks. We develop a novel method that chooses better designs of flipflops and latches in different places of the datapath, based on the data and clock activities. We also examine the effect of clock gating.

Thesis Supervisor: Krste Asanović Title: Assistant Professor

#### A Low-Power 32 bit Datapath Design

by

### Seongmoo Heo

Submitted to the Department of Electrical Engineering and Computer Science on August 15, 2000, in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering and Computer Science

#### Abstract

In this thesis, we design a low-power 32 bit datapath with a five-stage pipeline for a single-issue MIPS RISC microprocessor. We compare various designs of flipflops, latches, and muxes in terms of power, delay, and PDP (Power-Delay Product) since they are the most common building blocks in the datapath. We develop new precise analytic energy models for flipflops, latches, and muxes.

We develop a new simulation-based energy model, the *net-transition energy model*, to calculate energy consumption quickly and accurately. The energy model combines effective capacitance values extracted from layout and transition counts obtained from a simulator to estimate energy dissipation. We build a *capacitance merging method* to extract precise effective capacitance values from layouts. Also, we model the short-circuit energy for an inverter.

We custom-design the prototype datapath for a 0.25  $\mu$ m TSMC process. We show design decisions on metal allocation, floor planning, and an adder — one of the most important blocks in the datapath. We develop an area-efficient logic unit design. Also, we explore shifter designs – a simple but essential block in the datapath – including our new shifter design, a *split log shifter* using SPECint95 and Dhrystone benchmarks. We find that the barrel shifter is a better choice than any log shifter.

Finally, we analyze the datapath energy consumption using our energy model. We show energy breakdowns by components and functional blocks. We develop a novel method that chooses better designs of flipflops and latches in different places of the datapath, based on the data and clock activities. We also examine the effect of clock gating.

Thesis Supervisor: Krste Asanović Title: Assistant Professor

# Acknowledgments

First of all, I'd like to thank my great advisor, Krste Asanović, deeply for his inspiring advice and guidance and also for spending a great deal of time and energy for this thesis. He let me realize how fun research is. I truly thank him for giving me chance to work with him.

I also thank my awesome group mates: Ronny Krashinsky, Mike Zhang, Jessica Tseng, Mark Hampton, Albert Ma, Luis Villa, and Serhii Zhak for helpful discussions and for helping with my thesis. In particular, I give special thanks to Ronny Krashinsky for helping me with English writing. He willingly spent lots of time and energy and made my thesis readable.

I want to thank my sweetheart and also my best buddy, Jieun Yoo, very much for her loving care. She gave me the boundless encouragement and motivation and led me to finish this thesis.

Finally, I want to thank my wonderful parents and my cute sister for all the support and for believing in me.

I should point out that much of energy modeling (Chapter 3) was co-work with Ronny Krashinsky and Mike Zhang. In particular, Mike Zhang developed a custom tool, mergecap and Ronny Krashinsky built the SyCHOSys cycle-accurate simulator. Also, Jessica Tseng provided her register file design.

Life is good!

# Contents

| 1 | Intr | oduction                                               | 15 |

|---|------|--------------------------------------------------------|----|

| 2 | Flip | flop, Latch, and Mux                                   | 19 |

|   | 2.1  | Simulation Test Bench                                  | 20 |

|   | 2.2  | Flipflop                                               | 20 |

|   |      | 2.2.1 Delay                                            | 21 |

|   |      | 2.2.2 Power                                            | 22 |

|   |      | 2.2.3 PDP                                              | 25 |

|   | 2.3  | Latch                                                  | 26 |

|   |      | 2.3.1 Delay                                            | 27 |

|   |      | 2.3.2 Power                                            | 28 |

|   |      | 2.3.3 PDP                                              | 29 |

|   | 2.4  | Mux                                                    | 30 |

| 3 | Ene  | rgy Modeling                                           | 35 |

|   | 3.1  | Sources of Power Dissipation in Digital CMOS Circuits  | 35 |

|   | 3.2  | Previous Energy Models                                 | 36 |

|   | 3.3  | Node-Transition Energy Model                           | 38 |

|   |      | 3.3.1 Transition Counts Gathering                      | 38 |

|   |      | 3.3.2 Capacitance Merging Method                       | 40 |

|   |      | 3.3.3 Calibrating Effective Gate and Drain Capacitance | 43 |

|   |      | 3.3.4 Energy Calculation                               | 48 |

|   |      | 3.3.5 Evaluation of Our Energy Model                   | 50 |

|   | 3.4  | Short-0    | Circuit Energy Modeling of an Inverter                | 51 |

|---|------|------------|-------------------------------------------------------|----|

| 4 | Data | apath D    | esign                                                 | 57 |

|   | 4.1  | VLSI I     | Design                                                | 59 |

|   |      | 4.1.1      | Full-custom Design                                    | 59 |

|   |      | 4.1.2      | Metal Allocation                                      | 59 |

|   | 4.2  | Floor p    | blanning                                              | 61 |

|   | 4.3  | ALU .      |                                                       | 62 |

|   |      | 4.3.1      | Adder Design                                          | 62 |

|   |      | 4.3.2      | Logic Unit and Branch Checker Design                  | 65 |

|   | 4.4  | Shifter    | ·                                                     | 66 |

|   |      | 4.4.1      | Types of Shifters                                     | 67 |

|   |      | 4.4.2      | Analysis of Shift Instructions                        | 68 |

|   |      | 4.4.3      | Comparison of Shifters                                | 69 |

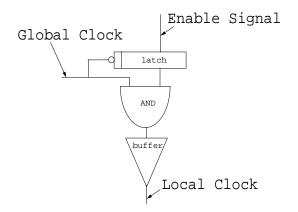

|   | 4.5  | Clock      | Gating                                                | 76 |

| 5 | Ana  | lysis of [ | Datapath Energy                                       | 79 |

|   | 5.1  | Bench      | marks                                                 | 79 |

|   | 5.2  | Energy     | Breakdown                                             | 80 |

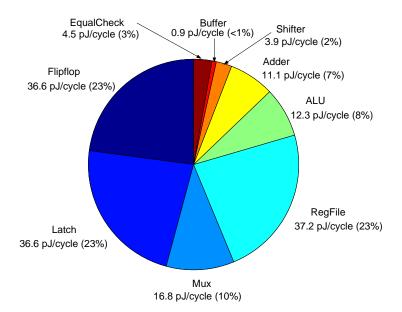

|   |      | 5.2.1      | Energy Breakdown By Component Type                    | 80 |

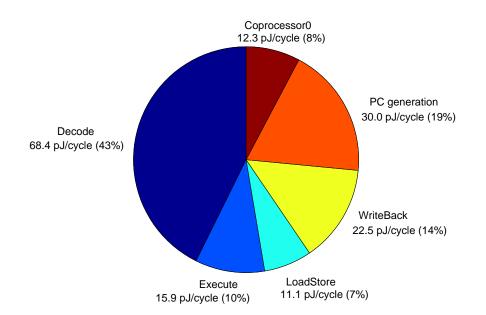

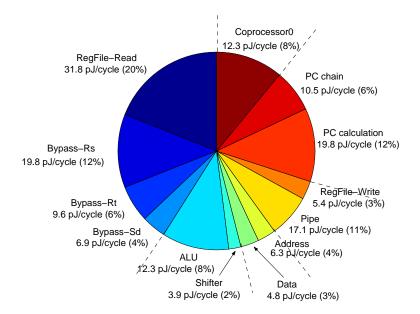

|   |      | 5.2.2      | Functional Energy Breakdown                           | 81 |

|   | 5.3  | Selecti    | on of Flipflops and Latches                           | 84 |

|   |      | 5.3.1      | Data Activity                                         | 84 |

|   |      | 5.3.2      | Clock Activity                                        | 85 |

|   |      | 5.3.3      | Power and PDP Curves for Flipflop and Latch Selection | 86 |

|   | 5.4  | Effect     | of Clock Gating                                       | 89 |

| 6 | Con  | clusion    |                                                       | 93 |

# **List of Figures**

| 1-1  | Our approach to low-power datapath design.                            | 16 |

|------|-----------------------------------------------------------------------|----|

| 2-1  | Test bench for flipflops, latches, and muxes.                         | 20 |

| 2-2  | Modified PowerPC flipflop.                                            | 21 |

| 2-3  | HL flipflop.                                                          | 21 |

| 2-4  | StrongArm 110 flipflop                                                | 22 |

| 2-5  | Transmission-gate flipflop.                                           | 23 |

| 2-6  | Power dissipation of flipflops (clock activity=1).                    | 25 |

| 2-7  | Power dissipation of modified PowerPC flipflop.                       | 26 |

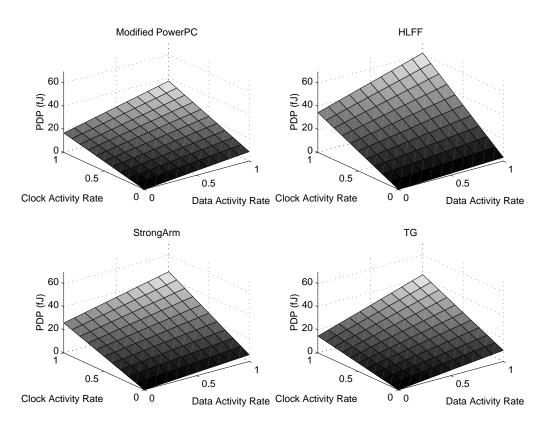

| 2-8  | PDP graphs of flipflops                                               | 27 |

| 2-9  | PDP of flipflops when clock activity rate is fixed                    | 28 |

| 2-10 | PowerPC 603 MS latch.                                                 | 29 |

| 2-11 | Pass-transistor latch.                                                | 29 |

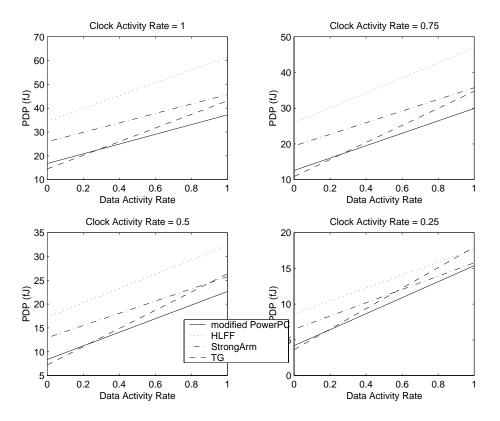

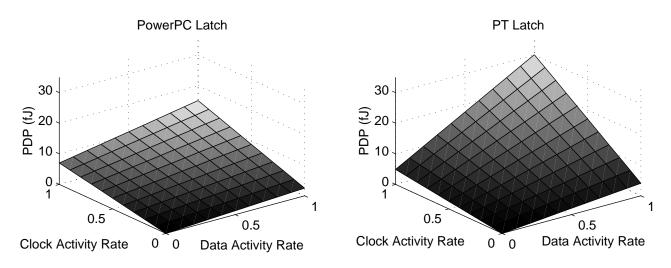

| 2-12 | PDP of latches.                                                       | 30 |

| 2-13 | PDP of latches when clock activity is fixed.                          | 31 |

| 2-14 | Transmission-gate mux                                                 | 32 |

| 2-15 | Pass-transistor mux                                                   | 32 |

| 3-1  | A 3-input Transmission-gate mux                                       | 39 |

| 3-2  |                                                                       | 40 |

| 3-3  |                                                                       | 41 |

| 3-4  |                                                                       | 42 |

| 3-5  | Schematic of cascaded inverters and the capacitances connected to the |    |

|      | L. L                              | 43 |

| 3-6  | Layout of cascaded inverters.                                                           | 43 |

|------|-----------------------------------------------------------------------------------------|----|

| 3-7  | The netlist and the capacitance file of a cascaded two inverters                        | 44 |

| 3-8  | Two FO4 inverter chains.                                                                | 45 |

| 3-9  | Gray inverter.                                                                          | 46 |

| 3-10 | Deriving gp, dp, gn and dn from measurements.                                           | 47 |

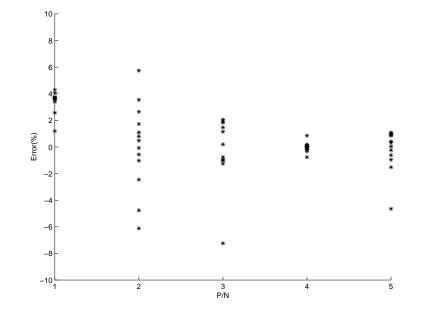

| 3-11 | Verification of gate and drain capacitance coefficients. P/N is the ratio of PMOS width |    |

|      | to NMOS width.                                                                          | 48 |

| 3-12 | Energy equations of N bit 3-input mux, N-bit positive flipflop, and 4-bit Manchester    |    |

|      | carry chain.                                                                            | 49 |

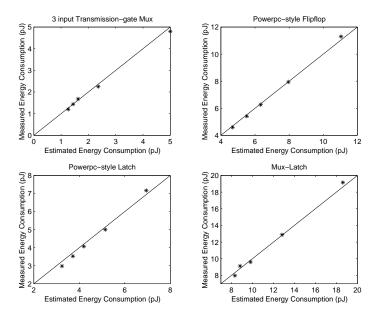

| 3-13 | Mux, latch, flipflop and mux-latch: measured energy vs. estimated energy. Ideally, all  |    |

|      | points should fall on the line.                                                         | 50 |

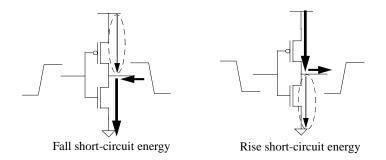

| 3-14 | Two kinds of short circuit current.                                                     | 52 |

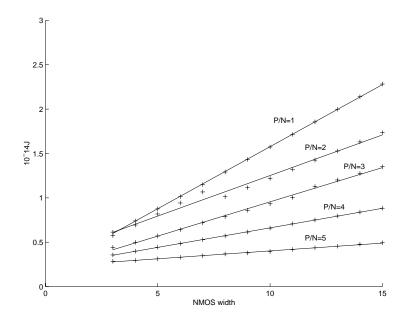

| 3-15 | Measurements of fall short-circuit energy for various inverters                         | 53 |

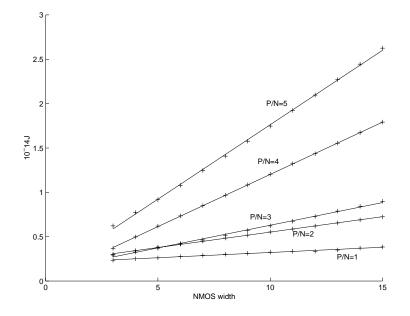

| 3-16 | Measurements of rise short-circuit energy for various inverters                         | 54 |

| 3-17 | Error between the measured average short-circuit energy and the calculated one using    |    |

|      | table lookup.                                                                           | 55 |

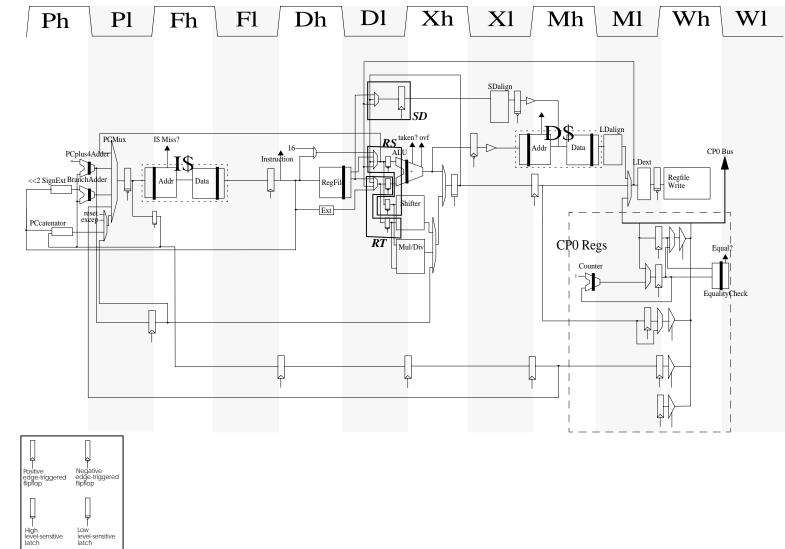

| 4-1  | Pipeline diagram for datapath.                                                          | 58 |

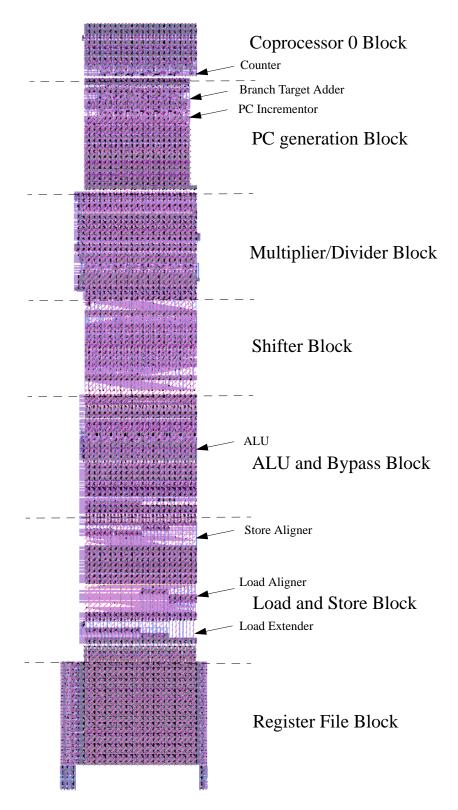

| 4-2  | Layout of the datapath.                                                                 | 60 |

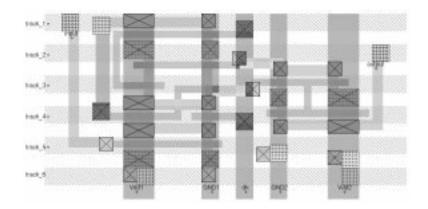

| 4-3  | Metal allocation.                                                                       | 61 |

| 4-4  | Floorplan of datapath (except coprocessor 0).                                           | 63 |

| 4-5  | Floorplan of coprocessor 0                                                              | 64 |

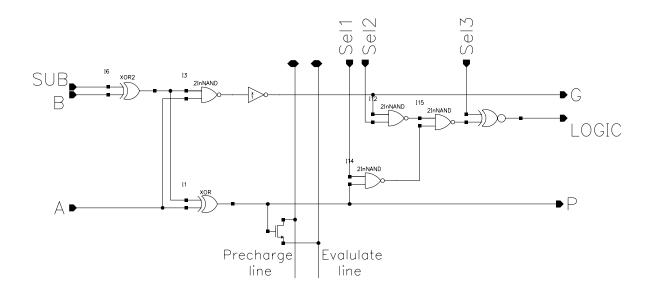

| 4-6  | Modified propagate(P) and generate(G) circuit for ALU.                                  | 66 |

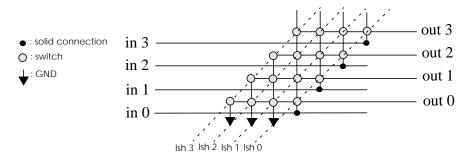

| 4-7  | A barrel shifter.                                                                       | 67 |

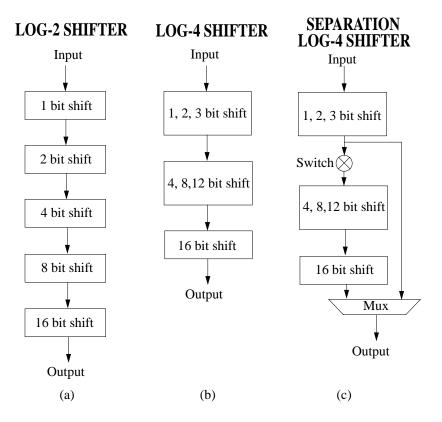

| 4-8  | Logarithmic shifters.                                                                   | 68 |

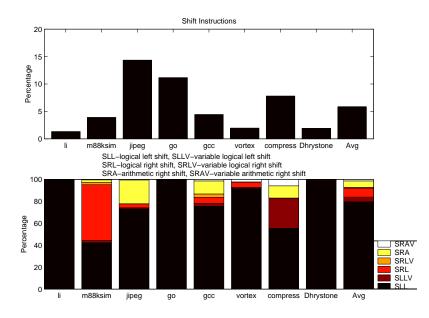

| 4-9  | Shift instructions.                                                                     | 69 |

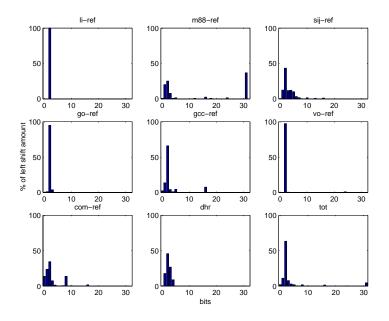

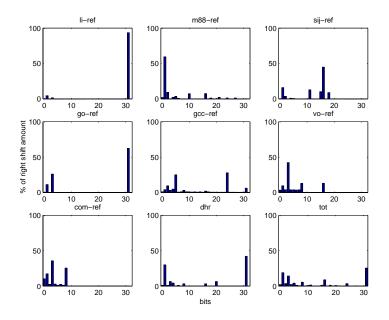

| 4-10 | Left shift amounts.                                                                     | 70 |

| 4-11 | Right shift amounts                                                                     | 71 |

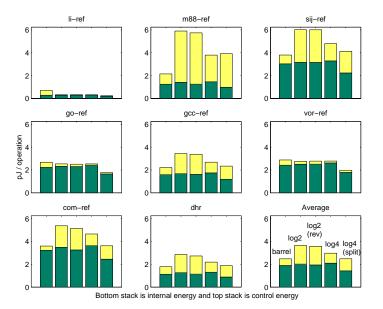

| 4-12 | Average energy of left shifters.                                                        | 73 |

| 4-13 | Average energy of right shifters                                                        | 74 |

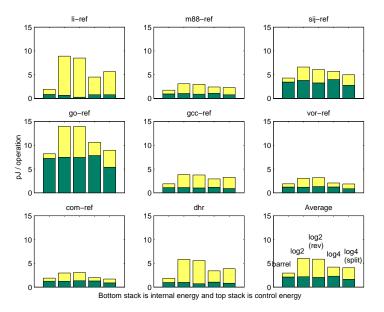

| 4-14 | Energy-delay product of left shifters.                                                   | 75 |

|------|------------------------------------------------------------------------------------------|----|

| 4-15 | Energy-delay product of right shifters                                                   | 76 |

| 4-16 | Clock gating circuit.                                                                    | 77 |

| 5-1  | Average energy breakdown by component type.                                              | 80 |

| 5-2  | Average functional energy breakdown                                                      | 82 |

| 5-3  | Average more detailed functional energy breakdown                                        | 83 |

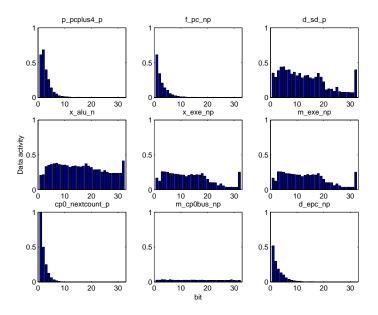

| 5-4  | Input data activity of flipflops in the datapath.                                        | 85 |

| 5-5  | Input data activity of latches in the datapath.                                          | 86 |

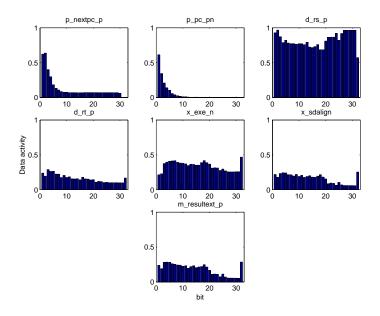

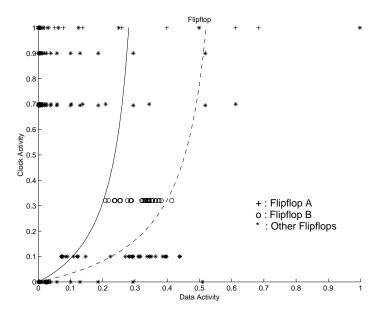

| 5-6  | Clock and data activities for various flipflops. A solid curve is a PDP curve and a      |    |

|      | dashed curve is a power curve.                                                           | 87 |

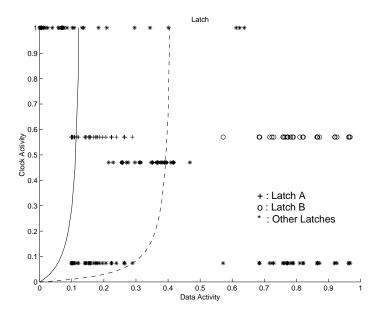

| 5-7  | Clock and data activities for various latches. A solid curve is a PDP curve and a dashed |    |

|      | curve is a power curve.                                                                  | 88 |

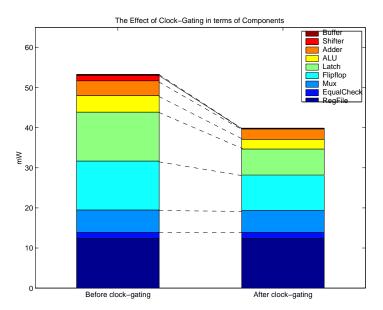

| 5-8  | The effect of clock gating in terms of components.                                       | 89 |

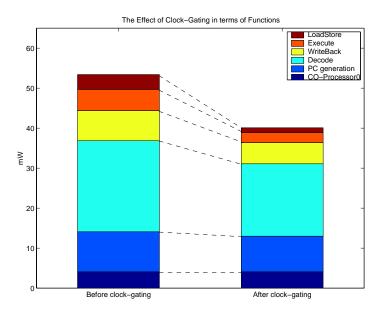

| 5-9  | The effect of clock gating in terms of functional blocks.                                | 90 |

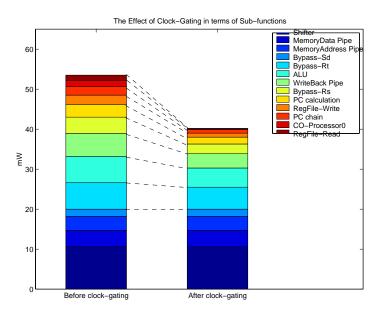

| 5-10 | The effect of clock gating in terms of sub-functional blocks.                            | 91 |

# **List of Tables**

| 2.1  | MOS model parameters and conditions.                                                                                                       | 19 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Minimum D-Q delay measurements of flipflops                                                                                                | 22 |

| 2.3  | Power measurements of flipflops (clock activity=1).                                                                                        | 24 |

| 2.4  | Power measurements of flipflops (clock activity=0).                                                                                        | 24 |

| 2.5  | PDP of flipflops (clock activity=1).                                                                                                       | 24 |

| 2.6  | PDP of flipflops (clock activity=0).                                                                                                       | 25 |

| 2.7  | D-Q delay measurements of latches                                                                                                          | 27 |

| 2.8  | Power and PDP measurements of latches (clock activity=1)                                                                                   | 28 |

| 2.9  | Power and PDP measurements of latches (clock activity=0)                                                                                   | 29 |

| 2.10 | Delays and energy consumptions measurements of muxes                                                                                       | 32 |

| 2.11 | Average energy consumptions and EDP (Energy-Delay Product) of muxes                                                                        | 33 |

| 3.1  | Short-circuit energy calculation table for an inverter. Average short-circuit energy is the average of fall and rise short-circuit energy. | 54 |

| 4.1  | Various adder designs.                                                                                                                     | 64 |

| 4.2  | Control signals for logic operation.                                                                                                       | 65 |

| 4.3  | Worst case delay of shifters. (The barrel shifter delay includes the worst case decoder                                                    |    |

|      | delay, 0.37 ns.)                                                                                                                           | 72 |

| 5.1  | Benchmarks used                                                                                                                            | 79 |

| 5.2  | Energy breakdown by component type (pJ/cycle (%)).                                                                                         | 81 |

| 5.3  | Functional energy breakdown (pJ/cycle (%)).                                                                                                | 84 |

| 5.4  | More detailed functional energy breakdown (pJ/cycle)                                                                                       | 84 |

# Chapter 1

# Introduction

As portability and embedibility become increasingly crucial for all kinds of electronic devices, the demand for low-power microprocessors is exploding. Building low-power microprocessors is challenging because performance must be maintained while lowering energy consumption. There has been tremendous research effort in this field and, as a result, many low-power microprocessors with remarkable performance have been produced. However, although low-power techniques for designing memory blocks such as RAMs or basic blocks such as an adder have been studied intensively, little work has been done in systematic design of a complete low-power datapath design — the core of the microprocessor. Accordingly, there is little understanding of why and how energy is consumed in a microprocessor datapath.

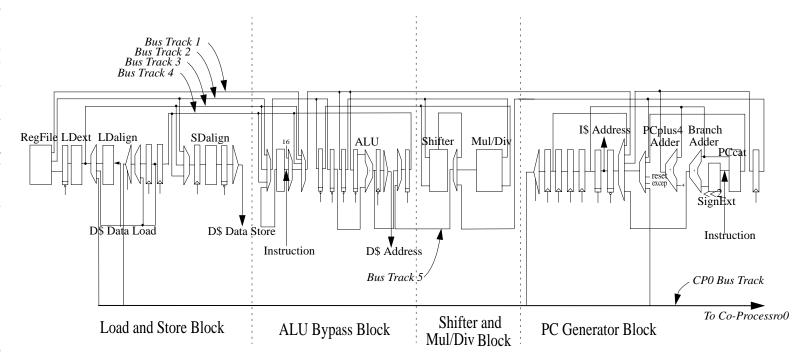

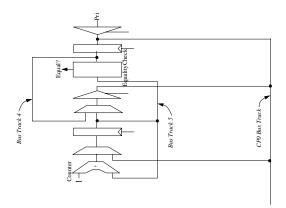

The main goal of our research is to design a prototype low-power datapath and analyze the energy consumption of the datapath. Of particular hindrance to low-power design of a datapath is its intrinsic complexity. Datapaths are collections of numerous irregular blocks which perform various functions. They have complex interconnect structures, a wide variety of circuit types, and a rich set of activation patterns [8]. This complexity makes both the analysis of datapath energy consumption and the application of low-power techniques difficult. Therefore, we restrict our research to a simple datapath — a MIPS-II single-issue five-stage pipelined RISC datapath. The MIPS architecture is one of the simplest RISC instruction set architectures (ISAs) [6]. The main blocks of the datapath are a register file, an ALU, a shifter, a multiplier/divider, and aligners/sign-extenders for load and store instructions. Also, the datapath includes a program counter (PC) generation block and a system coprocessor block.

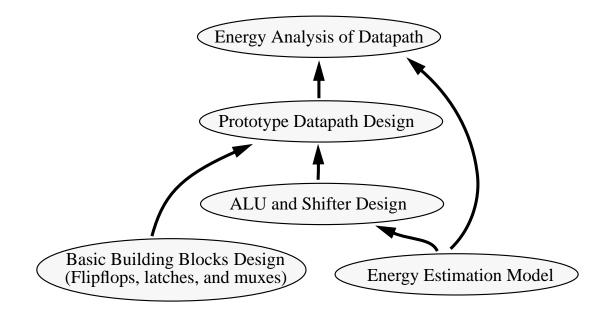

Figure 1-1: Our approach to low-power datapath design.

We believe that this research can be a base for future studies of more complicated low-power datapath designs which issue multiple instructions at the same time and which have more pipeline stages.

We approach our low-power datapath design problem in a bottom-up fashion (Figure 1-1). First, we notice that flipflops, latches, and muxes are the most common and frequentlyused building blocks in the datapath. Accordingly, their power consumption accounts for a significant portion of total power consumption. Therefore, we believe that a crucial first step when building a low-power system is to find flipflops, latches, and muxes which have good power and delay properties. In Chapter 2, we compare various flipflops, latches, and muxes intensively in terms of power and delay. We find that the traditional energy measurements of flipflops and latches which assume random input and un-gated clock are misleading especially for the datapath flipflops and latches, because the datapath gives a wide variety of data and clock activities to flipflops and latches. We develop analytic energy models for flipflops and latches which present energy dissipation of flipflops and latches as a two-variable function of input data and clock activities, and thus show dynamic features of energy dissipation. As for muxes, we develop an analytical energy comparison method.

For the detailed energy analysis of the datapath, we require a fast and accurate energy estimation tool, since circuit simulators are too slow to use for large systems such as our datapath. However, we find that existing energy estimation tools cannot satisfy both speed and accuracy requirements. They sacrifice one criterion or the other. Therefore, we decided to develop a new simulation-based energy estimation technique, the *net-transition energy model*, described in Chapter 3. The basic idea of this technique is to calculate energy dissipation by using effective capacitance values and transition counts for each node. We can get accurate transition counts from a simulator. The accuracy of this method depends mainly on that of the effective capacitance values. In order to calculate these precisely, we develop a *capacitance merging method*, which calculates transistor capacitances using empirical equations and merges them along with parasitic wire capacitances into one single effective capacitance for each node in the circuit. In Chapter 3, we present results from our evaluation that show close agreement (<8% error) with Hspice measurements for various basic circuit blocks and a 32-bit GCD (Greatest Common Divisor) circuit, which can be regarded as a small version of a datapath. One limitation of our energy modeling is that it ignores the short-circuit energy which accounts for a significant portion (5-10%) of energy consumption in digital CMOS circuitry. We observe that most of short-circuit energy in the datapath is due to inverters, therefore, we try to characterize the short-circuit energy of an inverter with a model which is within 8% error compared to Hspice measurements.

Chapter 4 describes the custom-design of a prototype datapath for a 0.25  $\mu$ m five metal process (from TSMC). We detail the VLSI design style and the floor planning of the datapath. Apart from the flipflops, latches, and muxes, the ALU block is one of main components of the datapath. We discuss our decision of the adder design and develop an area-efficient logic unit design. Also, we explore shifter designs because a shifter is an essential block in a datapath and its simple structure makes energy investigation easy. First, we study dynamic instruction traces to get a better understanding of the role of a shifter in a datapath. Then, we compare a barrel shifter and various logarithmic shifters including our new shifter design, a *split shifter*, in terms of delay and power. We use benchmarks to get more realistic activation patterns for energy analysis. We show that the barrel shifter is a better choice than any log shifter. We include the register file in our energy breakdowns, but the design is taken from earlier work [17].

Finally, in Chapter 5, we analyze the datapath energy using our energy model and benchmarks. We perform energy breakdown by components and show that basic building

blocks such as flipflops, latches, and muxes, account for over half the total energy (56%). We also try energy breakdown by functional blocks and reveal that register file read, bypassing, and the PC generation account for significant portions of the total energy (20%, 22%, and 19% respectively). Also, we develop a novel method that chooses better designs of flipflops and latches in different places of the datapath, based on the data and clock activities. Also, we examine the effect of clock gating and show 25.1% energy reduction by thorough clock gating.

Chapter 6 concludes and summarizes the work herein.

# Chapter 2

# Flipflop, Latch, and Mux

Flipflops, latches, and muxes are the most common blocks in the datapath. Accordingly, their power consumption accounts for a significant portion of total power dissipation. In particular, latches and flipflops have local clocks which burn power every cycle if they are not gated. Therefore, a crucial first-step when we build a low power system is to find flipflops, latches, and muxes which have good energy-delay products. Before building the datapath, we carefully compared various possible design candidates of flipflops, latches, and muxes.

This chapter begins by describing our simulation test bench. Comparisons of flipflops, latches, and muxes in terms of delay, power, and PDP (Power-Delay Product) or EDP (Energy-Delay Product) follow. Stojanovic at al. [15] established a set of rules for consistent estimation of the real performance and power features of the different flipflop structures for fair and realistic comparison. We extend their work to latches and muxes and also introduce new, precise energy comparison methods for flipflops, latches, and muxes.

| Technology:   | TSMC 0.25 $\mu$ m process |

|---------------|---------------------------|

| MOSFET Model: | Level 49 BSIM3 Ver3.1     |

| Conditions:   | Vdd=2.5V, T=25°C          |

Table 2.1: MOS model parameters and conditions.

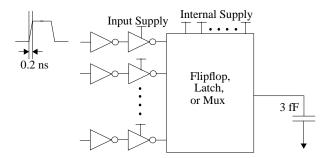

Figure 2-1: Test bench for flipflops, latches, and muxes.

# 2.1 Simulation Test Bench

All experiments were done using Hspice and measurements were made using Hspice's .measure command. Table 2.1 shows the parameters and conditions used in our simulation and Figure 2-1 shows the test bench for simulation. To give more realistic input and clock signals to the circuits, buffers consisting of two cascaded inverters were used. The ideal input and clock signals to the buffers had 0.2 ns rail-to-rail rise/fall times which are typical for the 0.25  $\mu$ m process. We assumed that all input data transitions happen at most once per cycle. For a flipflop, input transitions happen before the primary clock edge (e.g. the rising edge for a positive flipflop) and for a latch, they happen when the latch is transparent. The clock frequency was fixed at 333 MHz which represents around 16 FO4 (fanout-of-4) delays in our process technology. All outputs were loaded with a 3 fF capacitor which is around the same as the capacitance load as four minimum inverters. All cells were optimized to have low power consumption using small-sized transistors. Currents from input and internal supplies were integrated to calculate input and internal energy consumptions.

# 2.2 Flipflop

We chose a set of representative flipflops which can hold their output values when clock is gated (to low value) in an energy saving mode. For this reason, purely dynamic flipflops were excluded from the potential candidates. We experimented with the following flipflops:

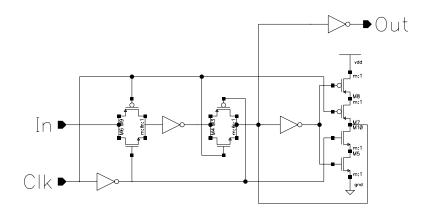

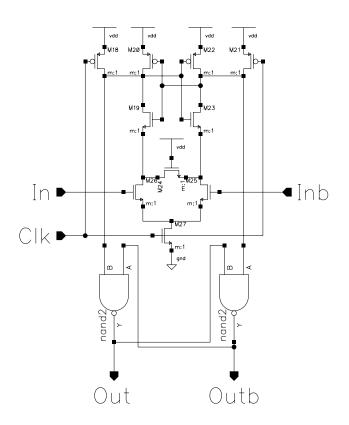

1. Modified PowerPC 603 flipflop: pseudo-static master-slave style. Because it is not fully static, it requires a minimum clock frequency (Figure 2-2), but can hold values

Figure 2-2: Modified PowerPC flipflop.

Figure 2-3: HL flipflop.

indefinitely when clock is gated.

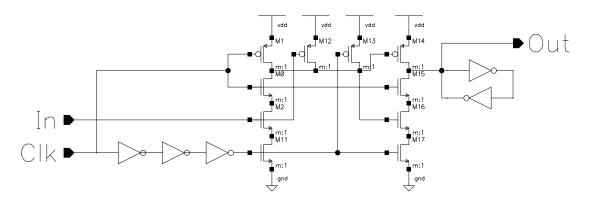

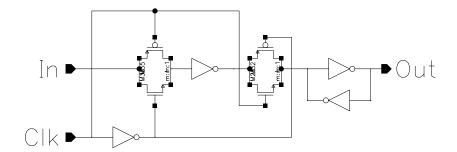

- 2. HLFF flipflop: hybrid style (Figure 2-3).

- 3. StrongArm110 flipflop: differential sense-amplifier based style (Figure 2-4).

- 4. Transmission-gate flipflop: pseudo-static master-slave style with a cross coupled inverter pair to store the output. This also requires a minimum clock frequency (Figure 2-5).

### 2.2.1 Delay

There are many important timing parameters in the flipflop such as Clk-Q delay, D-Q delay, setup time, and hold time. As described in Stojavnovic's paper [15], Clk-Q delay (which is commonly used as a relevant performance parameter) doesn't include setup time, and suffers from the fact that the last transition of input (before the clock) affects Clk-Q delay significantly.

Figure 2-4: StrongArm 110 flipflop.

|                  | min D-Q 1 to 0 (ps) | min D-Q 0 to 1 (ps) | max (ps) |

|------------------|---------------------|---------------------|----------|

| Modified PowerPC | 305.6               | 328.1               | 328.1    |

| HLFF             | 158.6               | 245.6               | 245.6    |

| StrongArm        | 354.8               | 290.6               | 354.8    |

| TG               | 366.5               | 313.4               | 366.5    |

Table 2.2: Minimum D-Q delay measurements of flipflops.

On the other hand, a minimum D-Q delay yields the optimum setup time and the best possible performance [15]. Therefore we chose the minimum D-Q delay as our delay parameter. Table 2.2 shows the delay measurements. We see HLFF is the fastest structure, and the other three flipflops have similar performance. Where speed is the primary concern, HLFF is the best choice.

### 2.2.2 **Power**

There are three major sources of energy consumption in a flipflop: input energy, which represents the energy dissipated to drive the input of the flipflop; internal energy, the energy

Figure 2-5: Transmission-gate flipflop.

dissipated at the internal nodes; and clock energy, the energy dissipated in the local clock buffer driving the clock.

One important fact about the energy dissipation of a flipflop is that it is a function not only of its input data, but also a function of clock activity. Energy can be saved by gating the clock, as is commonly done in modern low-power designs. However, even when the clock is frozen, there is some power dissipation due to input data transitions. Another fact is that the various flipflops in the datapath have significantly different input and clock activity patterns. For example, the flipflops for PC (Program Counter) usually have few input transitions since the PC value changes infrequent in the high order bits but their clocks can rarely be gated. On the other hand, the flipflops which latch the data that will be stored to memory, get input with relatively many transitions. But, because the flipflops are needed only for store instructions, their clocks can be gated most of time. Therefore, we decided to analyze energy consumption for both varying input data and clock activities. This extends the previous work [15] by realizing the importance of clock activity for power consumption, which was overlooked in the previous work. Here, we define input data and clock activities for our convenience as follows: input data activity means the average transitions per cycle of input data, and clock activity is the ratio of the time when the clock is not gated to the total time.

First, we measured energy dissipations for four different input data patterns when the clock activity is 100%. The first sequence (...0101010101...) alternates every cycle, the maximum possible activity, the second sequence (...0110011001...) has one transition every two cycles, and the third sequence (...0000000000...) and the fourth sequence (...1111111111...) have no transitions, that is, the lowest data activity. Also, we experimented with the same data sequences when the clock is frozen. Table 2.3 and Table 2.4 show the measurements of power

|                     | Power(uW)        |       |           |       |

|---------------------|------------------|-------|-----------|-------|

| Input data sequence | Modified PowerPC | HLFF  | StrongArm | TG    |

| 000000000           | 52.6             | 111.4 | 78.9      | 43.5  |

| 1111111111          | 52.9             | 230.0 | 81.2      | 41.9  |

| 0101010101          | 117.5            | 304.1 | 141.6     | 126.8 |

| 0011001100          | 84.4             | 238.8 | 112.5     | 84.8  |

Table 2.3: Power measurements of flipflops (clock activity=1).

|                     | Power(uW)        |      |           |      |

|---------------------|------------------|------|-----------|------|

| Input data sequence | Modified PowerPC | HLFF | StrongArm | TG   |

| 000000000           | 0.0              | 0.0  | 0.0       | 0.0  |

| 1111111111          | 0.0              | 0.0  | 0.0       | 0.0  |

| 0101010101          | 25.4             | 15.5 | 17.9      | 28.2 |

| 0011001100          | 11.5             | 5.8  | 10.2      | 12.2 |

Table 2.4: Power measurements of flipflops (clock activity=0).

dissipation. Table 2.5 and Table 2.6 show the corresponding PDPs for flipflops.

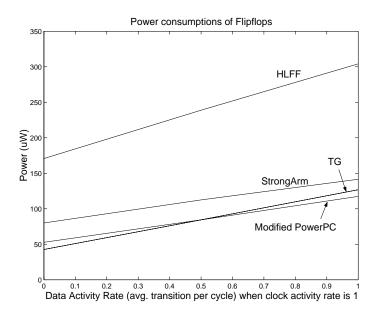

Figure 2-6 shows the power consumptions of flipflops when the clock activity is 1. We notice that power dissipation can be modeled as a linear function of data activity rate (likewise, when the clock activity rate is 0). We can model the power dissipation of a flipflop as f(d, c) (where d and c represent data and clock activity rate). We can get two linear functions of variable d, f(d, 0) and f(d, 1) using the experimental measurements. If clock activity is c (  $0 \le c \le 1$  ), then the clock is on for  $c \cdot TotalTime$  and off for  $(1 - c) \cdot TotalTime$ . Therefore, we can express f(d, c) as the following equation.

$$f(d, c) = c \cdot f(d, 1) + (1 - c) \cdot f(d, 0)$$

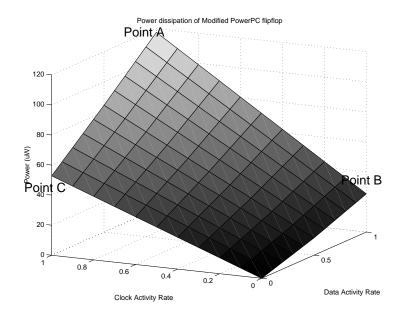

Figure 2-7 shows a 3-dimensional power dissipation graph for the modified PowerPC flipflop which was constructed using the equation. The height represents power dissipation

|                     | PDP (fJ)         |      |           |      |

|---------------------|------------------|------|-----------|------|

| Input data sequence | Modified PowerPC | HLFF | StrongArm | TG   |

| 000000000           | 16.7             | 22.5 | 25.5      | 14.7 |

| 1111111111          | 16.8             | 46.5 | 26.2      | 14.2 |

| 0101010101          | 37.2             | 61.5 | 45.7      | 43.1 |

| 0011001100          | 26.7             | 48.3 | 36.3      | 28.8 |

Table 2.5: PDP of flipflops (clock activity=1).

|                     | PDP (fJ)         |      |           |     |

|---------------------|------------------|------|-----------|-----|

| Input data sequence | Modified PowerPC | HLFF | StrongArm | TG  |

| 0000000000          | 0.0              | 0.0  | 0.0       | 0.0 |

| 1111111111          | 0.0              | 0.0  | 0.0       | 0.0 |

| 0101010101          | 8.1              | 3.1  | 5.8       | 9.6 |

| 0011001100          | 3.6              | 1.2  | 3.3       | 4.2 |

Table 2.6: PDP of flipflops (clock activity=0).

Figure 2-6: Power dissipation of flipflops (clock activity=1).

while the x axis is data activity and the y axis is clock activity. We see it spends the maximum power (Point A) when data and clock activity are both maximum (c = d = 1). Also, as we expected, we notice that there is non-trivial power dissipation if the data activity is high even when the clock is frozen. For example, if data alternates every cycle (d = 1) when clock is off (c = 0), the flipflop spends around 25% of the maximum power (Point B). On the other hand, the flipflop spends over 50% of the maximum power (Point C) even when there is no transition in input data if the clock is left un-gated.

#### 2.2.3 PDP

Figure 2-8 shows PDP graphs for the flipflops. We can see that the modified PowerPC flipflop has the best power-delay product among the various candidates for most of the clock and data patterns. Especially when clock and data activities are both high, the modified PowerPC flipflop

Figure 2-7: Power dissipation of modified PowerPC flipflop.

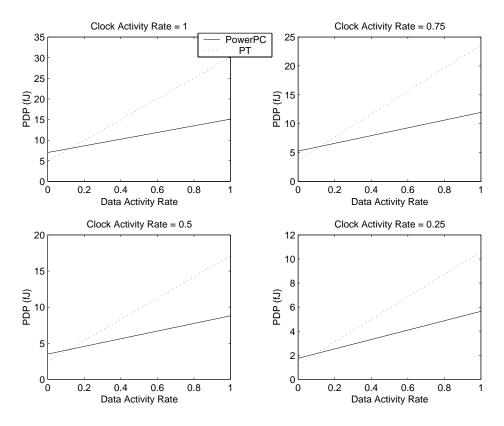

is the most attractive choice. We sliced PDP graphs in order to have a closer look. Figure 2-9 shows the PDP of the flipflops when clock activity rates are 1, 0.75, 0.5, and 0.25. We find that if the data activity rate is less than 0.2, the TG flipflop is a better choice than the modified PowerPC flipflop regardless of clock activity since the TG flipflop has less clock energy. However, the PDP of the TG flipflop increases faster than the others as data activity rate increases. For example, when clock activity rate is 0.25 and data activity rate increases, the TG flipflop falls from the best choice to the worst.

# 2.3 Latch

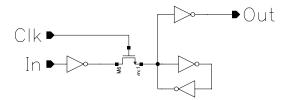

Two popular latches were compared: the PowerPC 603 latch and the Pass-transistor latch. The PowerPC 603 latch is a static latch which uses a transmission-gate as its switch. The Pass-transistor latch is a static latch which has a cross-coupled inverter pair. Both can maintain their output values when their local clocks are gated for saving energy. Figure 2-10 shows the PowerPC 603 MS latch and Figure 2-11 shows the Pass-transistor latch. One problem with the Pass-transistor latch is that the threshold voltage drop across the pass-transistor switch can be fatal if the supply voltage is not high enough.

Figure 2-8: PDP graphs of flipflops.

|                 | PowerPC | PT    |

|-----------------|---------|-------|

| D-Q 1 to 0 (ps) | 197.7   | 311.2 |

| D-Q 0 to 1 (ps) | 184.0   | 251.9 |

| Max D-Q (ps)    | 197.7   | 311.2 |

Table 2.7: D-Q delay measurements of latches.

### 2.3.1 Delay

Among the many timing parameters of a latch, the D-Q delay (the propagation delay from input transition to output transition when a latch is transparent) was chosen as the delay parameter since it best represents the performance (or speed) of the latch. From Table 2.7 we see that the PT latch is slower than the PowerPC latch. In the PT latch, unlike PowerPC latch, there is a conflict between the NMOS and PMOS transistors at the internal node before the output inverter, which harms PT latch performance.

Figure 2-9: PDP of flipflops when clock activity rate is fixed.

|                     | Power(uW) |       | PDP (fJ) |      |

|---------------------|-----------|-------|----------|------|

| Input data sequence | PowerPC   | PTL   | PowerPC  | PTL  |

| 000000000           | 37.4      | 14.8  | 7.1      | 4.2  |

| 1111111111          | 36.3      | 19.8  | 6.9      | 5.6  |

| 0101010101          | 79.2      | 106.9 | 15.1     | 30.1 |

| 0011001100          | 56.5      | 59.3  | 10.8     | 16.7 |

Table 2.8: Power and PDP measurements of latches (clock activity=1).

### 2.3.2 Power

Similar to a flipflop, a latch has three primary sources of power dissipation: input power, internal power, and clock power. We measured the total power consumption with the same input sequences used for the flipflop experiments when clock activity is 1 and 0. Table 2.8 and Table 2.9 show the measurements. The measurements indicate that we can model power dissipation of a latch as a linear function of data activity when clock activity is constant. Also, using the same reasoning as that used for flipflop power modeling, we can estimate the power dissipation of a latch, f(d, c) as  $c \cdot f(d, 1) + (1 - c) \cdot f(d, 0)$ .

Figure 2-10: PowerPC 603 MS latch.

Figure 2-11: Pass-transistor latch.

### 2.3.3 PDP

Figure 2-12 shows PDP graphs of two latches. We can see clearly that the PowerPC latch is a better choice when clock and data activity are high. But if we have a closer look at the PDP graphs (Figure 2-13) we find that the PT latch gives a better power-delay product when data activity is lower than 0.1 regardless of clock activity. This is because most of the power dissipation is clock power when data activity is low and the PT latch spends very little clock power since the clock signal is only connected to one NMOS transistor.

|                     | Power(uW) |      | PDP (fJ) |     |

|---------------------|-----------|------|----------|-----|

| Input data sequence | PowerPC   | PTL  | PowerPC  | PTL |

| 0000000000          | 0         | 0    | 0        | 0   |

| 1111111111          | 0         | 0    | 0        | 0   |

| 0101010101          | 12.9      | 14.4 | 2.5      | 4.1 |

| 0011001100          | 5.7       | 7.4  | 1.1      | 2.1 |

Table 2.9: Power and PDP measurements of latches (clock activity=0).

Figure 2-12: PDP of latches.

## 2.4 Mux

We have experimented with two different muxes: a Transmission-gate (TG) mux, shown in Figure 2-14, and a Pass-transistor (PT) mux, shown in Figure 2-15. The PT mux uses one NMOS pass transistor as a selection switch. Thus, it can't charge up the internal node before the output inverter to Vdd. Accordingly, a small PMOS keeper whose gate is connected to the output and whose drain is connected to the internal node, is needed for full charge.

There are two important timing parameters in a mux design: the D-Q delay and the S-Q delay. The D-Q delay is defined as the propagation delay from the input transition to the resulting output transition while the control signals remain unchanged. The S-Q delay is defined as the propagation delay from the change of the control signals to the resulting output transition while the inputs stay the same.

We identified three main sources of energy dissipation in a mux: pass energy, non-pass energy, and control energy. We define pass energy as the total energy consumption when one input transition goes through a mux and makes an output transition while other inputs and select signals stay the same. Non-pass energy is defined as the energy consumption due to one transition of a not-chosen input. We define control energy as the energy consumption by control signal drivers when there is a change of control signals (while inputs stay the same). Using these components, we can model the average total energy consumption of an N-input mux using the following equation.

Figure 2-13: PDP of latches when clock activity is fixed.

Average Energy Consumption per cycle =  $\alpha$  \* Pass Energy +  $\beta$  \* (N-1) \* Non-pass Energy +  $\gamma$  \* Control Energy

In the equation,  $\alpha$  is the average switching rate of the chosen input,  $\beta$  is that of all the nonchosen inputs and  $\gamma$  is the probability that the mux selects a different input from the previous.

We made the following preliminary assumptions for comparison purpose. We assumed that a mux chooses an input randomly every cycle. Then  $\gamma$  is (N-1)/N. Also, we assumed that all input data are random but change at most once per cycle. Therefore,  $\alpha$  and  $\beta$  are 0.5.

Table 2.10 shows the experimental measurements. First, we notice that the TG mux has less delay and pass energy. The PT mux has a fight between NMOS and PMOS transistors, which the TG mux doesn't have, when discharging the internal node before the output inverter. This harms performance significantly and also results in a fair amount of short-circuit energy loss, which contributes to the larger pass energy. Next, we see that the control energy of the TG mux is around two times bigger than that of the PT mux because the TG mux has an additional PMOS transistor per switch. However, we see that they dissipate similar amounts of non-pass

Figure 2-14: Transmission-gate mux.

Figure 2-15: Pass-transistor mux.

power.

Table 2.11 shows average energy consumption and energy-delay products (EDP) for 2 to 5 input muxes which are typical in the datapath. The average of D-Q delay and S-Q delay was used as delay parameter when we calculated energy-delay products. First, we notice that if the number of inputs are larger than 3, the PT mux consumes less power. As the number of inputs (N) increases from 2 to 5,  $\alpha$  and  $\beta$  remain unchanged, but  $\gamma$  gets larger since there is more

|                      | PT Mux | TG Mux |

|----------------------|--------|--------|

| D to Q delay (ns)    | 0.277  | 0.257  |

| S to Q delay (ns)    | 0.253  | 0.200  |

| Pass Energy (fJ)     | 110.5  | 77.3   |

| Non-pass Energy (fJ) | 22.3   | 23.2   |

| Control Energy (fJ)  | 19.2   | 41.6   |

Table 2.10: Delays and energy consumptions measurements of muxes.

|               | PT Mux      |                      | TG Mux      |                      |

|---------------|-------------|----------------------|-------------|----------------------|

| Num. of input | Energy (fJ) | EDP ( $10^{-24}$ Js) | Energy (fJ) | EDP ( $10^{-24}$ Js) |

| 2             | 76.0        | 20.1                 | 71.1        | 16.2                 |

| 3             | 90.4        | 24.0                 | 89.6        | 20.5                 |

| 4             | 103.1       | 27.3                 | 104.7       | 23.9                 |

| 5             | 115.2       | 30.5                 | 118.3       | 27.0                 |

Table 2.11: Average energy consumptions and EDP (Energy-Delay Product) of muxes.

chance of choosing different inputs. As a result, the portion of control energy to total energy also increases. Therefore, the PT mux which has less control energy, does better than the TG mux when N is large. Likewise, it is expected that the PT mux will spend less power where there are frequent control signal transitions and few input data transitions. However, for EDP, the TG mux is a better choice than the PT mux as seen from the table. For this comparison, we assumed random input data and mux selection. However, in order to make better decisions, we need to find more realistic  $\alpha$ ,  $\beta$ , and  $\gamma$  values from real data statistics.

# Chapter 3

## **Energy Modeling**

This chapter begins by identifying major sources of energy consumption in modern digital CMOS circuits. It is necessary to understand the energy consumption behavior of a circuit before applying low-power techniques. Building a fast and accurate energy estimation model is the first step for low-power design because it allows us to experiment with and evaluate various low-power techniques. We discuss problems of previous energy models and then present and evaluate our energy estimation model, *net-transition energy model*. We describe a short-circuit energy model for an inverter at the end of this chapter.

## 3.1 Sources of Power Dissipation in Digital CMOS Circuits

There are three major sources of power dissipation in a digital CMOS circuit: dynamic switching power due to charging and discharging circuit capacitances, leakage current power including sub-threshold leakage and reverse-biased diode conduction leakage, and short-circuit current power due to finite signal rise/fall times.

Dynamic switching power is the primary source of power dissipation in a digital CMOS circuit; usually it accounts for around 90% of the total power dissipation. It can be modeled as the following equation [4].

$$P = a \cdot c \cdot V_{swing} \cdot V_{dd} \cdot f$$

(a - switching activity, c - effective load capacitance, Vswing - voltage change,

Vdd - source voltage, f - clock frequency)

Vdd and f can be regarded as constant numbers. Vswing is equal to Vdd in most cases where complementary or dynamic CMOS circuit design styles are used. The other terms are not as easy to quantify: c varies according to terminal voltages, rise/fall time, and coupling effects while a is most likely not random in the datapath, and has strong correlations with input vectors.

Short-circuit currents occur because the rise/fall time of input signals are not zero. During the finite rise/fall time, both PMOS and NMOS transistors are turned on, the path between Vdd and GND is connected, and current flows. Usually the short-circuit power dissipation accounts for approximately 5-10% of total power [2].

Leakage current power is significantly smaller than the other sources of power dissipation in normal operation mode, but it can be the dominant component in standby mode. Over time, the threshold voltage in process has been lowered to allow for lower Vdd for less power consumption. As a result, the sub-threshold current, the main component of leakage current, has been increasing rapidly. It is certain that the leakage current power will get more attention in the near future.

## **3.2 Previous Energy Models**

Circuit simulators such as Hspice [11] or Powermill [5] can be used to estimate energy usage. The main advantages of circuit-level simulation are its accuracy and generality [13]. It can estimate the energy consumption of any circuit very precisely regardless of technology, design style, functionality, and architecture. However, it is computationally very expensive and too slow to use for large systems such as our target microprocessor datapath. Therefore, a fast energy estimation model with accuracy comparable to the circuit simulators is needed for research in the design of large low-power systems.

Many approaches have been tried to model energy consumption quickly and accurately. These approaches can be classified into three broad categories: statistical/empirical techniques, probabilistic techniques, and simulation-based techniques [9].

The statistical technique simulates the circuit and measures the power consumption repeatedly with circuit simulators using short random input patterns. When the average of

power measurements converges to a specific value, the simulation stops and the convergence point indicates the average power. This technique was found to be accurate for some logic gates [13]. However, the average power consumption derived from repeated simulations with random sample input patterns, is not meaningful for strongly input-dependent circuits such as a microprocessor. Additionally, the simulation of small input patterns with circuit simulators may take a long time for large systems.

The probabilistic technique is based on the propagation of probabilities. The user provides signal probabilities at the primary inputs and these are propagated into the circuit using Boolean arithmetic and probability theory [13]. Using the probabilities of each node, the average power of the circuit is estimated. It is fast and independent of input data. However, the accuracy of this method is limited by the quality of the input signal probabilities specification and the spatial and temporal correlation model between internal node values.

The simulation-based technique uses high-level simulators such as RTL (Register-Transfer Level) simulators to count circuit node transitions, and calculates energy dissipation from these. It is far more accurate than the previous methods since it is input-dependent and also transition-sensitive. Its accuracy is almost comparable to that of a circuit-level simulator while its speed is 5-7 orders of magnitude faster than that of circuit simulators [8]. However, compared to previous energy models, it is still slower. By developing a fast high-level simulator and trading off the simulation time and accuracy wisely, we can mitigate this disadvantage. Additionally, this technique can provide detailed energy analysis such as spatial and temporal energy breakdowns for real input loads such as SPECint benchmarks easily since it uses a high-level simulator. Therefore we determined that the simulation-based technique is the most appropriate for the study of microprocessor datapath energy consumption. It can give us sufficient accuracy and enough information on many respects of energy consumption.

The most important part of the simulation-based energy model is to get the necessary switching activities. However, getting switching activities is only the first part in the simulation-based technique. The next part is converting them to energy consumption. One possible solution is to make an energy calculation table for each module [19]. Basic blocks are simulated using a circuit simulator for every possible input and internal-state combination, energy consumption is measured, and then the table is constructed. After building an energy table for every block of the system, we can calculate energy consumption by looking up precomputed values in the energy tables. This is accurate because it uses the energy measured from a transistor-level simulator, but it has three obvious disadvantages. First of all, building energy tables is not cheap. It is labor-intensive and time-consuming since we need to simulate every module using every possible input and internal state combination. Second, it is not flexible. If we need to change some features of a circuit block, for example, resizing transistors, we can't help but repeat the whole simulation of that block again in order to update the energy lookup table of the block. Lastly, the table size (accordingly, the simulation time) grows exponentially with the size of the input vector (for example, a 32 bit adder requires  $2^{64}$  table entries.) Clustering algorithms can be used to decrease the size of the energy tables, but they lose a large amount of accuracy (up to 30% [10]).

## **3.3 Node-Transition Energy Model**

We developed a new simulation-based energy model, the *Node-Transition Energy Model*, based on a *capacitance merging method*. The basic idea of our method is simple: If we get the effective, equivalent capacitance,  $C_{eq}$  and the 0-to-1 transition counts of every node, we can calculate the dynamic energy consumption of each node by using the following simple equation. The total energy of a circuit is the sum of the energy dissipation of every node.

Energy Consumption of a node = 0-to-1 Transition Counts  $* C_{eq} * V dd^2$ .

In the following subsections, we first show how we gather transitions counts for all nets. Next, we show how we calculate the accurate, effective capacitance for each net using our *capacitance merging method*. Then, we show how we calculate energy consumption with the transition counts and the effective capacitance using energy equations. Lastly, we evaluate our energy model with sample circuit blocks.

#### **3.3.1** Transition Counts Gathering

An important measurement for our energy model is the transition count. A conventional RTL simulator only counts transitions at registers — not intermediate nodes. This is a limitation

Figure 3-1: A 3-input Transmission-gate mux.

because our energy model requires transition counts for every node including internal nodes in the circuit. However, our simulator, SyCHOSys [8] enables us to gather the transition counts for all interesting nodes in the circuit. First, it is cycle-accurate and it can count and gather transitions on the nets which connect components together directly; that is, the input and output transitions of components. Second, we can add any energy statistics gathering functions to our simulator and the functions calculate and gather the transition counts on all the internal nodes.

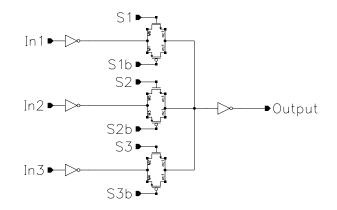

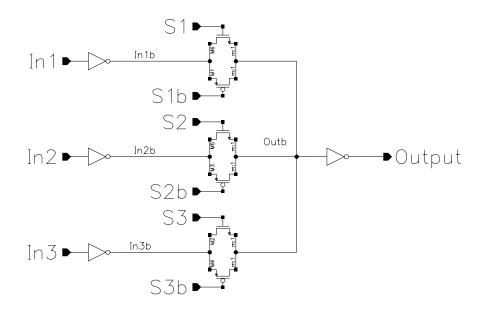

We found that we can factor out many transition counts of internal nodes. First, for simple components such as our buffers and muxes, internal node switchings are the same as input/output transitions. Figure 3-1 shows the schematic of a 3-input transmission-gate mux design. We can see that the transition counts of inlb and outb are the same as those of inl and output respectively since they are connected by inverters, and likewise the transition counts of other internal nodes are the same as those of inputs and output.

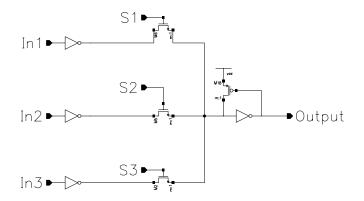

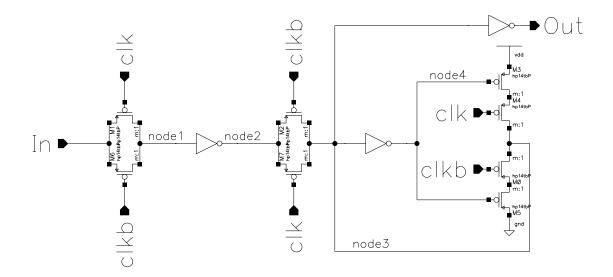

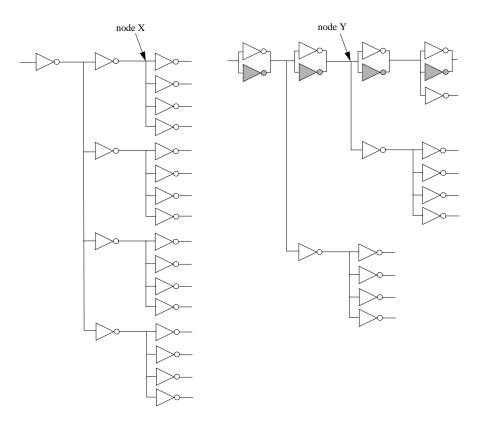

For other blocks such as latches and flipflops, the internal node switchings can also be approximated using input/output transitions. Figure 3-2 shows the schematics of a modified PowerPC-style positive edge-triggered flipflop. We see that the transition counts of node1 and node2 are approximately the same as that of in if we assume that input transitions happen at most once per cycle. Those of node3 and node4 are the same as that of out.

However, for more complicated blocks such as an adder, our simulator, SyCHOSys needs

Figure 3-2: A PowerPC-style flipflop.

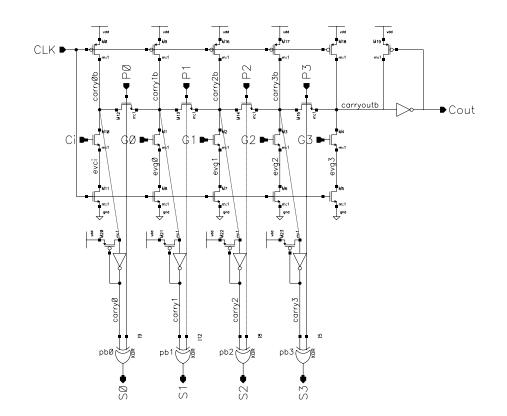

to perform an arithmetic/logical evaluation of input/output in order to obtain the internal node switchings inside the block. For example, when we model our adder, we use bitwise XORs and ANDs of the input vectors to determine the values for P (propagate) and G (generate) while the individual carry values are determined by XOR-ing the adder output with the internal propagate value. For a 32-bit adder, one bit-parallel operation determines a group of corresponding internal nodes simultaneously. By using bit-parallel arithmetic in this way, we can rapidly calculate transitions of all internal nodes. Additionally, the simulator must sometimes count the number of the 1s or 0s instead of transitions in the case of dynamic circuits. For example, a dynamic node, carry0b in Figure 3-3 continues pre-charging and discharging if Ci remains high. We need to count 1s of Ci to determine the transition counts of carry0b.

Since many internal node transitions in a component mirror those of the inputs and outputs, the simulator needs to gather only a fraction of the total statistics. For example, the simulator needed to keep statistics for only 300 nodes in a sample datapath with 1278 nodes in total [8].

### 3.3.2 Capacitance Merging Method

$C_{eq}$  is defined as a single equivalent capacitance to ground for each node. Obtaining an accurate value for  $C_{eq}$  is very crucial for our model since its accuracy is directly related to that of energy

Figure 3-3: A 4-bit Manchester carry chain.

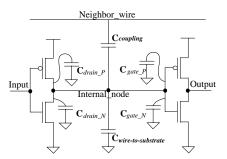

consumption estimation. In CMOS circuits, two kinds of capacitances are connected to a net: transistor capacitance and wire capacitance. Transistor capacitance includes drain (diffusion) capacitance and gate capacitance. Wire capacitance includes wire-to-substrate area/fringe capacitance, and interwire capacitance. Among them, interwire capacitance is hard to estimate since it depends on relative switching of the coupling wires. For example, if the coupling wire has the same signal as the net, the interwire capacitance is zero. On the other hand, if the coupling wire has exactly the opposite signal to the signal of the net, the interwire capacitance is twice bigger than the interwire capacitance when the coupling wire is grounded.

We developed a *capacitance merging method* to estimate  $C_{eq}$  fast and accurately. We obtain  $C_{eq}$  using two phases of calculation. First, the circuit layout is passed to SPACE 2D extractor [18] and it extracts a circuit netlist with accurate parasitic wire capacitances including coupling and fringing wire capacitances. Next, *mergecap*, our custom tool, reads the netlist and sums all transistor gate and drain capacitances, and parasitic wire capacitances connected to each net to give a single effective capacitance for the net.

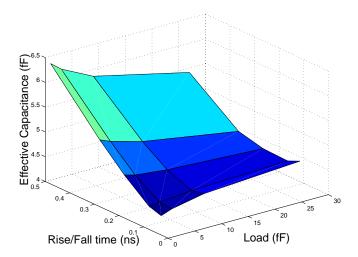

Figure 3-4: Sum of an inverter's PMOS and NMOS drain capacitances.

One complication is that transistor capacitance values vary dynamically depending on terminal voltages. That is, transistor capacitances are not constant values. We experimented with an inverter, varying the rise/fall time of the input and the size of the output load. We could obtain the sum of NMOS and PMOS drain capacitances by measuring the current from source. Figure 3-4 shows the dependency of the drain capacitances on the input rise/fall time and the output load. We see that the maximum (6.35 fF) is 47% bigger than the minimum (4.31fF) in the table. The rise/fall time and the output load determine the change rate of PMOS and NMOS transistors' operating modes during the transition, which result in different effective drain capacitances. Gate capacitances also vary dynamically like drain capacitances. In order to solve this problem, we took advantage of the fact that our design domain is a well-built low-power circuit. A well-built circuit usually has the FO4 (fanout-of-four) characteristics [16]; therefore, we assumed that our circuit has the characteristic FO4 rise/fall time and loads. Therefore, we built FO4 inverter chains and experimented with them to measure realistic gate and drain capacitance coefficients instead of calculating these using equations. The details of this experiment are shown in Section 3.3.3.

Interwire capacitance (coupling wire capacitance) causes another complication. It varies from 0 to twice the static capacitance dynamically depending on the relative timing of signal transitions on coupling wires. A cycle-accurate simulator cannot determine it. Therefore, we made the approximation that the coupled wire is always grounded and simply sum all interwire

Figure 3-5: Schematic of cascaded inverters and the capacitances connected to the internal\_node.

Figure 3-6: Layout of cascaded inverters.

capacitances into a single equivalent capacitance to ground.

For an example of the *capacitance merging method*, we show how we calculate the capacitance of the internal node between two cascaded inverters. Figure 3-5 shows the example circuit and the capacitances connected to the internal node. The layout of two cascaded inverters is shown in Figure 3-6. The corresponding netlist and the extracted capacitance file — the final output of *capacitance merging method* — are shown in Figure 3-7. We see from the netlist that internal\_node has 0.340 fF (= c2 + c5 + c7 + c9 + c11) wire capacitance in total. This value is added to two gate and two drain capacitances obtained using the calibrated gate and drain capacitance coefficients and results in a  $C_{eq}$  of 8.075 fF.

#### 3.3.3 Calibrating Effective Gate and Drain Capacitance

As shown earlier, transistor capacitances are difficult to model because they are voltage dependent. However, exploiting the fact that a well-designed circuit has the natural fanout-of-four (FO4) characteristics, we calibrated effective gate and drain capacitance coefficients.

The basic idea of our method is to calibrate gate and drain capacitance coefficients by experimenting with two kinds of FO4 inverter chains, where inverters are all the same-size:

```

NETLIST :

m1 Vdd1 input internal_node Vdd1 PMOS

+ w=600n l=240n ad=432f as=360f pd=2.04u ps=1.8u

m2 GND1 input internal_node GND NMOS

+ w=600n l=240n ad=432f as=360f pd=2.04u ps=1.8u

m3 output internal_node Vdd1 Vdd1 PMOS

+ w=600n l=240n ad=360f as=432f pd=1.8u ps=2.04u

m4 GND1 internal_node output GND NMOS

+ w=600n l=240n ad=432f as=360f pd=2.04u ps=1.8u

cl GND1 output 34.99428e-18

c2 GND1 internal_node 44.83748e-18

c3 GND1 neighbor_wire 62.31828e-18

c4 GND1 Vdd1 63.218e-18

c5 input internal_node 73.79929e-18

c6 input neighbor_wire 43.82269e-18

c7 neighbor_wire internal_node 121.0628e-18

c8 neighbor_wire Vdd1 62.31828e-18

c9 output internal_node 55.8099e-18

c10 output Vdd1 34.99428e-18

cll Vddl internal node 44.83748e-18

```

```

CAPACITANCE FILE :

cap_input 3.203 fF

cap_internal_node 8.075 fF

cap_output 4.775 fF

cap_neighbor_wire 0.290 fF

```

Figure 3-7: The netlist and the capacitance file of a cascaded two inverters.

Figure 3-8: Two FO4 inverter chains.

a normal FO4 inverter chain and a modified FO4 inverter chain with slightly different FO4 characteristics. Exploiting the slight difference, we could calibrate the coefficients.

Figure 3-8 shows these two inverter chains. We see that four NMOS gates, four PMOS gates, one NMOS drain, and one PMOS drain are connected to node X. Likewise, three NMOS gates, three PMOS gates, two NMOS drains, and two PMOS drains are connected to node Y. We assumed that one NMOS gate and one PMOS gate capacitance are comparable to one NMOS drain and one PMOS drain capacitance. (If this assumption doesn't hold, the modified chain will lose the FO4 characteristic.)

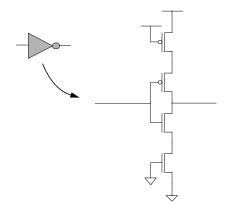

The gray inverter is intentionally turned off since we wanted to keep the same amount of driving power as the normal FO4 inverter chain. It is shown in Figure 3-9. Therefore, we can expect that both nodes have similar but different FO4 rise/fall times. Energy consumptions of node X and node Y were measured and, from them, effective capacitances of the nodes were calculated.

We assumed that NMOS and PMOS gate and drain capacitances are linear functions of the

Figure 3-9: Gray inverter.

transistor widths since the length of transistors is usually set to the minimum value in digital CMOS circuits. The following are the functions and coefficients used:

PMOS gate capacitance = gp \* PMOS width PMOS drain capacitance = dp \* PMOS width NMOS gate capacitance = gn \* NMOS width NMOS drain capacitance = dn \* NMOS width

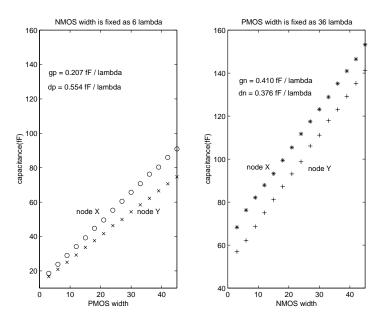

In order to derive gp and dp coefficients, we measured the capacitances of node X and node Y while varying PMOS width with a fixed NMOS width. The left graph of Figure 3-10 shows the measurements. We can see that the capacitances of both nodes are linearly proportional to the PMOS width, but the slopes of the two functions are slightly different. The linearity of the two functions validates our assumption that the gate and drain capacitances can be modeled as linear equations. Also, the slight difference validates our assumption that the two chains have similar FO4-like characteristic. Using our linear capacitance equations, we could calculate the capacitances of the node X and the node Y as follows. (Here,  $P_w$  and  $N_w$  represent PMOS width and NMOS width respectively.)

$$\begin{aligned} Capacitance(nodeX) &= 4 \cdot gp \cdot P_w + 4 \cdot gn \cdot N_w + dp \cdot P_w + dn \cdot N_w \\ &= (4 \cdot gp + dp) \cdot P_w + (4 \cdot gn \cdot N_w + dn \cdot N_w) \\ Capacitance(nodeY) &= 3 \cdot gp \cdot P_w + 3 \cdot gn \cdot N_w + 2 \cdot dp \cdot P_w + 2 \cdot dn \cdot N_w \end{aligned}$$

Figure 3-10: Deriving gp, dp, gn and dn from measurements.

$$= (3 \cdot gp + 2 \cdot dp) \cdot P_w + (3 \cdot gn \cdot N_w + 2 \cdot dn \cdot N_w)$$

Since the NMOS width is fixed, the slope of the node X plot is  $4 \cdot gp + dp$  and that of the node Y plot is  $3 \cdot gp + 2 \cdot dp$ . After getting the slopes using the linear-square method from the measurements, we can derive gp and dp by solving linear equations. The results are shown in the left Figure 3-10.

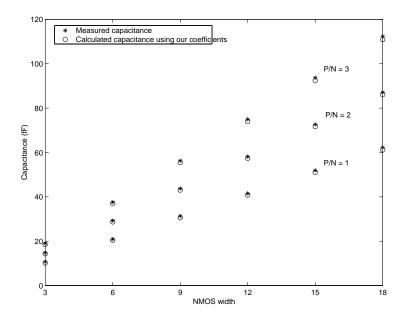

In the same way, we can derive *gn* and *dn* using the measurements where PMOS width is fixed, as shown in the right graph of Figure 3-10. In order to verify the derived capacitance coefficients, we calculated the capacitance of node X for different PMOS and NMOS widths and compared these values with the empirically measured capacitances obtained using Hspice. Figure 3-11 shows that the calculated capacitances match the measured ones well. The relative error is within 5% for 18 different NMOS and PMOS widths.

The entire measuring process is done automatically and only needs to be done once for a given process technology.

Figure 3-11: Verification of gate and drain capacitance coefficients. P/N is the ratio of PMOS width to NMOS width.

#### **3.3.4 Energy Calculation**

Energy calculation is divided into two parts: external and internal. External energy is defined as the energy dissipated on the nets which connect components together, and is modeled for each net as the effective capacitance times the transition counts times  $V_{dd}^2$ . Internal energy is the energy dissipated inside components. Each component has its own internal energy equation which calculates the energy consumption using effective capacitances of all internal nodes and internal statistics as described above. While a layout is required for external capacitance, the internal effective capacitances are independent of the specific layout, and can be determined once when the component is designed. Figure 3-12 shows energy equations for a 32-bit 3input mux, a 32-bit positive-edge triggered flipflop, and a 4-bit Manchester carry chain (an adder block for our 32-bit carry skip adder, as shown in Figure 3-3). In the equations, each prefix cap, tran, and one represents the effective capacitances, the transition counts, and the 1s counts respectively. We see that the energy equations directly reflect the structure and the circuit style of a circuit.

```

N bit 3-Input Mux :

(tran_in1[N-1:0], tran_in2[N-1:0], tran_in3[N-1:0], tran_out[N-1:0],

cap_in1b, cap_in2b, cap_in3b, cap_outb) {

for (i=0;i<N;i++)</pre>

internal_energy += Vdd^2 * (tran_in1[i] * cap_in1b +

tran_in2[i] * cap_in2b +

tran_in3[i] * cap_in3b +

tran_out[i] * cap_outb);

}

N bit Positive-edge triggered Flipflop :

(tran_in[N-1:0], tran_out[N-1:0], cap_node1, cap_node2, cap_node3,

cap_node4) {

for (i=0;i<N;i++)</pre>

internal_energy +=

Vdd^2 * (tran_in[i] * (cap_node1 + cap_node2) +

tran_out[i] * (cap_node3 + cap_node4));

}

4 bit Manchester Carry Chain :

(tran_p[3:0], one_g[3:0], one_carry[3:0], one_carryout, cap_pb[3:0],

cap_ev[3:0], cap_carry[3:0], cap_carryb[3:0],

cap_carryout, cap_carryoutb) {

for (i=0;i<4;i++) {

internal_energy += Vdd^2 * tran_p[i] * cap_pb[i];

internal_energy += Vdd^2 * one_g[i] * cap_ev[i];

internal_energy +=

Vdd^2 * one_carry[i] * (cap_carry[i] + cap_carryb[i]));

}

internal_energy

+= Vdd<sup>2</sup> * one_carryout * (cap_carryout + cap_carryoutb);

}

```

Figure 3-12: Energy equations of N bit 3-input mux, N-bit positive flipflop, and 4-bit Manchester carry chain.

Figure 3-13: Mux, latch, flipflop and mux-latch: measured energy vs. estimated energy. Ideally, all points should fall on the line.

### **3.3.5** Evaluation of Our Energy Model

We first evaluated our energy model using small circuit examples. Figure 3-13 shows the estimated energy consumption using the *net-transition energy model* (X-axis) versus the measured energy consumption using Hspice (Y-axis) for a mux, a latch, a flipflop, and a mux-latch circuit, where the output of the mux is connected to the latch input.

We used the typical FO4 rise and fall times and output load for the simulation. We chose 5 random input patterns for each circuit. We found that the maximum relative errors are 4.76%, 2.36%, 8.02%, and 4.32% for the mux, the latch, the flipflop and the mux-latch circuits respectively. We see that the errors are of the same order of magnitude as those of the gate and drain capacitance coefficients.

For a larger example, we used the 32-bit GCD (Greatest Common Divisor) circuit. The circuit implements Euclid's GCD algorithm. The GCD circuit is a small version of a CPU datapath in the sense that it has muxes, latches, flipflops and an adder. Our energy model could estimate energy dissipations within 7% error compared to Hspice simulation for 7 different input test vectors [8].

Our method has three advantages over other simulation-based energy estimation tools. First, it is fast. The total time needed for energy calculation depends mainly on the running time of the cycle-accurate simulator (with statistics gathering code). The time needed for merging capacitances and calculating energy equations are very little compared to the simulation time. Our simulator, SyCHOSys [8] was fast enough to simulate a billion cycles of benchmark programs per day. Second, it is flexible. For example, if we change a mux design, we need to do only two things. We need to get the capacitance values from the layout of the new mux design, which can be done automatically after the layout is ready, and we need to modify the energy equation if the internal structure of the new mux is different from the old. Third, it is accurate. A cycle-accurate simulation-based technique is the most accurate of the three categories of energy estimation techniques. Additionally, our detailed energy equations and realistic effective capacitance values guarantee the accurate energy estimation. The verification of our method with some examples will be shown in section 3.3.5.

One limitation of our method is that it can't model glitch power since it is only cycleaccurate. But, we can assume that for a well-built low-power circuit, glitches are rare and small. Another limitation is that it deals with only dynamic switching energy, but ignores short-circuit and leakage energy. Lastly, if we substitute a block with another block which executes the same function, but requires different internal statistics from a simulator, we have to re-simulate.

## 3.4 Short-Circuit Energy Modeling of an Inverter

Short-circuit energy accounts for a significant portion (5-10%) of the total power consumption in CMOS circuits. However, our energy model, the *Net-Transition Energy Model*, did not include the short-circuit energy. Therefore, we tried to model the short-circuit energy to be included in the next version of the *net-transition energy model*.

Short-circuit energy is difficult to model in general since it varies dynamically depending on the on-time of the transistors and their operating modes. Also, the relative switching time of multiple inputs to a logic gate further complicates the problem. However, we observed that most of the short-circuit power in our design is consumed in inverters since they are the most common components in complementary static CMOS circuits (transmission-gate and dynamic circuits don't dissipate short-circuit power). For example, our latches, buffers, muxes, and

Figure 3-14: Two kinds of short circuit current.

flipflops dissipate short-circuit power only in their inverters. Modeling the short-circuit energy of an inverter is relatively easy since it has only one input and no internal nodes. In addition, the inverter is most likely to have the short-circuit current (every transition), compared to more complex gates such as three-input NANDs. Thus, if we can calibrate the short-circuit energy loss per transition for a given inverter strength, transition counts are enough to calculate the total short-circuit energy of inverters.

The basic intuition of our model is that if all transistors scale the same, then the rise/fall time remains constant since strength of the transistors and the load capacitance scale proportionally to the transistor sizes. Short-circuit current is proportional to the rise/fall time and the the strength of the transistors. Therefore, the average short-circuit power scales linearly with the transistor size. Using this intuition, when the ratio of PMOS width to NMOS width (P/N) is fixed, the short-circuit energy of an inverter can be modeled as a linear function of NMOS width.

## Short-circuit energy per transition = *Ratio constant* \* NMOS width + *Base energy* (P/N is fixed)

We define two kinds of short-circuit energy for inverters: Rise short-circuit energy and fall short-circuit energy (Figure 3-14). Rise short-circuit energy is the energy dissipation due to the current from output to GND when the output goes from low to high and fall short-circuit energy is the energy dissipation due to the current from Vdd to output when there is an output transition from high to low.

For our test bench, we used an FO4 inverter chain whose inverters are all the same size, in order to represent the typical FO4 environment of a well-built low-power datapath. We used

Figure 3-15: Measurements of fall short-circuit energy for various inverters.

inverters which have ratios between 1/1 and 5/1 since they are typical in CMOS digital circuits. We measured rise and fall short-circuit energy while varying PMOS and NMOS widths and derived *Ratio constant* and *Base energy* for various ratios of PMOS width to NMOS width using a linear least square method.