| Feedback                                                                |   |

|-------------------------------------------------------------------------|---|

| • Good                                                                  |   |

| Entire flow of CAD                                                      |   |

| Real world perspective                                                  |   |

| Examples of algorithms                                                  |   |

| <ul> <li>Class structure → problem → formulation → algorithm</li> </ul> |   |

| No homework                                                             |   |

| <ul> <li>Dialog with class/ "Socratic approach"</li> </ul>              |   |

| • Bad                                                                   |   |

| No homework                                                             |   |

| <ul> <li>Questions to class sometimes unclear</li> </ul>                |   |

| Too fast, need more details                                             |   |

| <ul> <li>Energy of lecture up and down some days</li> </ul>             |   |

| Actually, this was last year's feedback!!!                              | 2 |

### Feedback – this year

- Good

- Entire flow of CAD

- Real world perspective

- Examples of algorithms

- Good slides

- No homework

- Questions invited in class

- Bad

- No homework

- Too fast, need more details more examples of algorithms

- Slides not updated on webpage before class slides don't match the lecture

- Can't see fonts on slides

- Don't know what to read before class

3

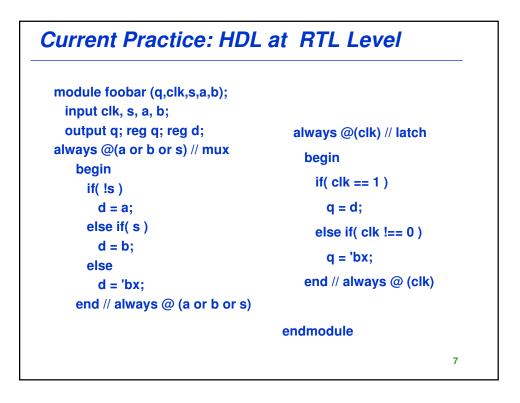

## Types of software simulators

- Circuit simulation

- Spice, Advice, Hspice

- Timemill + Ace, ADM

- Event-driven gate/RTL/Behavioral simulation

- Verilog VCS, NC-Verilog, Turbo-Verilog, Verilog-XL

- VHDL VSS, MTI, Leapfrog

- Cycle-based gate/RTL/Behavioral simulation

- Verilog Frontline, Speedsim

- VHDL Cyclone

- Domain-specific simulation

- SPW, COSSAP

- Architecture-specific simulation

| che Switch<br>che lgate |

|-------------------------|

| che loff                |

| re Switch<br>re Igate   |

| re loff<br>bias         |

| Dias<br>AP Ikg          |

|                         |

|                         |

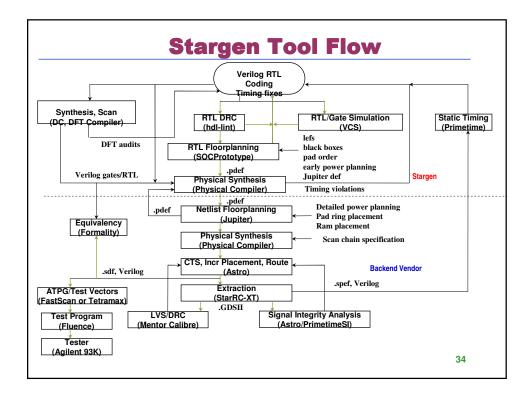

| RTL creation, checking, debugging                 | Emacs, vi, Everest HDL-Lint, Novas Debussy             |

|---------------------------------------------------|--------------------------------------------------------|

| Verilog simulation/testbench                      | Synopsys VCS, VERA                                     |

| RTL floorplanning                                 | Icinergy SOCPrototype                                  |

| Logic synthesis<br>Physical synthesis             | Synopsys Design Compiler<br>Synopsys Physical Compiler |

| Static timing analysis                            | Primetime                                              |

| Design for test analysis and scan chain insertion | Synopsys DFT Compiler or Mentor DFT Adviso             |

| Gate netlist floorplanning                        | Synopsys (Avanti) Jupiter                              |

| Clock tree synthesis, routing                     | Synopsys (Avanti) Astro                                |

| Extraction                                        | Synopsys (Avanti) Star-RCXT                            |

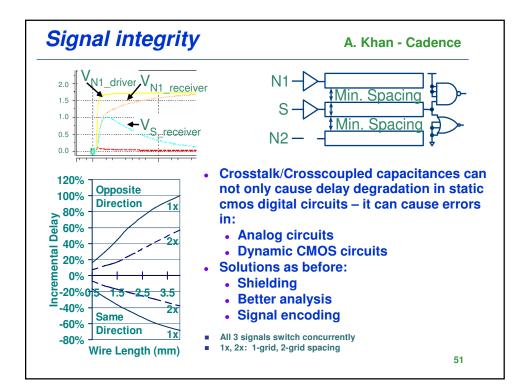

| Signal integrity                                  | PrimetimeSI, AstroXTalk, AstroRail                     |

| DRC/LVS                                           | Mentor Calibre                                         |

| Equivalency checking                              | Synopsys Formality                                     |

| Memory BIST                                       | TBD Tools                                              |

| ATPG, IEEE1149                                    | TBD Tools                                              |

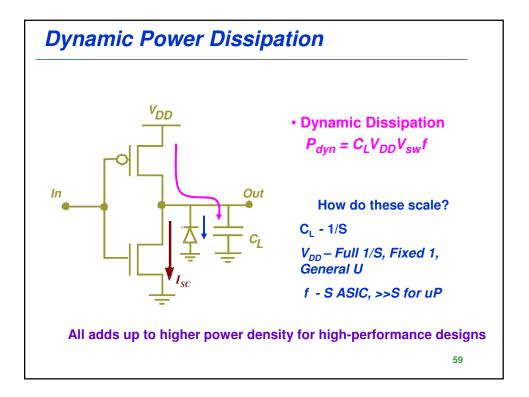

| Parameter                       | Relation                           | Full<br>Scaling  | General<br>Scaling | Fixed Voltage<br>Scaling |

|---------------------------------|------------------------------------|------------------|--------------------|--------------------------|

| W, L, t <sub>ox</sub>           |                                    | 1/S              | 1/S                | 1/S                      |

| $V_{DD}, V_T$                   |                                    | 1/S              | 1/U                | 1                        |

| N <sub>SUB</sub>                | V/W <sub>depl</sub> <sup>2</sup>   | S                | S <sup>2</sup> /U  | S <sup>2</sup>           |

| Area/Device                     | WL                                 | 1/S <sup>2</sup> | 1/S <sup>2</sup>   | 1/S <sup>2</sup>         |

| Cox                             | 1/t <sub>ox</sub>                  | S                | S                  | S                        |

| CL                              | CoxWL                              | 1/S              | 1/S                | 1/S                      |

| k <sub>n</sub> , k <sub>p</sub> | C <sub>ox</sub> W/L                | S                | S                  | S                        |

| Iav                             | k <sub>n,p</sub> V <sup>2</sup>    | 1/S              | S/U <sup>2</sup>   | S                        |

| t <sub>p</sub> (intrinsic)      | C <sub>L</sub> V / I <sub>av</sub> | 1/S              | U/S <sup>2</sup>   | 1/S <sup>2</sup>         |

| Pav                             | $C_L V^2 / t_p$                    | 1/S <sup>2</sup> | S/U <sup>3</sup>   | S                        |

| PDP                             | $C_L V^2$                          | 1/S <sup>3</sup> | $1/SU^2$           | 1/S                      |

| Table 3.                        | 1: Scaling Rel                     | ationships f     | or Long Cha        | nnel Devices             |

|                                  |                                    |                  | Weste &            | Harris – CMOS VL         |

|----------------------------------|------------------------------------|------------------|--------------------|--------------------------|

| Parameter                        | Relation                           | Full<br>Scaling  | General<br>Scaling | Fixed Voltage<br>Scaling |

| W, L, t <sub>ox</sub>            |                                    | 1/S              | 1/S                | 1/S                      |

| V <sub>DD</sub> , V <sub>T</sub> |                                    | 1/S              | 1/U                | 1                        |

| N <sub>SUB</sub>                 | V/W <sub>depl</sub> <sup>2</sup>   | S                | S²/U               | S <sup>2</sup>           |

| Area/Device                      | WL                                 | 1/S <sup>2</sup> | 1/S <sup>2</sup>   | 1/S <sup>2</sup>         |

| Cox                              | 1/t <sub>ox</sub>                  | S                | S                  | S                        |

| CL                               | C <sub>ox</sub> WL                 | 1/S              | 1/S                | 1/S                      |

| k <sub>n</sub> , k <sub>p</sub>  | C <sub>ox</sub> W/L                | S                | S                  | S                        |

| Iav                              | k <sub>n,p</sub> V <sup>2</sup>    | 1/S              | S/U <sup>2</sup>   | S                        |

| t <sub>p</sub> (intrinsic)       | C <sub>L</sub> V / I <sub>av</sub> | 1/S              | U/S <sup>2</sup>   | 1/S <sup>2</sup>         |

| Pav                              | $C_L V^2 / t_p$                    | 1/S <sup>2</sup> | S/U <sup>3</sup>   | S                        |

| PDP                              | $C_L V^2$                          | 1/S <sup>3</sup> | $1/SU^2$           | 1/S                      |

| Table 3.                         | 1: Scaling Rel                     | ationships f     | or Long Cha        | nnel Devices             |

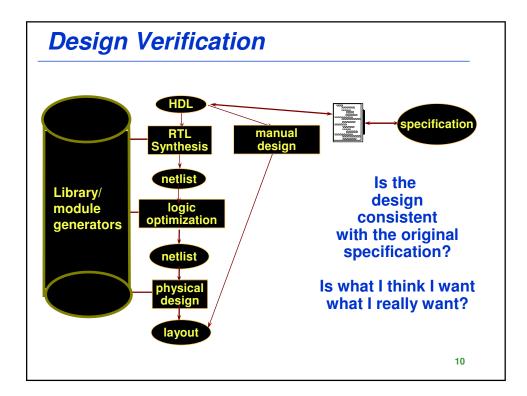

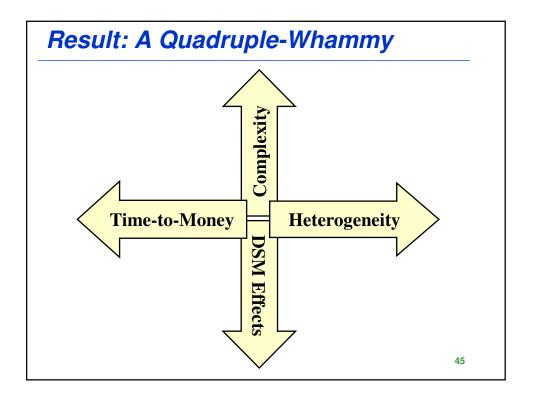

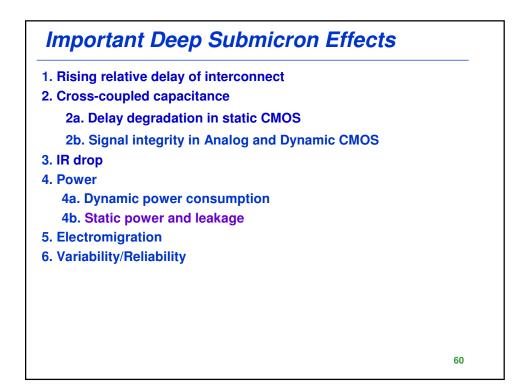

| DSM Effects                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>During the golden era of ASIC (3.5u to .18u) there was little<br/>concern for physical effects during design.</li> </ul>                                                                           |

| Area                                                                                                                                                                                                        |

| Delay                                                                                                                                                                                                       |

| Power                                                                                                                                                                                                       |

| <ul> <li>Were all relatively predictable and insurable</li> </ul>                                                                                                                                           |

| • With smaller geometries (.18u and below) physical effects began to demand greater and greater attention in design. Basic design parameters were neither predictable or insurable                          |

| <ul> <li>But moving higher in the design hierarchy (RTL → Behavioral →<br/>"System-level") requires building on top of predictable layers</li> </ul>                                                        |

| <ul> <li>As a result the design process has been stalled at the RTL level as<br/>we try to bring netlist implementation back to the predictability and<br/>reliability that we had 20 years ago!</li> </ul> |

| <ul> <li>Focus of research in the RTL design flow has been on managing<br/>these DSM effects</li> </ul>                                                                                                     |

| these DSM effects                                                                                                                                                                                           |

| 68                                                                                                                                                                                                          |

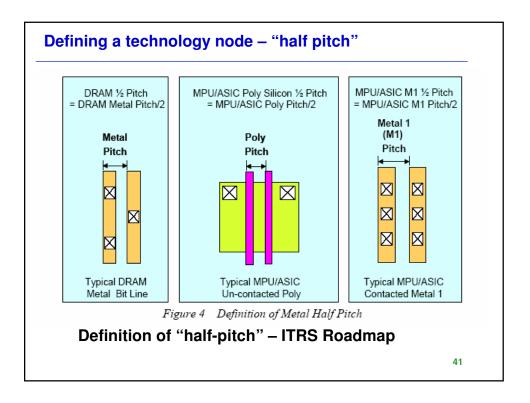

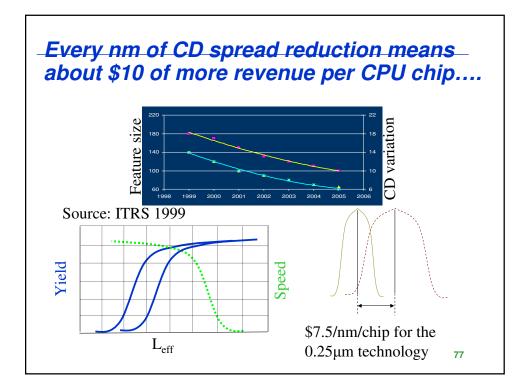

# SIA thinks that CD should be allowed a 10% error budget – why?

| Year<br>Technology Node                  | 1999<br>180 nm | 2000 | 2001 | 2002<br>130 nm | 2003 | 2004 | 2005<br>100 nm |

|------------------------------------------|----------------|------|------|----------------|------|------|----------------|

| DRAM                                     |                |      |      |                |      |      | 1              |

| Half pitch (nm)                          | 180            | 165  | 150  | 130            | 120  | 110  | 100            |

| Contacts (nm)                            | 200            | 185  | 170  | 150            | 145  | 140  | 130            |

| Overlay (nm, mean + 3 sigma)             | 65             | 58   | 52   | 45             | 42   | 38   | 35             |

| CD control (nm, 3 sigma, post-etch)      | 18             | 17   | 15   | 13             | 12   | 11   | 10             |

| MPU                                      |                |      |      |                |      |      |                |

| Half pitch                               | 230            | 210  | 180  | 160            | 145  | 130  | 115            |

| Gate length (nm, in resist)              | 140            | 120  | 100  | 90             | 80   | 70   | 65             |

| Gate length (nm, post-etch)              | 140            | 120  | 100  | 90             | 80   | 70   | 65             |

| Contacts (nm, in resist)                 | 230            | 210  | 180  | 160            | 145  | 130  | 115            |

| Gate CD control (nm, 3 sigma, post-etch) | 14             | 12   | 10   | 9              | 8    | 7    | 6              |

|                                          |                |      |      |                |      |      |                |

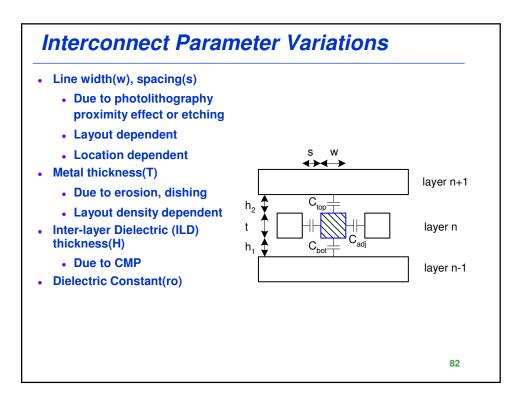

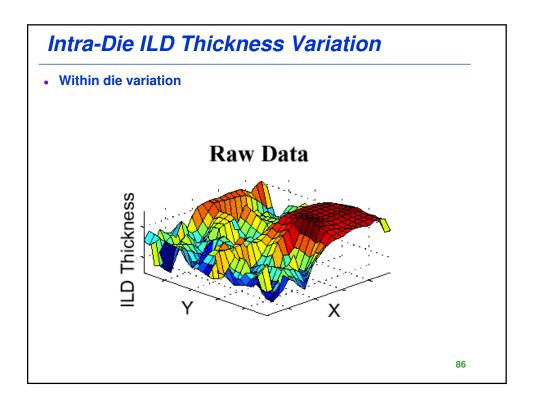

## **ILD Thickness Variation**

#### • TSMC specs on ILD Variation

• Variation is up to 20%

#### • Modest (3% ?) impact on timing

| iel | ecti | rie l | laye | rs |

|-----|------|-------|------|----|

|     |      |       |      |    |

| Dielectric | Thickness | %Var   | Dielectric constant | Comments            |

|------------|-----------|--------|---------------------|---------------------|

| FOX        | 3500 🗆    | ±17.1% | 3.9                 |                     |

| ILD        | 7000 🗆    | ±21.4% | 4.0                 | See NOTE 1.         |

| IMD1a      | 11300 🗆   | ±20%   | 3.7                 | See NOTE 1.         |

| IMD1b      | 2000 🗆    | ± 3%   | 4.2                 |                     |

| IMD2a      | 11300 🗆   | ± 20%  | 3.7                 | See NOTE 1.         |

| IMD2b      | 2000 🗆    | ± 3%   | 4.2                 |                     |

| IMD3a      | 11300 🗆   | ±20%   | 3.7                 | See NOTE 1.         |

| IMD3b      | 2000 🗆    | ± 3%   | 4.2                 |                     |

| IMD4a      | 11300 🗆   | ±20%   | 3.7                 | See NOTE 1.         |

| IMD4b      | 2000 🗆    | ± 3%   | 4.2                 |                     |

| IMD5a      | 11300 🗆   | ±20%   | 3.7                 | See NOTE 1.         |

| IMD5b      | 2000 🗆    | ± 3%   | 4.2                 |                     |

| PASS1      | 10000 🗆   | ±10%   | 4.2                 | See NOTE 2.         |

| PASS2      | 7000 🗆    | ±10%   | 7.9                 | Conformal material. |

are overetched 1000