## **Distributed Memory Multiprocessors**

CS 252, Spring 2005 David E. Culler Computer Science Division U.C. Berkeley

### **Fundamental Issues**

- · 3 Issues to characterize parallel machines

- 1) Naming

- 2) Synchronization

- 3) Performance: Latency and Bandwidth (covered earlier)

/1/05

CS252 s05 smp

## Fundamental Issue #1: Naming

- · Naming:

- what data is shared

- how it is addressed

- what operations can access data

how processes refer to each other

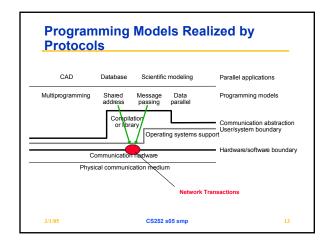

- Choice of naming affects code produced by a compiler; via load where just remember address or keep track of processor number and local virtual address for msg. passing

- Choice of naming affects replication of data; via load in cache memory hierarchy or via SW replication and consistency

3/1/05

CS252 s05 smp

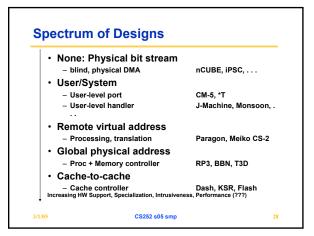

## Fundamental Issue #1: Naming

- Global physical address space: any processor can generate, address and access it in a single operation

- memory can be anywhere:

virtual addr. translation handles it

- Global virtual address space: if the address space of each process can be configured to contain all shared data of the parallel program

- Segmented shared address space: locations are named

3/1/05

CS252 s05 smp

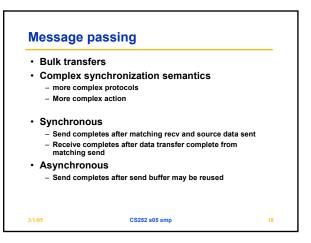

## Fundamental Issue #2: Synchronization

- · To cooperate, processes must coordinate

- Message passing is implicit coordination with transmission or arrival of data

- · Shared address

=> additional operations to explicitly coordinate: e.g., write a flag, awaken a thread, interrupt a processor

3/1/05

CS252 s05 smp

## **Challenges (cont)**

- Fetch Deadlock

- For network to remain deadlock free, nodes must continue accepting messages, even when cannot source msgs

- what if incoming transaction is a request?

- » Each may generate a response, which cannot be sent!

- » What happens when internal buffering is full?

- logically independent request/reply networks

- physical networks

- virtual channels with separate input/output queues

- · bound requests and reserve input buffer space

- K(P-1) requests + K responses per node

- service discipline to avoid fetch deadlock?

- · NACK on input buffer full

- NACK delivery?

CS252 s05 smp

s05 smp

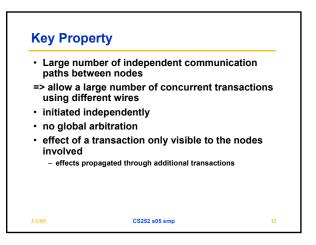

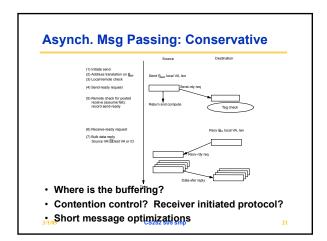

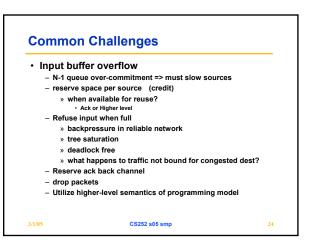

## Challenges in Realizing Prog. Models in the Large

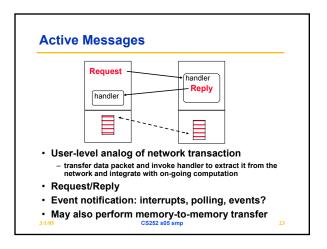

- · One-way transfer of information

- · No global knowledge, nor global control

- barriers, scans, reduce, global-OR give fuzzy global state

- · Very large number of concurrent transactions

- · Management of input buffer resources

- many sources can issue a request and over-commit destination before any see the effect

- Latency is large enough that you are tempted to "take risks"

- optimistic protocols

- large transfers

- dynamic allocation

- Many many more degrees of freedom in design

- and engineering of these system

26

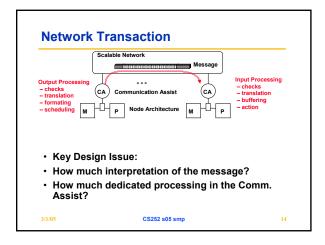

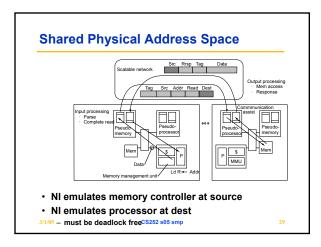

## Network Transaction Processing Output Processing - checks - check

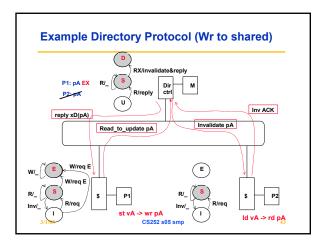

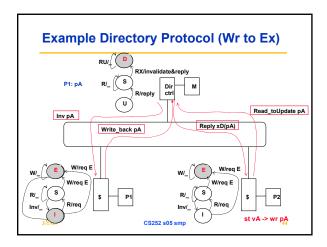

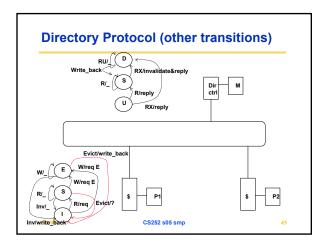

# A Cache Coherent System Must: • Provide set of states, state transition diagram, and actions • Manage coherence protocol • (0) Determine when to invoke coherence protocol • (a) Find info about state of block in other caches to determine action » whether need to communicate with other cached copies • (b) Locate the other copies • (c) Communicate with those copies (inval/update) • (0) is done the same way on all systems • state of the line is maintained in the cache • protocol is invoked if an "access fault" occurs on the line • Different approaches distinguished by (a) to (c)

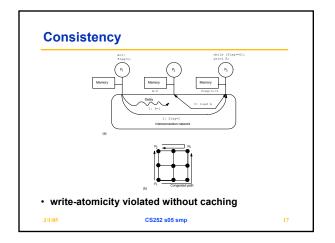

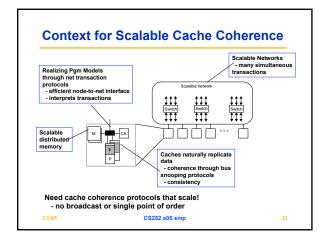

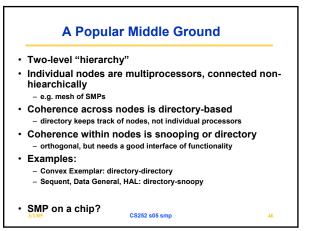

## All of (a), (b), (c) done through broadcast on bus - faulting processor sends out a "search" - others respond to the search probe and take necessary action Could do it in scalable network too - broadcast to all processors, and let them respond Conceptually simple, but broadcast doesn't scale with p - on bus, bus bandwidth doesn't scale - on scalable network, every fault leads to at least p network transactions Scalable coherence: - can have same cache states and state transition diagram - different mechanisms to manage protocol

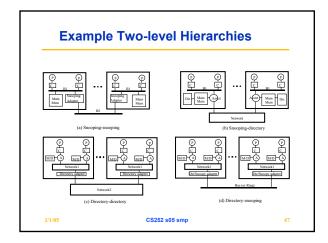

## One Approach: Hierarchical Snooping

- · Extend snooping approach: hierarchy of broadcast media

- tree of buses or rings (KSR-1)

- processors are in the bus- or ring-based multiprocessors at the leaves

- parents and children connected by two-way snoopy interfaces

- » snoop both buses and propagate relevant transactions

main memory may be centralized at root or distributed among leaves

- Issues (a) (c) handled similarly to bus, but not full broadcast

- faulting processor sends out "search" bus transaction on its bus

- propagates up and down hiearchy based on snoop results

- · Problems:

- high latency: multiple levels, and snoop/lookup at every level

- bandwidth bottleneck at root

- Not popular today

3/1/05

CS252 s05 smp

37

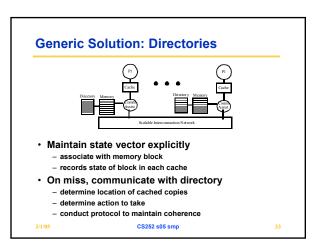

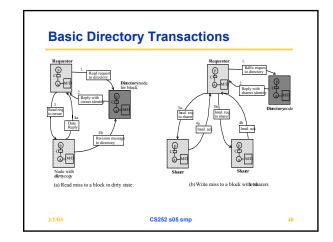

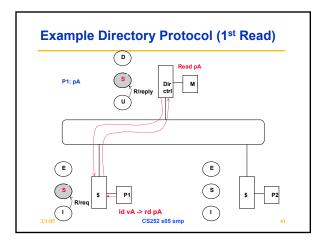

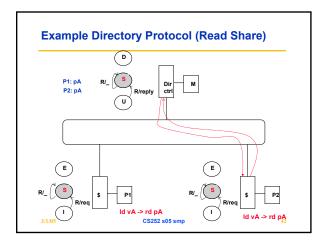

## **Scalable Approach: Directories**

- Every memory block has associated directory information

- keeps track of copies of cached blocks and their states

- on a miss, find directory entry, look it up, and communicate only with the nodes that have copies if necessary

- in scalable networks, communication with directory and copies is through network transactions

- Many alternatives for organizing directory information

1/05

CS252 s05 smp

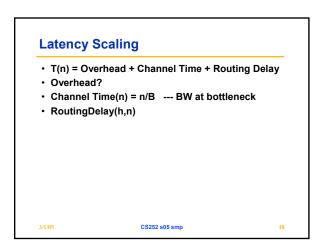

## **Typical example**

- · max distance: log n

- number of switches:  $\alpha$  n log n

- overhead = 1 us, BW = 64 MB/s, 200 ns per hop

- Pinelined

```

T_{64}(128) = 1.0 us + 2.0 us + 6 hops * 0.2 us/hop = 4.2 us T_{1024}(128) = 1.0 us + 2.0 us + 10 hops * 0.2 us/hop = 5.0 us

```

· Store and Forward

```

T_{64}^{sf}(128) = 1.0 \text{ us} + 6 \text{ hops} * (2.0 + 0.2) \text{ us/hop} = 14.2 \text{ us}

T_{64}^{sf}(1024) = 1.0 \text{ us} + 10 \text{ hops} * (2.0 + 0.2) \text{ us/hop} = 23 \text{ us}

```

3/1/05

CS252 s05 smp

## **Cost Scaling**

- cost(p,m) = fixed cost + incremental cost (p,m)

- · Bus Based SMP?

- Ratio of processors : memory : network : I/O ?

- Parallel efficiency(p) = Speedup(P) / P

- Costup(p) = Cost(p) / Cost(1)

- Cost-effective: speedup(p) > costup(p)

- · Is super-linear speedup possible?

3/1/05 CS252 s05 smp

50