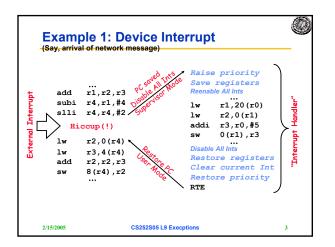

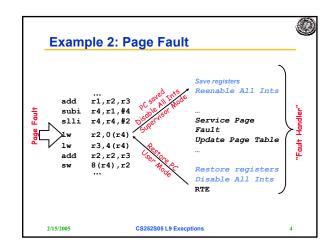

#### Supervisor State Entry into Supervisor Mode Typically, processors have some amount of state that Entry into supervisor mode typically happens on user programs are not allowed to touch. interrupts, exceptions, and special trap instructions. - Page mapping hardware/TLB » TLB prevents one user from accessing memory of another Entry goes through kernel instructions: interrupts, exceptions, and trap instructions change to supervisor mode, then jump (indirectly) through table of instructions in kernel » TLB protection prevents user from modifying mappings – Interrupt controllers -- User code prevented from crashing machine by disabling interrupts. Ignoring device interrupts, etc. intvec: j handle\_int0 handle\_int1 Real-time clock interrupts ensure that users cannot lockup/crash machine even if they run code that goes into a loop: » "Preemptive Multitasking" vs "non-preemptive multitasking" handle\_fp\_except0 j Access to hardware devices restricted handle\_trap0 Prevents malicious user from stealing network packets handle\_trap1 - Prevents user from writing over disk blocks – OS "System Calls" are just trap instructions: read(fd,buffer,count) => 20(r0).r1 st Distinction made with at least two-levels: 24(r0),r2 st USER/SYSTEM (one hardware mode-bit) st 28(r0),r3 \$READ x86 architectures actually provide 4 different levels, only two trap usually used by OS (or only 1 in older Microsoft OSs) OS overhead can be serious concern for achieving fast interrupt behavior. CS252S05 L9 Execptions 2/15/2005 CS252S05 L9 Execptions 10

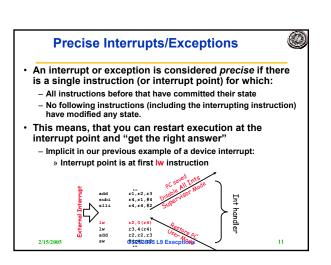

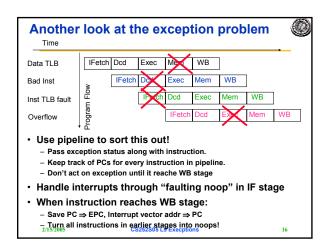

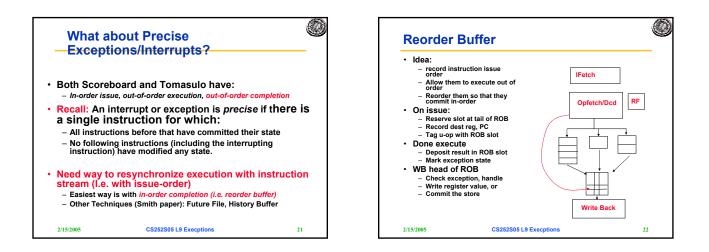

### Precise Exceptions in simple 5-stage pipeline:

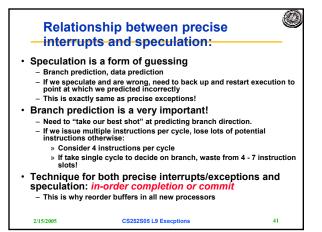

- Exceptions may occur at different stages in pipeline (I.e. out of order):

- Arithmetic exceptions occur in execution stage

- TLB faults can occur in instruction fetch or memory stage

- What about interrupts? The doctor's mandate of "do no harm" applies here: try to interrupt the pipeline as little as possible

- All of this solved by tagging instructions in pipeline as "cause exception or not" and wait until end of memory stage to flag exception

- Interrupts become marked NOPs (like bubbles) that are placed into pipeline instead of an instruction.

- Assume that interrupt condition persists in case NOP flushed

- Clever instruction fetch might start fetching instructions from

- interrupt vector, but this is complicated by need for

- 2/15 supervisor mode switch; saving of one or more PCs, etc

15

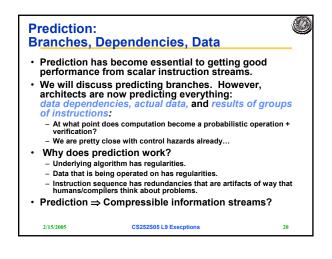

| loop • In our loo                      | ches mus<br>overlap!<br>op-unrolling ex<br>ler control of "f                                              | ample, we                             | e relied                      | on the fact                     | that branche | ©<br>** |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------|---------------------------------|--------------|---------|

| Loop:                                  | LD<br>MULTD<br>SD<br>SUBI<br>BNEZ                                                                         | F0<br>F4<br>F1<br>R1                  | 0<br>F0<br>0<br>R1<br>Loop    | R1<br>F2<br>R1<br>#8            |              |         |

| – We co<br>– Need<br>– If we v<br>most | opens if branch<br>ompletely lose<br>to be able to " <br>were to predict<br>of the time.<br>much worse fo | all of our<br>predict" b<br>that bran | advanta<br>ranch o<br>Ich was | iges!<br>utcome.<br>taken, this |              | jht     |

| 2/15/2005                              |                                                                                                           | CS252S05 L                            | 9 Execptio                    | ns                              |              | 19      |

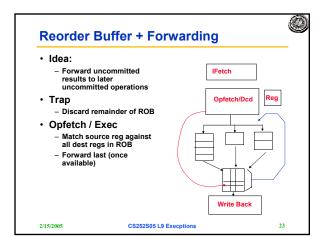

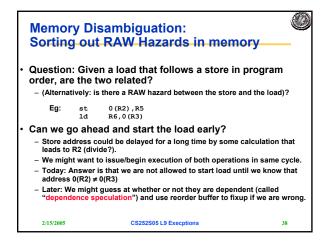

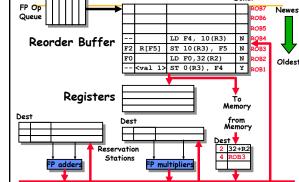

#### Hardware Support for Memory Disambiguation Need buffer to keep track of all outstanding stores to memory, in program order. Keep track of address (when becomes available) and value (when becomes available) FIFO ordering: will retire stores from this buffer in program order When issuing a load, record current head of store queue (know which stores are ahead of you). When have address for load, check store queue: - If any store prior to load is waiting for its address, stall load. If load address matches earlier store address (associative lookup), then we have a memory-induced RAW hazard: » store value available ⇒ return value » store value not available ⇒ return ROB number of source Otherwise, send out request to memory Actual stores commit in order, so no worry about WAR/WAW hazards through memory.

39

Done?

Memory Disambiguation:

CS252S05 L9 Execptio

2/15/2005

| Interrupt o<br>mask leve |                 | r hardware and                     | Polling                           | is faster/slower than<br>pts.                                                                     | 9    |  |

|--------------------------|-----------------|------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------|------|--|

| Operating evet           | om constru      | cts a hierarchy of masks           | Polling is fas                    | ster than interrupts because                                                                      |      |  |

|                          |                 | interrupt priority.                |                                   | ows which registers in use at polling point. Hence, do and restore registers (or not as many).    | not  |  |

| For instance:            | Priority        | Examples                           | <ul> <li>Other interru</li> </ul> | pt overhead avoided (pipeline flush, trap priorities, etc                                         | :).  |  |

|                          | 0               | Software interrupts                | Polling is slo                    | ower than interrupts because                                                                      |      |  |

|                          | 2               | Network Interrupts                 |                                   | polling instructions is incurred regardless of whether<br>n. This could add to inner-loop delay.  | or n |  |

|                          | 4               | Sound card                         |                                   | have to wait for service for a long time.                                                         |      |  |

|                          | 5               | Disk Interrupt                     | When to use                       | one or the other?                                                                                 |      |  |

|                          | 6               | Real Time clock                    | – Multi-axis tra                  | deoff                                                                                             |      |  |

|                          | Ø               | Non-Maskable Ints (power)          |                                   | » Frequent/regular events good for polling, as long as device can be<br>controlled at user level. |      |  |

| - This reflects the      | an order of urg | ency to interrupts                 | » Interrupt                       | s good for infrequent/irregular events                                                            |      |  |

|                          | s ordering says | that disk events can interrupt the | » Interrupt                       | s good for ensuring regular/predictable service of even                                           | nts. |  |

| 2/15/2005                | CS252S05 L9     | Execptions 49                      | 2/15/2005                         | CS252S05 L9 Execptions 5                                                                          | 50   |  |