### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

## Polycrystalline Silicon Thin-Film Transistor Technology for Flexible Large-Area Electronics

by

## Yeh-Jiun Tung

B.S. (Massachusetts Institute of Technology, Cambridge, MA) 1995 M.S. (University of California, Berkeley) 1998

A dissertation submitted in partial satisfaction of the

requirements for the degree of

**Doctor of Philosophy**

in

Engineering – Electrical Engineering and Computer Sciences

in the

**GRADUATE DIVISION**

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Tsu-Jae King, Chair Professor Chenming Hu Professor Costas Grigoropoulos

Spring 2001

**UMI Number: 3019837**

Copyright 2001 by Tung, Yeh-Jiun

All rights reserved.

#### UMI Microform 3019837

Copyright 2001 by Bell & Howell Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

Bell & Howell Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

# Polycrystalline Silicon Thin-Film Transistor Technology for Flexible Large-Area Electronics

Copyright 2001

by

Yeh-Jiun Tung

#### Abstract

## Polycrystalline Silicon Thin-Film Transistor Technology for Flexible Large-Area Electronics

by

#### **Yeh-Jiun Tung**

## Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

#### Professor Tsu-Jae King, Chair

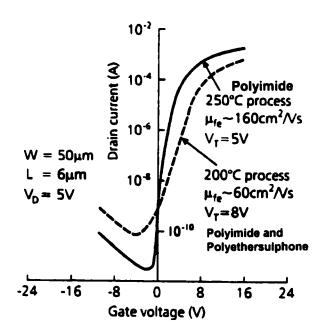

The development of a polycrystalline-silicon (poly-Si) thin-film transistor (TFT) technology compatible with plastic substrates will enable information displays and large-area electronics devices that are low power, low cost, lightweight and rugged. Significant challenges exist in the development of a poly-Si TFT fabrication process that is compatible with plastic substrates, since plastic cannot withstand high processing temperatures.

This dissertation addresses two critical issues for the ultra-low temperature (T≤100°C) fabrication of poly-Si TFTs directly on polymer substrates. The first issue is the formation of the gate dielectric, since thermal oxidation and conventional low-pressure chemical vapor deposition (LPCVD) are not possible at 100°C. At such a low temperature, the quality of the critical gate-dielectric to channel interface is poor. Oxide deposition must be performed using plasma-enhanced CVD (PECVD) or sputter deposition. The work here introduces the use of high-density plasma (HDP) sources,

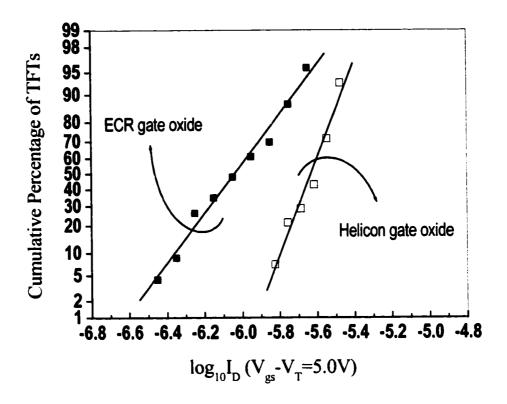

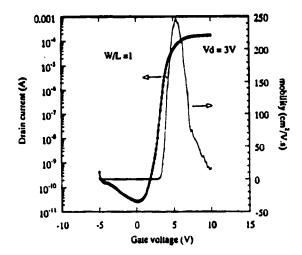

specifically helicon and electron cyclotron resonance (ECR) PECVD, for TFT gate oxide formation at ultra low temperature. Initial experiments were conducted to determine optimum recipes for SiO<sub>2</sub> deposition through the fabrication and characterization of metal-oxide-semiconductor (MOS) capacitors. Subsequently, high-performance, self-aligned gate poly-Si TFTs were fabricated using a process with a maximum substrate temperature of 100°C. At the time of this work, this process yielded the highest mobility devices reported for any TFT technology compatible with plastic substrates. It is shown that the use of HDP-PECVD tools significantly reduces interfacial oxide defect density compared to conventional parallel-plate PECVD tools.

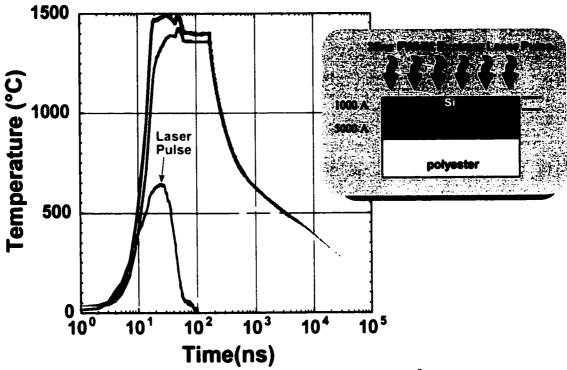

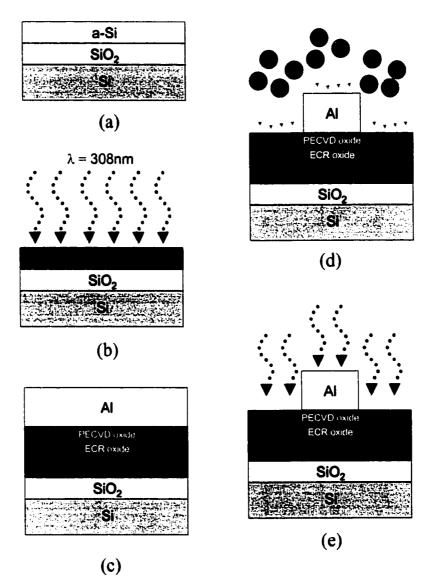

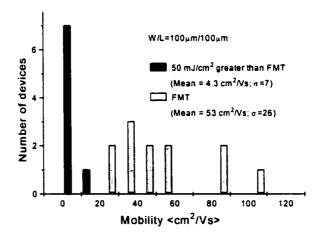

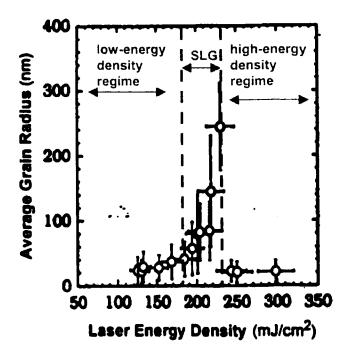

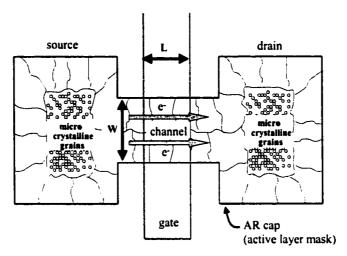

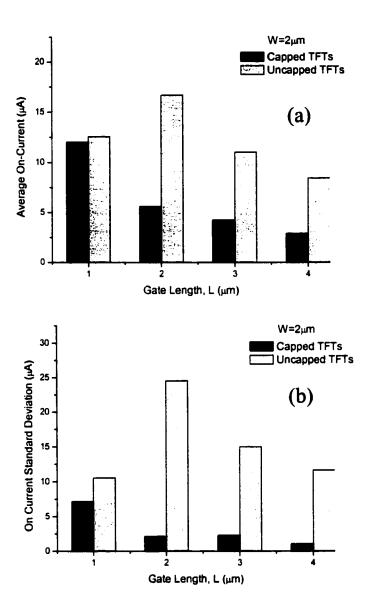

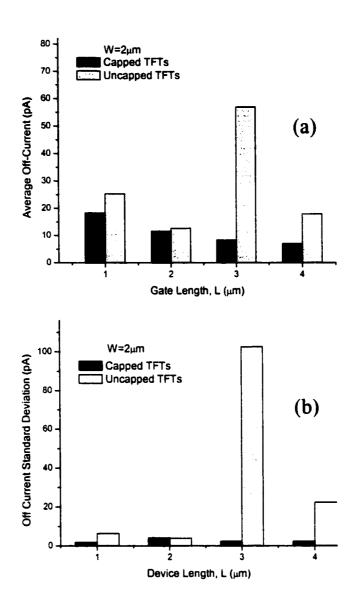

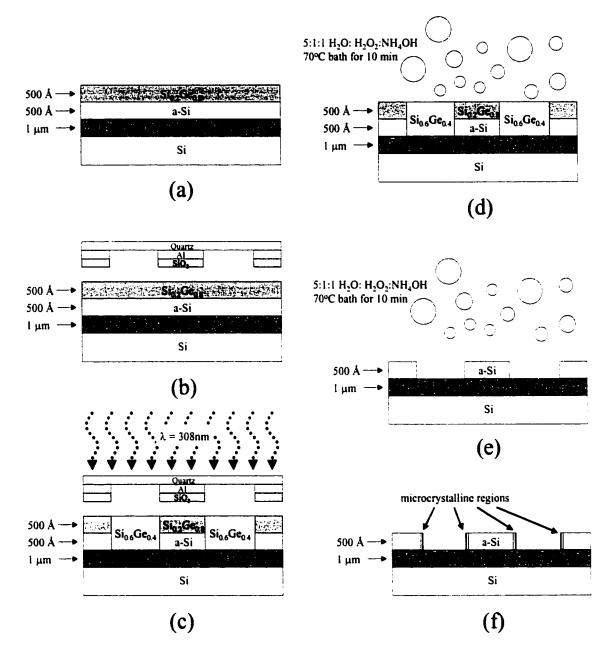

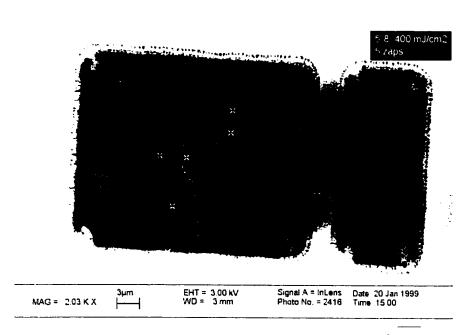

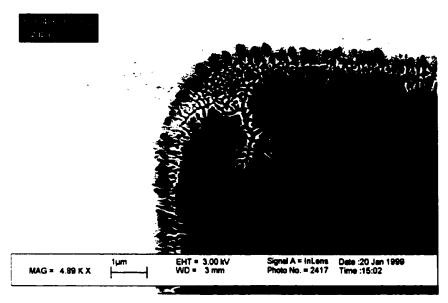

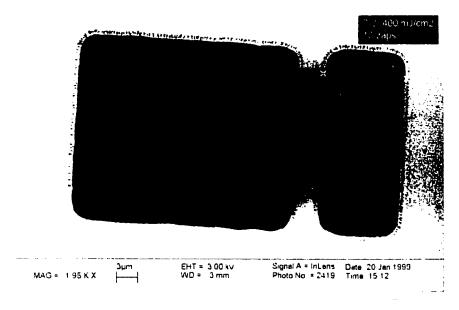

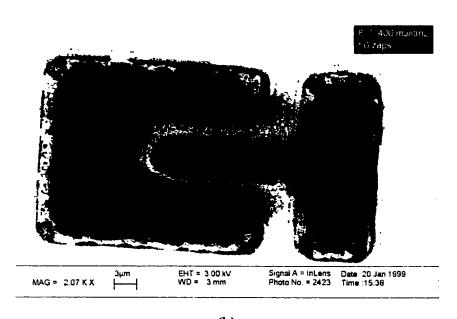

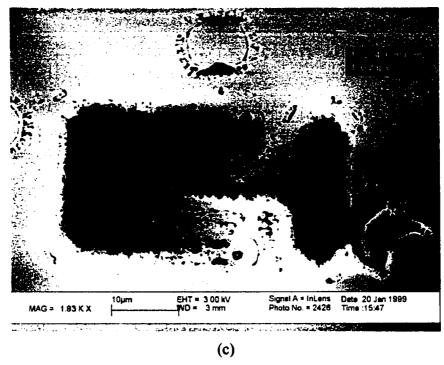

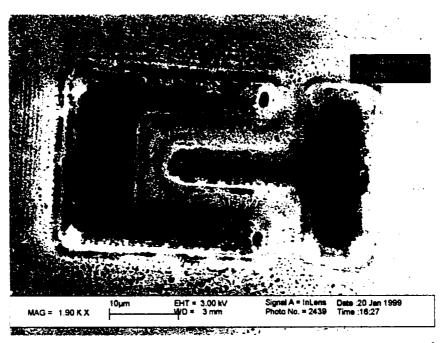

The second area of emphasis in this dissertation focuses on the poly-Si channel-film formation. Short-pulse excimer laser crystallization (ELC) is necessary to form poly-Si when a polymer substrate is used. (Plastics are incompatible with long, high-temperature crystallization processes.) Unfortunately, the range of laser fluences that yield large-grained poly-Si is very narrow, and often it is necessary to trade off good performance for device-to-device uniformity when ELC is used. This work introduces the use of a patterned anti-reflective (AR) oxide capping layer to control grain location in the channel film during ELC. Results from this new process show an improvement in TFT performance and uniformity. The process is self-aligned and simple, so it can be easily incorporated into existing ELC-based poly-Si TFT process flows.

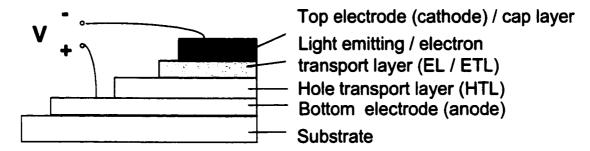

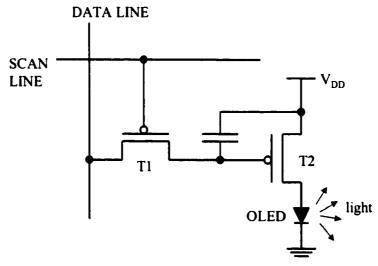

Two additional areas of work are presented in the latter part of the dissertation. A prototype for an active-matrix organic light-emitting diode (AMOLED) display is presented. A layout and fabrication process was designed for a monochrome 128x64 pixel, 80 dpi display on a 4"x4" square glass substrate. Each pixel contains two

transistors to drive an OLED. AMOLED displays are of great interest because they promise lower power, higher brightness, and wider viewing angle than the pervasive active-matrix liquid crystal display (AMLCD). In addition, the inherently low deposition temperature of organic materials allows for easy processing on flexible plastic substrates.

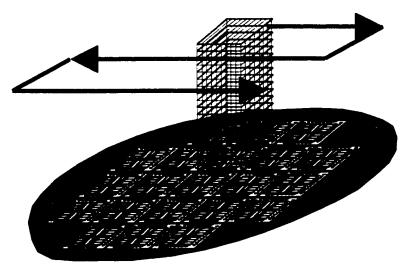

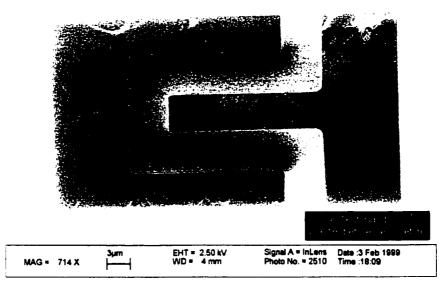

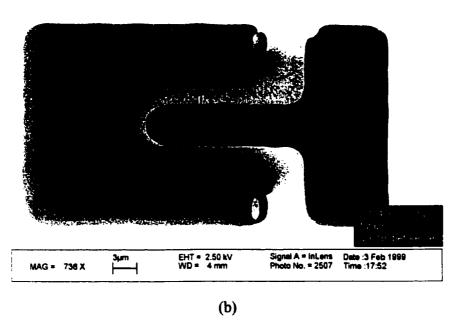

Lastly, a method is demonstrated for resist-free, direct patterning of thin films using an excimer laser. This technique addresses current problems plaguing the flat panel display manufacturing industry. High costs are associated with large area lithography that uses conventional photoresist coating, exposure and development. We present preliminary results for a direct patterning method that dramatically simplifies the lithography process. Specifically, the Si active layer is patterned by selectively exposing a laser beam onto a sacrificial layer of Si<sub>x</sub>Ge<sub>1-x</sub> that sits atop the Si film. The sacrificial film mixes with the underlying Si film and is then removed by a highly selective wet etch.

The dissertation abstract of Yeh-Jiun Tung is approved:

Professor Tsu-Jae King

Date

Committee Chair

## **Table of Contents**

| Chapter 1 Introduction 1                                      |

|---------------------------------------------------------------|

| 1.1 Flat-Panel Display Technologies                           |

| 1.1.1. The Flat-Panel Display Market                          |

| 1.1.2 Passive- vs. Active-Matrix LCDs4                        |

| 1.2 Thin-Film Transistor Technologies                         |

| 1.2.1. Amorphous silicon TFT Technology                       |

| 1.2.2. Poly-Si TFT Technology                                 |

| 1.3 Display Industry Trends                                   |

| 1.4 Organization                                              |

| 1.5 References                                                |

| Chapter 2 Ultra-Low Temperature Gate Dielectric Formation23   |

| 2.1 Introduction                                              |

| 2.2 Electron Cyclotron Resonance PECVD                        |

| 2.2.1 Background and System Configuration                     |

| 2.2.2 Experiments                                             |

| 2.3 Helicon Source PECVD                                      |

| 2.3.1 Background and System Configuration                     |

| 2.3.2 Experiments                                             |

| 2.4 References 46                                             |

| Chapter 3 Ultra-Low Temperature Fabrication of Poly-Si TFTs 4 |

| 3.1 Introduction                                              |

| 3.1.1 Polymer substrates: Advantages and Disadvantages            | 48            |

|-------------------------------------------------------------------|---------------|

| 3.1.2 TFTs on Polymer Substrates: Prior Work                      | 50            |

| 3.1.3. TFT Performance Requirements                               | 54            |

| 3.2 Fabrication Approach                                          | 55            |

| 3.2.1 Sputtered a-Si                                              | 56            |

| 3.2.2 Excimer Laser Annealing                                     | 57            |

| 3.2.3 Gate Oxide Formation                                        | 58            |

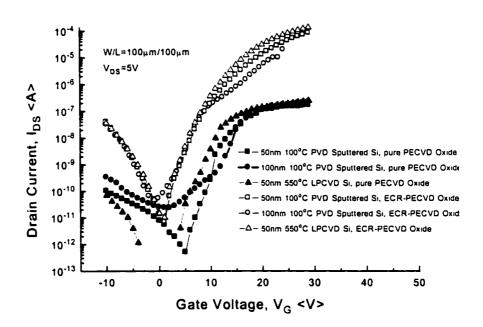

| 3.3 ECR-PECVD Gate Oxide Process                                  | 59            |

| 3.3.1. Process Flow                                               | 59            |

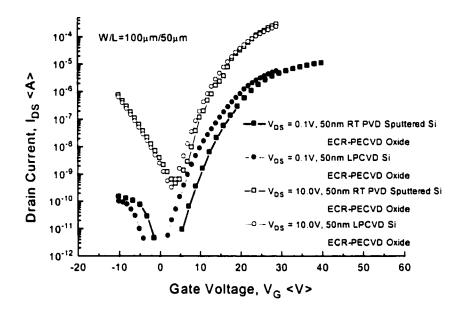

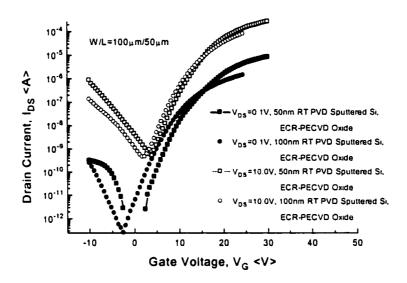

| 3.3.2. TFT Performance                                            | 61            |

| TFT process details                                               | 63            |

| 3.4 Helicon Source PECVD Gate Oxide Process                       | 66            |

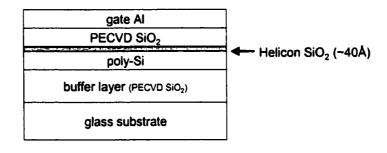

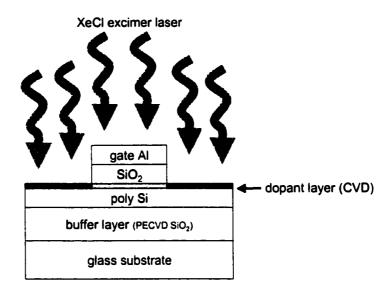

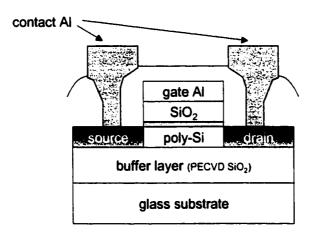

| 3.4.1. Process Flow                                               | 66            |

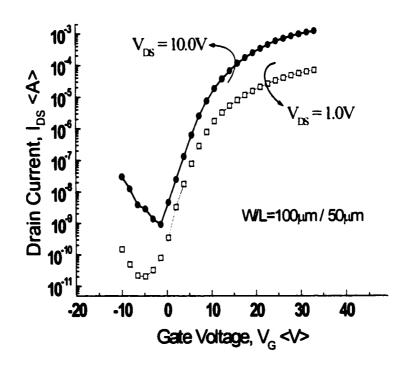

| 3.4.2. TFT Performance                                            | 69            |

| 3.5 Conclusion                                                    | 71            |

| 3.6 References                                                    | 73            |

| Chapter 4 A New Method for Improving Uniformity of Poly-Si TFT Po | erformance 76 |

| 4.1 Introduction                                                  | 76            |

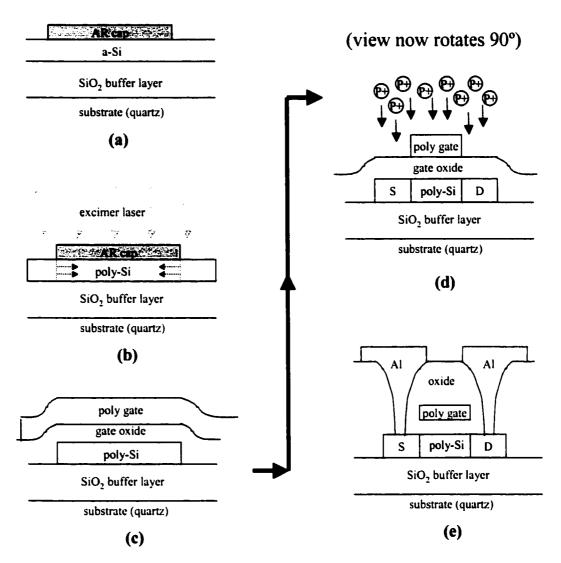

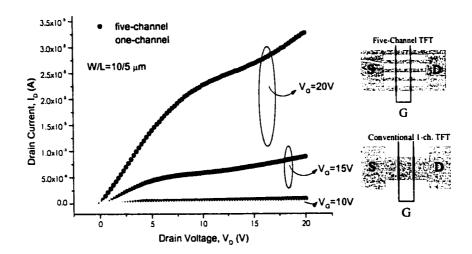

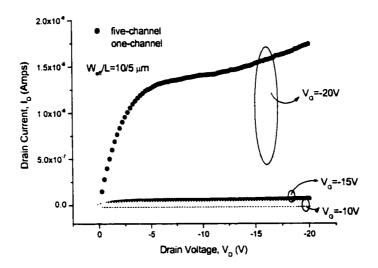

| 4.2 Process Flow                                                  | 82            |

| 4.3 TFT Performance                                               | 85            |

| 4.4 Pafaranas                                                     | or            |

| Chapter 5 Design of a Poly-Si TFT Active-Matrix Organ | ic Light Emitting Diode |

|-------------------------------------------------------|-------------------------|

| Display Prototype                                     | 93                      |

| 5.1 Introduction                                      | 93                      |

| 5.2 Display Prototype Specifications                  | 98                      |

| 5.3 Active-Matrix Process Flow                        | 100                     |

| 5.4 References                                        | 102                     |

| Chapter 6 A Direct Patterning Method Using Silicon-Ge | rmanium Films103        |

| 6.1 Introduction                                      | 103                     |

| 6.2 Process Description                               | 108                     |

| 6.3 Initial Results                                   | 111                     |

| 6.4 Conclusion                                        | 117                     |

| 6.5 References                                        | 117                     |

| Chapter 7 Conclusions                                 | 119                     |

| 7.1 Summary                                           | 119                     |

| 7.2 Contributions                                     | 122                     |

| 7.3 Suggestions for Future Work                       | 123                     |

| 7.4 References                                        | 127                     |

| Appendix A AMOLED Process Runsheet                    | 129                     |

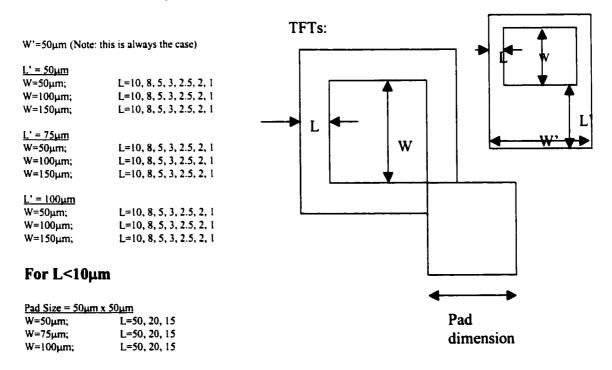

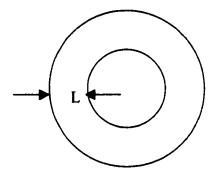

| Appendix B TFT Mask Layouts                           | 133                     |

| B.1 Simplified Two Mask Set TFT Layout                | 133                     |

| B.2 Conventional TFT Mask Set Structures List         | 134                     |

### **Acknowledgments**

I would like first and foremost to thank my advisor, Professor Tsu-Jae King. Due to her continuous guidance and support, my graduate school experience has been enormously positive and enriching. She has been the ideal advisor in every aspect. Her keen technical insight enabled me to make forward progress when I needed direction, while her patience and commitment were a constant source of encouragement. It is truly a privilege to have been a student of hers over the past few years.

I would like to thank Professor Chenming Hu for serving on my master's thesis committee, qualifying exam committee and dissertation committee. He has been greatly supportive since my first year when I was enrolled in his solid-state devices course, and I am grateful for his generosity of time and spirit.

I would also like to thank Professor Nathan Cheung for serving on my qualifying exam committee. I was fortunate enough to have taken the department's three semiconductor processing courses during the semesters that he was teaching them. His enthusiasm and energy in class fueled my interest in research.

I am grateful to Professor Timothy Sands of the Materials Science and Engineering Department for serving on my qualifying exam committee.

My thanks also to Professor Costas Grigoropoulos for serving on my dissertation committee.

I must also express my gratitude toward Dr. Paul Carey, Dr. Paul Wickboldt, and Dr. Patrick Smith for the opportunity to work in their group at the Lawrence Livermore National Laboratory during the summer of 1998. Their mentoring pointed me down an

exciting path of research, and they have continued to be an unfailing source of advice and encouragement since then.

My thanks go to Jim Bustillo, Alex Papavasiliou, Johan Vanderhaegen, and Scott McNally for the enjoyable lunch hour runs up into the Berkeley Hills. I am also grateful to the members of Cal Cycling for introducing me to the rewarding world of collegiate bicycle racing.

I would like to recognize all the talented members of the Device Group for their various contributions to this dissertation. I am especially grateful for the friendship of the following people: Dennis Sylvester, Ching-Yune Chen, Yuan and Thuyen Wang, Steve Czerwinski, Stephen Hwang, Anoop Sinha, John Ueng-McHale, Xuejue Huang, and Lance Doherty.

Most importantly, I would like to thank my family. I owe all my achievements to their unconditional love and support.

## Chapter 1

## Introduction

## 1.1 Flat-Panel Display Technologies

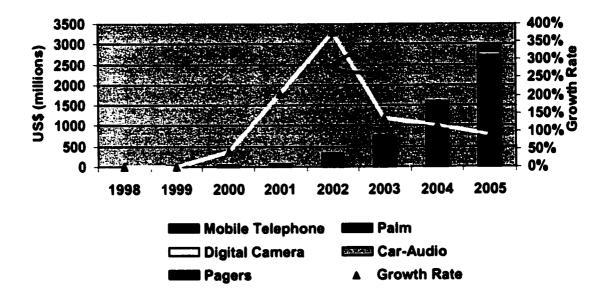

### 1.1.1. The Flat-Panel Display Market

Flat panel display (FPD) technologies have long sought to supplant the firmly entrenched cathode ray tube (CRT) as the dominant electronic information display medium. Since 1950, there has been a sustained effort to find a replacement for the CRT. However, the CRT has many virtues for information displays: extremely fast response; high resolution; vivid color and excellent image quality; and both small-size (1-in. diagonal) and large-size (36-in. diagonal) formats for varied applications. As recently as the beginning of the 1980's, the CRT was still the only commercially available device that could display full color TV video. CRT technology has been continuously improving since its inception, but the most significant trend for CRTs is decreasing cost. Because

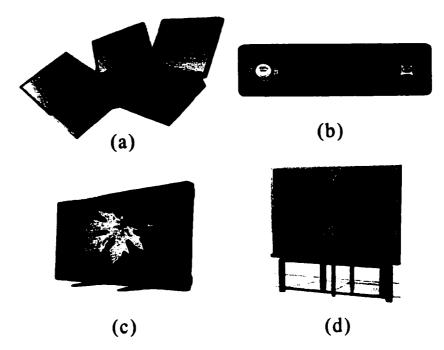

Figure 1.1. Examples of various FPD technologies: (a) LCD screens in laptop computers (from http://www.dell.com). (b) Pioneer DEH-P9200R car stereo display featuring an organic electro-luminescent (EL) display (from http://www.pioneerelectronics.com). (c) Sony 40-in. plasma display panel (PDP) television (from http://www.sony.com). (d) Rear projection Hitachi 55DMX 2000 digital micromirror device (DMD) TV (from http://www.hitachi.com).

CRTs are continually getting cheaper and better, the cost challenge is the most difficult for flat-panel technologies. But the CRT does have one drawback that it cannot overcome: it is too bulky. The large volume stems from the depth of the tube, which is required to focus and scan the image and is thus comparable to its diagonal dimension. This depth remains the CRT's Achilles' heel.

In contrast, FPDs are compact, lightweight and consume less power. These features alone have enabled many products and applications, despite the higher costs of FPDs. A wide variety of FPD technologies can be found in commercial electronics nowadays (Figure 1.1). The leading FPD technology is liquid crystal displays (LCDs), which are found in laptop computers, watches, personal digital assistants (PDAs),

handheld computers, mobile phones, pagers, among other applications. An emerging FPD technology is based on organic light-emitting diodes (OLEDs). OLEDs are meant to compete directly with LCDs and are just beginning to be available to consumers. These bright, high-contrast and low-power displays can be found in Pioneer car stereo displays and Motorola and Sanyo cellular phones. Plasma display panels (PDPs) are another commercially available FPD technology. Major electronics companies (e.g. Philips, Panasonic, Fujitsu, Pioneer and Sony) manufacture large-area (50-inch diagonal), high-definition PDP television sets with 4" depths.<sup>2</sup> Though presently expensive, PDP TV sets are expected to be cost competitive with CRT TVs by 2003. In the projection display arena, Texas Instruments has developed an electro-mechanical display technology called the digital micromirror device (DMD). Hitachi, Mitsubishi and Panasonic use these tiny mirror arrays in rear projection displays for desktop monitors and televisions.<sup>3</sup>

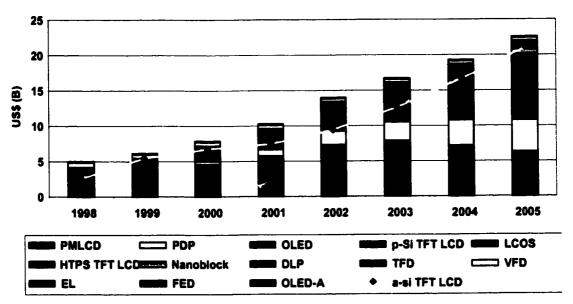

These examples demonstrate that a vast array of CRT-alternative display technologies exists. With new technologies constantly being introduced, more mature technologies are forced to improve performance and lower cost. As a result, FPD sales have been rising steadily, particularly in the last decade. It is predicted that FPDs will capture 50% of the worldwide display market by 2003,<sup>4</sup> thus ending nearly a century of the CRT's dominance. Within the FPD market itself, LCDs represent the largest segment by far, comprising the majority of total FPD sales. Figure 1.2 shows the world market for FPDs by technology. LCD dominance is still expected to continue in the coming decade. LCDs enjoy this lofty market position because they are the most mature of the FPD technologies, making them both the highest performance display technology and the lowest cost as well.

Figure 1.2 World market for FPDs by technology. Improvements in competing display technologies will continue to drive the progress of AMLCDs. (source: DisplaySearch)

#### 1.1.2 Passive- vs. Active-Matrix LCDs

LCDs can be categorized into two broad categories: passive-matrix and active-matrix. As background to discussion of these display types, the fundamentals of LC operation are first presented. Then, the basic operation of passive and active displays is described, with an emphasis on the increasing importance of high-performance active-matrix technologies.

Liquid crystal is a state of matter that exists between liquid and solid. LC materials can flow as liquids, but there is some long-range order due to an elongated molecular structure, which leads to the parallel alignment of molecules. This long-range order creates a unique electro-optic characteristic that can be exploited for displays.

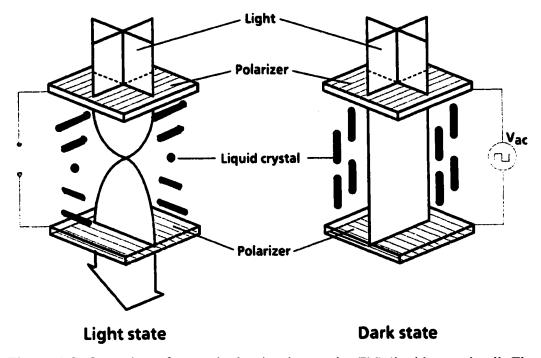

Figure 1.3 shows a schematic of a standard twisted nematic (TN) LC cell. The liquid crystal is sandwiched between two glass plates that are each coated with a

Figure 1.3. Operation of a standard twisted-nematic (TN) liquid-crystal cell. The nematic LC molecules align with the brushed surface of the top and bottom electrodes so that the orientation of the LC molecules undergoes a twist from one electrode to the other. The polarization axis of the light entering the cell is effectively rotated by the twisted LC layer so that it can pass through the second polarizer (light state). Under applied voltage, the LC molecules tend to align with the electric field so that the polarized light cannot pass through the second polarizer (dark state).

transparent conducting material (Indium Tin Oxide or ITO) and an orienting layer. The orienting layer is formed by brushing an organic film in one direction, thus creating grooves. In the figure, these layers on the two plates are oriented perpendicular to each other. The liquid crystal aligns its molecules with the direction of the grooves at the surface of each plate, so that the molecules must then twist 90° from top to bottom.

Liquid crystal is optically anisotropic. It has a different index of refraction for light polarized parallel to its molecular rods  $(n_e)$  compared to light polarized perpendicular to its rods  $(n_o)$ . If the twist is sufficiently gradual, then the polarization of light will twist in the same direction at the LC material. As shown in the figure, light

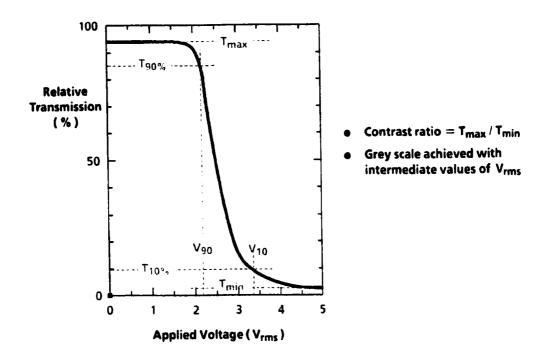

Figure 1.4. Electro-optic response of a TN LC cell. Light transmission varies with applied voltage. Grayscale is achieved by applying voltages between  $V_{90}$  and  $V_{10}$ , where light transmission varies between 90% and 10% respectively.

enters the cell polarized in the x-direction, slowly rotates polarization as it passes through the cell, and exits polarized in the y-direction. In this case, light is transmitted, so it is the "light state." LC also exhibits dielectric anisotropy, so that the rods tend to align to an applied electric field. When a voltage is applied between the plates, the 90° twist is disturbed and light can longer be transmitted through the cell. This is the "dark state." Essentially, the LC cell acts as a light valve.

The light transmission of an LC cell varies with applied voltage. This curve, shown in Figure 1.4, exhibits varying light transmission as a function of applied AC rms (root mean square) voltage. (An AC signal is required to drive the LC materials to prevent deterioration of the cell.) This LC cell is called "normally white," because light

passes in the normal state, i.e. zero applied voltage. (A "normally black" cell would have the inverse curve.) As the applied voltage is increased, the LC molecules at the center plane begin to align to the electric field and transmission is gradually reduced until near-zero transmission at  $V_{rms}$ =5V. Grayscale can be achieved using intermediate  $V_{rms}$  values between 90% transmission ( $T_{90\%}$ ) and 10% transmission ( $T_{10\%}$ ). However, high-level grayscale requires precise control of the voltage level in this transition region. For instance, 8-bit grayscale (16.7 million colors) requires 256 distinct voltage levels within a range of roughly 1.2V in this example. Maintaining these fine voltage levels over the refresh time of the cell is critical to achieving good grayscale performance. The contrast ratio of the cell is defined as the ratio between the maximum and minimum transmission ( $T_{max}/T_{min}$ ).

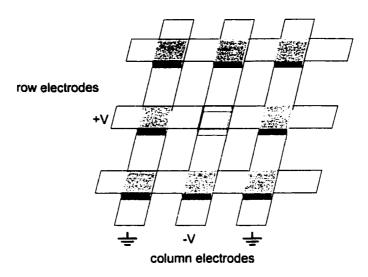

Passive-matrix displays are constructed using two sets of perpendicular electrodes: horizontal row and vertical column electrodes. Figure 1.5 shows a schematic of the passive-matrix structure. The intersection of these electrodes defines the pixels. Operation consists of sequentially raising the potential of each row electrode to +V, while the data is loaded through the column lines by either applying -V (leading to white cells in a normally black display) or grounding (leading to dark cells). The full voltage only appears across the selected pixels. By repeating this process for all row and column electrodes at a frame rate of ~50Hz or higher, an image is formed. Passive-matrix displays thus have a simple, inexpensive construction and a simple multiplexed addressing scheme.

Passive-matrix addressing suffers from one major drawback: applied voltages also affect non-selected pixels in the selected row and column. This crosstalk is due to "sneak

Figure 1.5. Passive-matrix structure schematic. Row and column electrodes consist of perpendicular conducting lines on opposing glass plates, and the intersection of the electrodes define the pixels. In this figure, the LC cells are "normally black." The center pixel is addressed by biasing the row electrode to +V and the corresponding column electrode to -V. The applied voltage allows the cell to pass light.

paths" throughout the matrix and leads to a significant voltage drop across the cells in the selected row and column. The image quality suffers because there is a reduction in the contrast between selected and non-selected pixels. A steep LC electro-optic characteristic is required to ensure that partially selected pixels do not turn on (or off). The problem is exacerbated as the display size and number of pixels increase. The various display metrics (viewing angle, grayscale compatibility, contrast and speed of response) are often comprised for large passive-matrix displays to ensure a narrow transition region in the electro-optic characteristic. High-resolution, high-contrast passive-matrix displays are not be possible due to the Alt-Pleshko limit.<sup>5</sup>

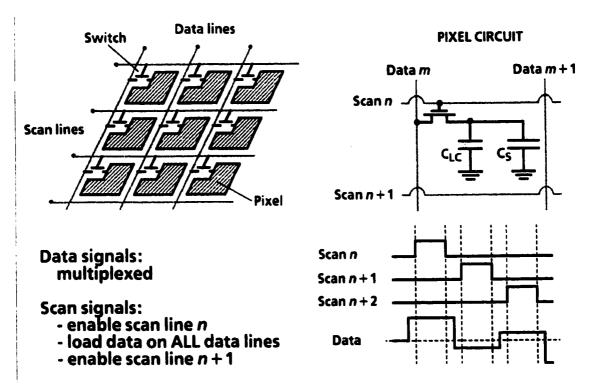

Active-matrix technology provides a solution to this limit for passive-matrix displays. Figure 1.6 shows a schematic of an active-matrix structure and describes the addressing scheme. The active-matrix circuit is similar to a large feature-size VLSI

DRAM with 1-T cells. A thin-film transistor (TFT) is used in each pixel, acting as a switch to store the voltage on the pixel electrode. Addressing is accomplished by driving one row (scan line) at a time, biasing the transistor gates high and loading data into the pixels from the column lines. After one row of data is loaded, the transistors are turned off and the next row is selected. The pixel electrodes are isolated from each other by the TFTs, and a constant voltage is maintained over the refresh cycle time (if the TFT and LC leakage currents are sufficiently low). As a result, the contrast is considerably better than in passive-matrix displays. In addition, the LC electro-optic curve no longer needs to be as abrupt, so other aspects such as viewing angle and response time can be optimized.

Figure 1.6. A schematic of active-matrix LCD structure and operation. A TFT is used at each pixel as a switch to control the voltage of the LC cell. Image data is loaded as follows: the TFT gates are turned on by applying a voltage to single row, then data is transferred to the pixels from the column (data) lines. Then, the row is turned off and the next row is selected. This process is repeated for each row line until the entire display image is loaded. A storage capacitor (C<sub>S</sub>) is placed in parallel with the LC cell to maintain the voltage across the LC cell for a frame time (~16msec for a 60Hz refresh rate).

Pixel TFTs in active-matrix displays have relatively modest performance requirements. The devices must be able to fully charge the pixel capacitance ( $C_{LC} + C_S$ ) during one line time (the duration that the scan line is pulsed high). Typically, the drive current required is  $\sim 1 \mu A$ . Such drive currents should be achievable at a gate-to-source voltage ( $V_{GS}$ ) < 30V in order to avoid the use of expensive, high-voltage IC driver chips. The leakage currents should be low enough so grayscale levels can be maintained over the frame refresh time. Typically, the voltage across the pixel should not change by more than 20mV over the frame time, and the corresponding requirement is for leakage currents to be less than 1pA.

Unfortunately, fabrication of active-matrix displays is a difficult task because the TFTs are distributed over such a large area. The costliest and most complex component in the AMLCD manufacturing process is the active-matrix backplane. An XGA monitor (1024x768 pixels) has approximately 785,000 transistors for a monochrome display. For color displays, 2.35 million transistors are required! The active-matrix must be fabricated on a large glass panel (roughly one meter on a side) with near perfect yield. But the most challenging constraint is that the process must entirely compatible with the substrate material. In most cases, displays are fabricated on glass sheets that have a strain point far below the melting point of silicon. For example, the commonly used Corning 1737 has a strain point of 666°C, so all process steps must be performed below this temperature.

Thin-film transistor performance and process technology is closely correlated to the maximum fabrication temperature, which has implications for the electrical properties of the active layer. For example, amorphous silicon (a-Si:H) TFTs can be fabricated at temperatures below 350°C, while poly-Si TFTs generally require much higher

temperatures due to the need to crystallize Si. The resulting electrical performance of these two TFT technologies can differ dramatically. In the next section, an overview of TFT technologies is presented.

## 1.2 Thin-Film Transistor Technologies

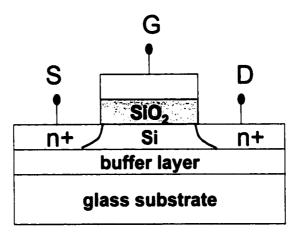

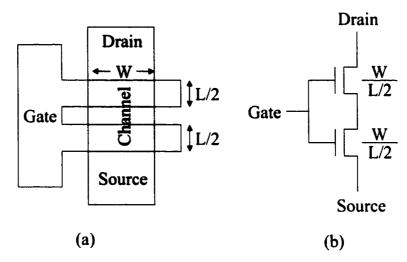

Figure 1.7 shows a typical structure for a top-gated TFT. TFTs are similar to silicon-on-insulator (SOI) transistors; the active layer is a thin film isolated from the substrate by a buffer dielectric. However, unlike SOI CMOS devices, TFTs are usually fabricated on glass substrates using either amorphous or polycrystalline Si films, which have an abundance of defects with associated carrier trap states within the Si bandgap. The presence of these traps results in significantly poorer transistor performance when compared to crystalline Si (c-Si) MOSFETs.

Figure 1.7. A cross-sectional schematic of a typical top-gate TFT structure (in this case, n-channel).

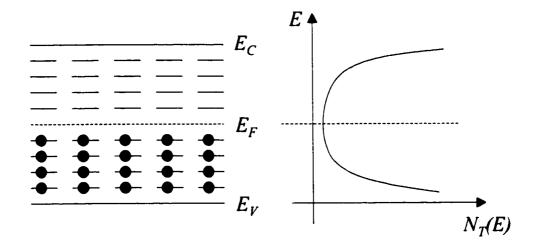

The spatial and energy distribution of trap states within the bandgap are largely a function of how the Si film is formed. For instance, in the case of a-Si, the spatial distribution of defect states is fairly uniformly throughout the material. In the case of poly-Si, trap states are mostly localized at the grain boundaries (intergranular defects) but can also exist within the grains themselves (intragranular defects) in the form of strained or dangling bonds. The energy distribution of trap state densities also differs between a-Si and poly-Si. Figure 1.8 shows a sample trap state density distribution as a function of energy within the bandgap. The Fermi level is located near the midgap (for undoped material), and the trap state density is usually higher near the conduction and valence bands. The exact shape of this curve varies depending on the physical structure of the film, which is usually dictated by the temperature and method of deposition.

Figure 1.8. An illustration of trap state density distribution within the Si bandgap. Typically the trap state density increases near the band edges, but the exact shape of the distribution is dependent on the physical structure of the material itself. The temperature and method of film deposition is the largest determinant of film structure.

When transistors are fabricated using such high trap state density material (such as a-Si or poly-Si), electrical performance suffers in a number of ways. First, the threshold voltage is high. As the gate voltage is increased, it is initially balanced by the trapped charge in the midgap, and the trap states must be filled before sufficient mobile carrier concentration is generated for current conduction between source and drain. Secondly, the mobility is very low. The presence of defects leads to additional scattering of carriers, and the maximum achievable mobility of a-Si devices is about two orders of magnitude lower than for VLSI CMOS devices. Nonetheless, a-Si TFT technology remains the dominant transistor technology used in AMLCDs today. Why? Amorphous silicon TFTs are easily and inexpensively fabricated at temperatures compatible with low-cost glass substrates, and they provide adequate performance for the vast majority of AMLCDs.

#### 1.2.1. Amorphous silicon TFT Technology

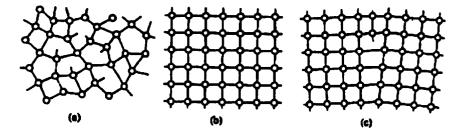

Amorphous silicon has no long-range order. The film is essentially a random network of Si atoms with a distribution of bond angles near the 109.5° bond angle of crystalline, tetrahedrally bonded silicon. A-Si can be distinguished from perfectly ordered c-Si and poly-Si, which consists of randomly oriented grains of single-crystalline material, as shown in Figure 1.9. While crystalline silicon exists only as a perfect matrix, both a-Si and poly-Si are not unique materials, taking on many forms depending on deposition method and temperature.

Figure 1.9. Two-dimensional schematic illustrations of the atomic structure of (a) amorphous, (b) crystalline and (c) polycrystalline silicon. Amorphous Si has no long-range order and contains many dangling bonds. Crystalline Si exhibits perfect order with no defects, and poly-Si is composed of randomly-oriented grains, where defects tend to be localized at the grain boundaries.

Deposition of a-Si and SiN<sub>x</sub> (dielectric) is usually accomplished with plasma-enhanced chemical vapor deposition (PECVD) at low substrate temperatures (250-350°C) using a gas flow of reactants (SiH<sub>4</sub>, NH<sub>3</sub>), dopants (PH<sub>3</sub>, for n-type Si), and dilution gases (N<sub>2</sub>, Ar or He). At these temperatures, hydrogen from the reactant gas is not completely desorbed, and consequently the a-Si contains considerable quantities of hydrogen (10-30%). The presence of hydrogen is actually beneficial, serving to terminate the many dangling bonds that exist in the random network of Si atoms (thus reducing the number of electrical defects in the film).

The best a-Si films, however, yield TFTs with effective electron mobility ≤ 2cm²/Vs. While a-Si TFTs provide enough drive current to charge an LC cell, they do not have sufficient performance to be used efficiently in the peripheral circuitry that is used to address the display. As a result, conventional AMLCDs must use off-chip IC driver chips for addressing the "dumb" a-Si active-matrix. In such a scheme, there must be as many connections to the display as there are scan lines and data lines. For commonly used chip-bonding methods (such as tape-automated bonding), the pitch between the lines

is extremely tight (~60µm for 4000 lines in high-resolution displays), and the bonded wires must be able to withstand mechanical shock and thermal mismatch between the glass, silicon and polymers used in the package. Thus, strict requirements are placed on these connections, and the cost of packaging reliable external driver circuitry is high.

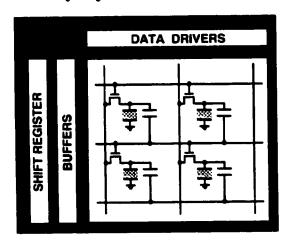

The higher mobility of poly-Si TFTs (vs. a-Si TFTs) makes it possible to directly integrate driver circuitry onto the display substrate periphery. In Figure 1.10, an illustration of a "dumb" a-Si active matrix display is shown in comparison with poly-Si TFT active matrix technology, where drivers for both scan and data lines are sketched. With high performance poly-Si TFT technology, the number of external connections can be significantly reduced, thus improving reliability and reducing overall system cost.

## **Amorphous Silicon**

## **Polycrystalline Silicon**

Figure 1.10. A-Si vs poly-Si technology. A-Si TFTs have carrier mobility < 2cm<sup>2</sup>/Vs, while poly-Si carrier mobility typically exceeds 30cm<sup>2</sup>/Vs. The higher performance of poly-Si TFT technology offers the possibility of: (1) higher-aperture-ratio for lower power or brighter displays (2) integration of peripheral driver circuitry, leading to reduced system cost and improved reliability.

#### 1.2.2. Poly-Si TFT Technology

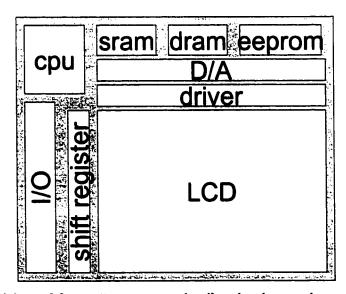

Poly-Si TFTs not only offer higher mobilities than a-Si TFTs but also lower threshold voltages and the capability to implement CMOS circuitry for reduced power consumption. (Hole mobility in p-channel a-Si TFTs is too low for practical devices, but p-channel poly-Si devices are feasible.) The higher performance of poly-Si TFTs is beneficial in a number of ways. First, the aperture ratio of the pixel can be increased, since the poly-Si TFT does not require as much area as its a-Si counterpart, resulting in a brighter display. Second, higher resolution displays are realizable, since the pixel sizes can be reduced with the smaller TFT dimensions. Third, high-speed CMOS poly-Si TFT driver circuitry can be integrated directly on the display periphery to reduce the number of external connections, which serves to reduce the packaging cost and to make the display more compact. Ultimately, it may be possible to achieve a system-on-glass, where even complex CPU logic is implemented using TFTs. Figure 1.11 illustrates how such a system might look.

Figure 1.11. A vision of future "system-on-glass" technology, where all components are fabricated directly on the display (glass) substrate.

As mentioned previously, poly-Si has many forms. Grain size can vary from the smallest extreme, i.e. a-Si in the zero limit, to being infinitely large, i.e. crystalline silicon. Not only can grain size vary, but the quality of the Si grain can vary as well. The intragranular defect density can be different even for films having the same average grain size. However, the greatest factor in poly-Si TFT performance is grain size, because defects tend to be concentrated at the grain boundaries. Poly-Si TFTs with larger grain sizes have higher drive currents, lower leakage currents and lower threshold voltages because there are fewer grain boundaries within the active channel region. In crystallizing Si films, the eventual goal is to form a single-crystalline structure, but the immediate research focus is to achieve the largest grains possible at temperatures compatible with glass panels used in flat-panel display manufacture.

The use of poly-Si introduces additional process complexity because substrates used in flat-panel display manufacture only tolerate very low maximum process temperatures. Generally, the average grain size of the poly-Si film improves with increasing process temperature. Poly-Si is optimally formed by crystallizing an a-Si precursor film, which is deposited using LPCVD or PECVD at 350-550°C. Crystallization can be accomplished by annealing at 550-600°C (known as solid-phase crystallization or SPC) or the presently preferred method of pulsed excimer laser crystallization (ELC).

Using SPC, large poly-Si grains can be obtained by annealing at high temperatures (>950°C) and/or for many hours, but such techniques are unfortunately incompatible with glass substrates. The best glass panels such as Corning 1737 has a strain point near 660°C. Thus, for SPC, the poly-Si quality is effectively constrained by

the glass substrate. For crystallization temperatures near 600°C, the average grain size can range from 500-5000Å. With minimum TFT dimensions being on the order of one micron, a number of grain boundaries will exist in the active channel.

In contrast, ELC of a-Si precursor films tends to form larger, much less faulted grains, and resulting films can have mobilities approaching that of single-crystalline silicon. The short-pulsed, transient nature of ELC also significantly reduces the impact of the annealing process on the underlying substrate. (The laser dwell time is short enough so that even plastic substrates with glass transition temperature as low as 150°C can be used with ELC of poly-Si.) Hence, ELC is the preferred procedure for the formation of large-grained high-quality poly-Si films. There are, however, problems associated with ELC. Poly-Si grain size is highly sensitive to laser energy fluence and therefore difficult to control. As a result, poly-Si TFT performance and uniformity are important issues for ELC.

Gate dielectric formation is another critical process step in low-temperature poly-Si TFT fabrication. Unfortunately, it is impossible to form a thermal oxide, which requires growth temperatures greater than 700°C. The poly-Si TFT gate oxide is typically deposited by a chemical vapor deposition technique: low-pressure CVD (LPCVD, 400°C), atmospheric-pressure CVD (APCVD, 300–500°C), or plasma-enhanced CVD (PECVD, R.T.–500°C). CVD oxides are substantially inferior to thermal oxides, having a more porous physical structure and a lower quality SiO<sub>2</sub>/Si interface (higher density of interfacial trap states, D<sub>it</sub>). The D<sub>it</sub> for PECVD oxides can be as much as two orders of magnitude higher than for thermal oxide. The quality of the SiO<sub>2</sub>/Si interface has direct impact on the threshold voltage and mobility of the TFT. Therefore, the development of a

low-temperature CVD oxide with a D<sub>it</sub> close to that of thermal oxide would be a significant research contribution.

Poly-Si TFTs have generated a great deal of attention in the past decade, on account of their high performance and potential for unprecedented system integration. The business of information displays is growing rapidly, and the next section describes some of the leading trends in the display industry.

## 1.3 Display Industry Trends

The need for displayed information is growing with the increasing number of electronic devices. This demand has led to a few major trends in the flat panel display industry.

The first trend is toward lower power displays. Reflective display technologies such as reflective LCs will become increasingly important. However, passive-matrix reflective LC displays with simple multiplexed addressing schemes cannot be used because of their broad-transition electro-optic characteristic. Unless significant improvements are made in the LC material itself, active-matrix addressing will be required for high-resolution, reflective LC displays.

Secondly, there is a trend toward lower cost, larger area displays. OLED displays are a promising technology to address this need. Active-matrix addressing is also required for OLEDs because lifetime and efficiency degrade at high operating brightness. Passive-matrix OLEDs use a short, high current pulse scheme to drive OLEDs at low efficiency levels, which results in short lifetimes for the organic materials. <sup>12</sup> The active-

matrix addressing scheme provides a constant current to the pixel, reducing the power requirement and prolonging the OLED lifetime.

The third trend is toward lighter, more robust and compact displays for mobile electronics, where monolithic integration of driver circuitry is necessary to have highly portable rollup or foldable displays. To meet these demands, a high-performance transistor technology that is compatible with flexible substrates is needed. The ability to fabricate poly-Si TFTs on plastic substrates is critical to the achievement of these goals.

## 1.4 Organization

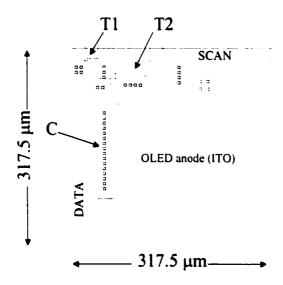

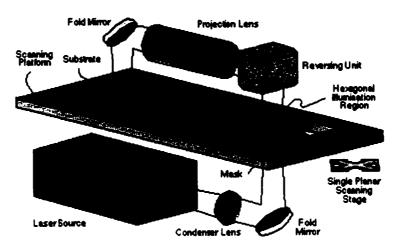

This dissertation addresses issues for direct fabrication of poly-Si TFTs on flexible plastic substrates. The formation of high-quality gate dielectrics at ultra-low temperatures (≤150°) is a critical step in the achievement of a high-performance TFT-on-plastic technology. Chapter 2 presents two methods for depositing low interfacial defect density SiO₂ using high-density plasma (HDP) CVD tools, namely electron cyclotron resonance (ECR) and helicon sources. We fabricated simple NMOS capacitors using an aluminum gate material and performed capacitance measurements for various deposition conditions. The highest-quality gate dielectrics were then selected for use in ultra-low temperature poly-Si TFT fabrication described in Chapter 3. This chapter presents the specific process methods used: sputtered a-Si, excimer laser annealing for poly-Si formation, ECR and helicon source PECVD oxide deposition, and laser-assisted source/drain formation. In Chapter 4, we present a method for improving poly-Si TFT uniformity by controlling grain growth using excimer laser crystallization. A patterned, anti-reflective oxide capping layer was used to align large-grained poly-Si to the active

channel region. N- and p-channel TFTs were fabricated using various laser fluences and compared. Chapter 5 describes an active-matrix organic light-emitting diode (AMOLED) prototype display designed in collaboration with Universal Display Corporation. The 128-by-64 pixel prototype utilizes a 2-TFT pixel design, and the fabrication process was designed to integrate seamlessly with backend OLED deposition. Lastly, in Chapter 6, a method for simplifying conventional lithography methods for large-area electronics manufacture is presented. We describe preliminary work on a direct patterning method using an excimer laser and Si<sub>x</sub>Ge<sub>1-x</sub> as a sacrificial material for transferring patterns without the use of resist and traditional optical lithography methods.

### 1.5 References

<sup>&</sup>lt;sup>1</sup> L.E. Tannas, Jr. (ed.), *Flat-Panel Displays and CRTs*, Van Nostrand Reinhold Company Inc., New York, 1985

<sup>&</sup>lt;sup>2</sup> http://www.cnet.com

<sup>&</sup>lt;sup>3</sup> http://www.dlp.com, Texas Instruments Digital Light Processing

<sup>&</sup>lt;sup>4</sup> from Flat Information Displays, Stanford Resources, Inc. 1997

<sup>&</sup>lt;sup>5</sup> P.M. Alt and P. Pleshko, "Scanning limitations of liquid-crystal displays," *IEEE Trans. Electron. Dev.*, vol. 21, no.2, 1974. pp.146-55.

<sup>&</sup>lt;sup>6</sup> I.-W. Wu, T.-Y. Huang, W.B. Jackson, A.G. Lewis, and A. Chiang, "Passivation Kinetics of Two Types of Defects in Polysilicon TFT by Plasma Hydrogenation," *IEEE Elec. Dev. Lett.*, vol. 12, no. 4, 1991, pp.181-183

- <sup>7</sup> R. Kingi, Y. Wang, S.J. Fonash, O. Awadelkarim, and J. Mehlhaff, "Comparison between rapid thermal and furnace annealing for a-Si solid phase crystallization," *Flat Panel Display Materials II Symposium* (1997) p. 237

- <sup>8</sup> S.D. Brotherton, J.R. Ayres, M.J. Edwards, C.A. Fisher, C. Glaister, J.P. Gowers, D.J. McCulloch, and M. Trainor, "Laser crystallized poly-Si TFTs for AMLCDs," *Thin Solid Films*, vol. 337, no.1-2, 1999, p. 188

- <sup>9</sup> S. Usui, T. Sameshima, and M. Hara, "The transformation of a-Si:H into polycrystalline silicon by excimer laser irradiation and its application to TFTs," *Optoelectronics Devices and Technologies*, vol.4, no.2, 1989, pp.235-48.

- N.D.Young, R.M.Bunn, R.W. Wilks, D.J.McCullough, G.Harkin, S.C.Deane, M.J.Edwards, and A.D.Pearson, "AMLCDs and electronics on polymer substrates," *in EURO Display* '96, pp. 555-558, 1996.

- <sup>11</sup> J.S. Im, H.J. Kim, M.O. Thompson, "Phase transformation mechanisms involved on excimer laser crystallization of amorphous silicon films," *Applied Physics Letters*, vol. 63, no.14, 1993. pp.1969-71.

- <sup>12</sup> T-J. King, "Poly-Si TFT Technologies for Future Flat-Panel Displays," *Proceedings of the 20<sup>th</sup> Int. Display Research Conference*, September 2000, pp. 406-410

## Chapter 2

# **Ultra-Low Temperature Gate Dielectric**

## **Formation**

## 2.1 Introduction

Much of the success of modern microelectronics can be attributed to the inherent ability of Si to form a stable, high-quality dielectric of silicon dioxide (SiO<sub>2</sub>) on its surface. Silicon dioxide (referred to as simply "oxide") grows readily on a bare Si surface, even at room temperature in air. In very-large-system-integration (VLSI) integrated circuits (ICs), oxide is commonly formed by thermal oxidation, a high-temperature ( $\ge 00^{\circ}$ C) process that uses either O<sub>2</sub> (dry) or H<sub>2</sub>O (wet) ambients. The elevated temperature supplies the energy needed for reactions to occur between the Si

surface atoms and the gaseous oxygen atoms, and the resulting oxide typically has an exact stoichiometric ratio (SiO<sub>2</sub>) and is strongly bonded to the Si surface. Thermally grown oxides have stable and controllable electrical properties, so they are the preferred gate dielectric for metal-oxide-semiconductor field-effect transistors (MOSFETs).

However, no oxide is electrically perfect or defect free. There are various types of traps and charges that exist in the bulk SiO<sub>2</sub> and at the Si-SiO<sub>2</sub> interface. These defects have a profound effect on the characteristics and performance of the devices fabricated in the underlying silicon. There are four basic types of charges that exist in the oxide itself or near the Si/SiO<sub>2</sub>: (1) interface trap charge, Q<sub>it</sub> (2) fixed oxide charge, Q<sub>f</sub> (3) bulk oxide trapped charge, Qot and (4) mobile ionic charge, Qm. The precise origin of the interface trap states is not well understood, but it is known that these trap states exist within the Si bandgap, and thus their charge state changes with gate bias if the interface trap is moved past the Fermi level, changing its occupancy. The fixed oxide charge is also associated with the Si/SiO<sub>2</sub> interface but is located in the oxide about 30-40Å away from the Si surface. Unlike Qit, the fixed oxide charge occupies energy levels outside the bandgap and does not change charge state with applied bias. Bulk oxide trapped charge can be located anywhere in the oxide and is associated with defects, such as impurities and broken bonds. All the charge types discussed so far can be effectively reduced by annealing the oxides at elevated temperatures. Only the mobile ionic charge is essentially independent of process temperature; Q<sub>m</sub> is commonly caused by the presence of ionized alkali metal atoms, such as Na<sup>+</sup> and K<sup>+</sup>, and can be reduced with a cleaner deposition system.

Oxide quality depends strongly on both the method of formation and post-formation annealing. Other than thermal oxidation, oxide can be formed by low-pressure chemical vapor deposition (LPCVD), plasma-enhanced CVD (PECVD) and physical vapor deposition (sputtering). In VLSI applications, CVD oxides have found extensive use for insulation between layers of interconnect, as getters, as diffusion sources, as diffusion and implantation masks, as capping layers to prevent outdiffusion, and as final passivation layers. But deposited oxides are generally of much lower quality than those that are thermally grown. Thus, CVD oxides are rarely used as gate dielectrics in VLSI devices.

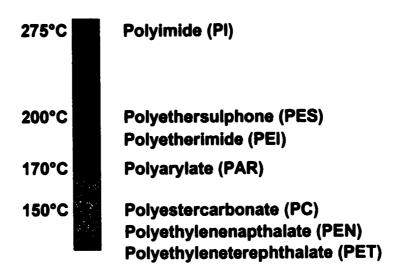

Polycrystalline silicon (poly-Si) thin-film transistors (TFTs) fabricated on plastic substrates *must* use gate dielectrics formed by low temperature deposition. SiO<sub>2</sub> is also the preferred dielectric because it can form a better interface with Si than other options such as silicon nitride. Plastic has a very low strain point; the most advanced polymer substrates can only tolerate a maximum process temperature of ~200°C (see Chapter 3 for details), so the preferred method of thermal oxidation is impossible. LPCVD SiO<sub>2</sub> requires temperatures in excess of 350°C, which is also incompatible with plastic. Sputtering of SiO<sub>2</sub> can be done as low as room temperature, but interface quality is typically poor and impurities from the chamber walls can easily be incorporated into the oxide film. Conventional radio frequency (13.56 MHz) (RF) PECVD can be used to deposit oxides at temperatures down to 100°C, but the quality of the Si/SiO<sub>2</sub> interface generally decreases with decreasing deposition temperature, resulting in poor TFT performance and reliability. It has been shown that RF PECVD oxide formed below 250°C results in dramatically degraded poly-Si TFT performance.<sup>3</sup> High-density plasma

(HDP) processing is the best method of attaining high-quality Si/SiO<sub>2</sub> interfaces at ultralow, plastic-compatible temperatures (<150°C).

In this chapter, we describe two types of HDP systems (electron cyclotron resonance (ECR) PECVD and helicon source PECVD). We present electrical data for oxides deposited at temperatures compatible with plastic substrates using these tools. The work presented in this chapter provides an optimum gate dielectric for the ultra-low temperature fabrication of poly-Si TFTs described in Chapter 3.

## 2.2 Electron Cyclotron Resonance PECVD

## 2.2.1 Background and System Configuration

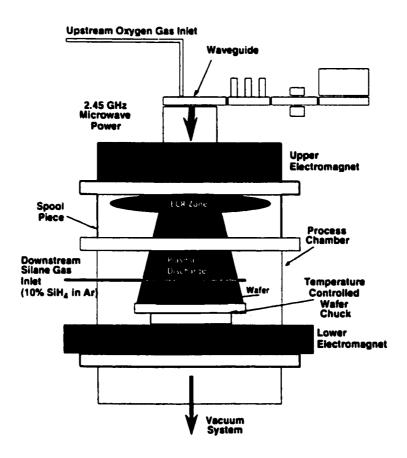

ECR PECVD allows for low temperature deposition of high quality thin oxide films. Using a microwave power source and electromagnets, high-reactivity plasmas can be generated under ECR conditions.<sup>4</sup> High densities of low-energy ions enhance surface reactions without the need for substrate heating. ECR systems can generate plasma densities as high as  $5 \times 10^{12}$  cm<sup>-3</sup>, which are 2-3 orders of magnitude higher than those achievable in RF PECVD tools.<sup>5</sup> Figure 2.1 shows a schematic of the ECR PECVD system used in this work.

The ECR reactor uses an electromagnet that produces a magnetic field for the resonance zone near the top of the chamber, where the 2.45GHz microwaves are injected. Oxygen and dilution gas mixtures are delivered into the ECR source and a high-density plasma is formed. The wafer sits on a graphite chuck in the lower portion of the chamber, and silane (SiH<sub>4</sub>) is injected directly above the wafer. Oxygen ions diffuse from the ECR

zone toward the substrate and dissociate the SiH<sub>4</sub>, which react with the oxygen to form  $SiO_2$  on the wafer. The spool piece distances the ECR zone from the wafer surface, improving uniformity and reducing substrate temperature heating. The lower magnet was not used in the experiments, since its use worsened uniformity without providing any noticeable benefit in the deposited film quality. Although the substrate was not deliberately heated, the temperature increased due to the ion bombardment during deposition. Typically, the base pressure of the system was  $\sim 8 \times 10^{-8}$  torr. Gases available in the ECR chamber were SiH<sub>4</sub>, Ar, O<sub>2</sub>, and N<sub>2</sub>.

Figure 2.1. Schematic diagram of the ECR PECVD system.

## 2.2.2 Experiments

A number of experiments were carried out in the ECR PECVD system to determine the best conditions for gate oxide deposition without substrate heating. Optimum conditions were determined by systematically varying the following parameters: microwave power, reactant gases, gas flow rates, and deposition time. The wafer surface temperature was measured for various deposition conditions to ensure compatibility with plastic substrates. The studies are described below and their results are presented. Since we use the deposited oxides as the gate dielectric in poly-Si TFTs, we are interested chiefly in their electrical characteristics. Thus, we fabricated simple test capacitors on lightly doped Si wafers by depositing blanket oxides to a thickness of 1000Å and then patterning aluminum gates on top of the oxide films to form capacitors of various sizes. We measured the high-frequency (100kHz) capacitance-voltage (CV) and current-voltage (IV) characteristics of the capacitors to determine the oxides' suitability for use in poly-Si TFTs.

#### ECR vs. LPCVD LTO and RF PECVD oxides

In the first experiment, we used an existing oxide deposition recipe (which we will refer to as the "standard" recipe), which had been optimized for superconductor IC fabrication. Dielectrics used in superconducting ICs have similar deposition temperature requirements as those used with polymer substrates. The parameters for the "standard" ECR oxide recipe are shown in Table 2.1.

| PARAMETER                  | VALUE    |

|----------------------------|----------|

| Power                      | 350W     |

| SiH <sub>4</sub> flow rate | 100 sccm |

| O <sub>2</sub> flow rate   | 20 sccm  |

| Ar flow rate               | 120 sccm |

| Pressure                   | 5 mTorr  |

Table 2.1. "Standard" ECR oxide deposition parameters. These were the parameters for the first ultra-low temperature gate oxide experiment. They do not reflect the optimum deposition conditions.

In this initial experiment, the quality of the standard ECR oxide was compared with oxides deposited using LPCVD at 450°C and RF PECVD at 100°C. Capacitors were fabricated on lightly doped n-type Si wafers in the following manner. First, the Si wafer was cleaned and placed in an HF bath to remove all native oxide. Immediately following the HF dip, the wafer was placed in the deposition chamber, and oxide was deposited to a thickness of 1000Å. The blanket film was then capped with 3000Å of sputtered Al. These thicknesses were chosen to be representative of the gate dielectric and metal thicknesses used in the TFTs. Lithography and etching defined squares in the Al film that determined the capacitor size. The backside of the wafer served as the bottom electrode of the capacitor.

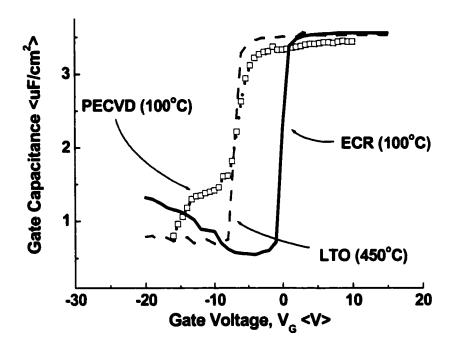

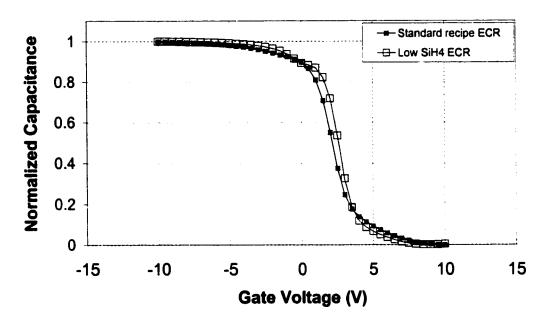

High-frequency CV measurements were performed on the completed capacitors. Figure 2.2 compares the CV curves for the 450°C LPCVD oxide (LTO), the unheated pure ECR oxide, and the 100°C pure PECVD oxide. The ECR oxide exhibits steep characteristics similar to that of the 450°C LTO, demonstrating that a similar quality Si/SiO<sub>2</sub> interface is achieved with ECR. The shallow slope of the PECVD oxide CV

Figure 2.2. High-frequency CV characteristics for 450°C LPCVD, 100°C PECVD and 100°C ECR oxides (0.1μm thick). The ECR oxide exhibits a silicon-oxide interface quality superior to that of PECVD oxide and close to that of the LTO.

characteristic indicates a higher density of interface trap states. Variations in capacitance values are due to slight differences in oxide thickness arising from process variation.

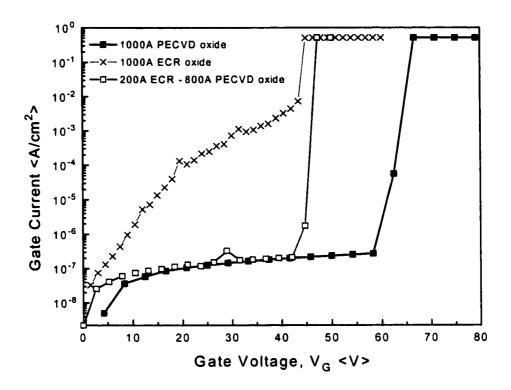

Unfortunately, the IV characteristics of the ECR oxide indicate that it has poor bulk properties. Figure 2.3 shows leakage characteristics and breakdown voltages of the devices. The pure ECR oxide exhibits excessive leakage current even at moderate values of gate voltage, and it also has an unsatisfactorily low V<sub>bd</sub>. The largest breakdown voltage is achieved with a pure PECVD oxide. Through the use of a composite ECR/RF-PECVD oxide (200Å/800Å), both good interface quality and acceptable leakage current can be achieved. The composite ECR-PECVD oxide CV characteristic is shown in Figure 2.3. It has a lower breakdown voltage than that of pure PECVD oxide, but the breakdown field is still >4 MV/cm.

Figure 2.3. Comparison of oxide breakdown voltages. The ECR-PECVD stack shows superior leakage current characteristics to a pure ECR oxide, but smaller breakdown voltage than pure PECVD oxide.

#### Improvement of ECR oxide leakage current

The standard oxide deposition recipe in the ECR system yielded a porous, electrically leaky film. It was unlikely that the ECR system inherently produces such high leakage oxides, so we aimed to improve the bulk properties of the oxide without adversely affecting the good interface properties. The starting point for the experiment was to lower the silane flow rate, because a lower deposition rate leads to a denser, less porous oxide. The lowest SiH<sub>4</sub> flow rate possible was found to be 40sccm. Below this point, the plasma was unstable and the reflected power fluctuated wildly. (For silane flow rates between 60-100 sccm, there was no appreciable change in the oxides.) Next, we

replaced Ar with  $N_2$  as the carrier gas. It was reported that ECR  $N_2O$  plasma oxides grown on poly-Si had the effect of smoothing the interface with poly-Si.<sup>6</sup> Because our system did not have  $N_2O$  available,  $N_2$  was flowed at twice the rate of  $O_2$ , so that the relative densities of reactant ions would be similar. Lastly, the power was increased. We found that it was necessary to run the plasma at powers  $\geq 500W$  to see improvements in the oxide. The pressure was kept as low as possible ( $\sim 5mTorr$ ) to maintain a high plasma density.<sup>5</sup> Table 2.2 shows the parameters for the low leakage, low SiH<sub>4</sub> flow rate oxide.

| PARAMETER                  | VALUE    |

|----------------------------|----------|

| Power                      | >500W    |

| SiH <sub>4</sub> flow rate | 40 sccm  |

| O <sub>2</sub> flow rate   | 75 sccm  |

| N <sub>2</sub> flow rate   | 150 sccm |

| Pressure                   | 5 mTorr  |

Table 2.2. Low SiH<sub>4</sub> flow rate ECR oxide recipe. The above conditions yield an oxide that has leakage characteristics similar to that of 450°C LPCVD LTO.

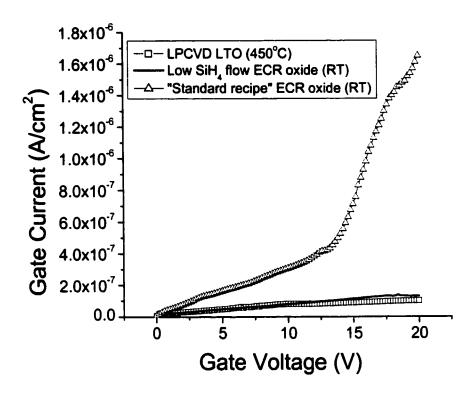

Simple Al-gate capacitors were fabricated using this new recipe (1000Å oxide thickness) and compared with the standard ECR oxide and 450°C LTO. Figure 2.4 shows the oxide leakage characteristics. The new low SiH<sub>4</sub> flow rate recipe yields an oxide with leakage characteristics comparable to LTO, while the leakage current of the standard recipe exceeds both.

Figure 2.4. Improvement in leakage current with new, low-SiH<sub>4</sub>, N<sub>2</sub>, O<sub>2</sub> gas flow recipe in the ECR system. The low leakage oxide was deposited at 500W microwave power using the gases listed in Table 2.2.

Interface characteristics achieved with the low leakage oxide were similar to those seen using the standard recipe. Figure 2.5 compares the CV curves for capacitors fabricated using the standard ECR oxide and the low leakage ECR oxide recipe. The substrate was a lightly doped p-type Si wafer. Comparable interface quality is achieved for the two ECR oxides.

Figure 2.5. No loss in interface quality is seen with the new low SiH<sub>4</sub> flow rate ECR oxide. LTO contains some fixed charge that causes the shift towards positive gate voltages.

One disadvantage of using a low silane flow rate is that the deposition time increases. The new low leakage oxide recipe lengthened the required deposition time by nearly five times. At 800W, the ECR plasma can cause the substrate temperature to rise substantially, especially if the run time is long. It was important to know whether the temperature rise led to the observed improvement in oxide quality. The temperature study is explained in a later section.

## Oxygen Plasma Pre-Treatment

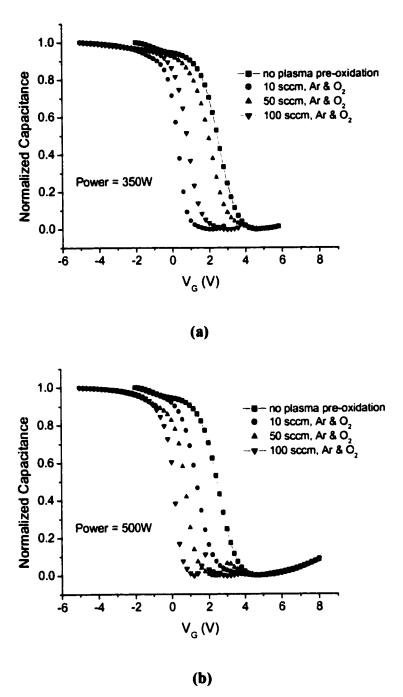

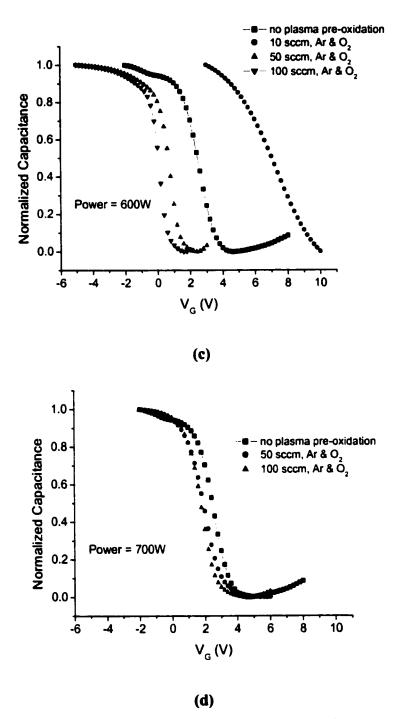

The effect of pre-treating the Si surface with oxygen plasma prior to oxide deposition was investigated. O<sub>2</sub> and Ar were flowed at equal rates (O<sub>2</sub>=Ar=10, 50, and 100 sccm), and power was varied (350, 500, 600, 700W) to determine the impact on the interface quality. The oxygen plasma pre-treatment was run for 120 seconds, and then it

was followed by deposition of standard recipe ECR oxide to a thickness of 1000Å. Figure 2.6a-d shows the CV characteristics for capacitors fabricated using the described splits.

Figure 2.6 (a) & (b). continued on next page

Figure 2.6 (c) & (d). CV characteristics for ECR oxygen plasma pre-treated oxide capacitors. Microwave power was varied from (a) 350W, (b) 500W, (c) 600W to (d) 700W, and the oxygen plasma was run for 120 seconds in all cases. The optimum condition for  $O_2$  plasma pre-treatment was found to be with  $O_2$ =Ar=100sccm at 500-600W.

The benefit of an oxygen plasma pre-treatment step is seen for nearly all ECR conditions. The anomalous result for 10sccm gas flows at 600W is due to plasma instability. At such low gas flows, the plasma had difficulty sustaining itself and the reflected power was highly unstable. The problem was only exacerbated at 700W, where the gas flows of O<sub>2</sub>=Ar=10sccm was too low to even strike a plasma. The best characteristics are seen for 100sccm gas flows around 500-600W of microwave power. At these conditions, the CV characteristics are steep and the flatband voltage is low (desirable for low TFT threshold voltage).

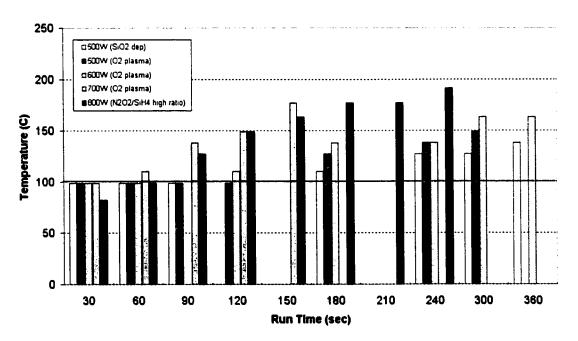

## Wafer Surface Temperature in ECR Chamber

Under ion bombardment, the surface temperature of the wafer rises. An experiment was carried out to quantify the substrate heating in the ECR chamber. Temperature-sensitive adhesives were mounted on Si wafers, and various plasma conditions were run in the ECR chamber. The stickers changed color when their designated temperature was reached, and through the use of assorted dots (i.e. sensitive at 99°C, 110°C, 116°C, 127°C, 138°C, 149°C, 163°C, and 177°C), the temperature was measured as a function of time for given plasma conditions. For microwave power levels up to 350W, the wafer surface did not exceed 150°C (the T<sub>g</sub> of a common plastic, polyethylene terephthalate or PET) even for depositions that lasted several minutes. Since the optimum oxide formation process sequence required power ≤00W, extra care was taken to ensure that the use of higher power levels does not cause the substrate temperature to exceed 150°C.

The processes that require high power are the oxygen plasma pre-treatment and the reduced SiH<sub>4</sub> flow rate, low leakage recipe. Figure 2.7 shows the evolution of temperature in the system as a function of run time and recipe. A thick bar indicates the 100°C mark, which is the preferred maximum process temperature for poly-Si TFTs on plastic. (The gate dielectric deposition usually demands the highest sustained temperature in the poly-Si TFT fabrication process.) It is important to note, however, that these results are only an approximate indication of the actual substrate temperature: the temperature dots themselves have error; the surface temperature differs considerably from the temperatures at substrate depths; lastly, the thermal conductivity of the Si wafer is significantly higher than glass or plastic. For TFT fabrication on silicon substrates, these data represent the worst case temperature rise.

Figure 2.7. Wafer temperature in the ECR PECVD system as a function of time. Surface temperature is also a function of the particular recipe, since gas flows and pressures vary.

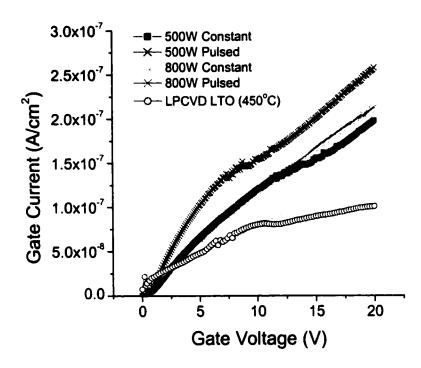

Figure 2.8. Leakage current as a function of pulsed vs. constant mode deposition in the ECR PECVD system. Oxide thickness is 100nm.

It can be seen from the figure that, for most plasma conditions, the surface temperature exceeds 100°C after 120 seconds. Thus, it is necessary to use a pulsed mode operation for depositions or treatments requiring longer times. Pulsed mode depositions break up the plasma run time into smaller durations with lag times, so that substrate cooling can occur.

Pulsed mode deposition was performed for the low leakage oxide recipe. The cycle executed as follows: gas stabilization (60 sec), deposition (150 sec), and cooling (60 sec of 50 secm N<sub>2</sub>). Results are shown in Figure 2.8 for 100nm-thick oxides. The pulsed mode deposited oxides have slightly higher leakages for both 500W and 800W depositions, but the leakage currents are tolerable. The CV characteristics were indistinguishable for pulsed mode vs. constant mode depositions. Thus, pulsed mode

deposition is a viable method to achieve high-quality, low temperature oxides. The obvious disadvantage is the longer process times required.

## 2.3 Helicon Source PECVD

## 2.3.1 Background and System Configuration

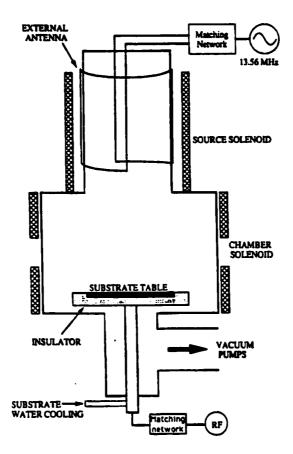

Typical plasma density values for helicon source plasmas are roughly 1x10<sup>13</sup> – 5x10<sup>13</sup> cm<sup>-3</sup>, which is about an order of magnitude higher than typical ECR plasma densities.<sup>7</sup> The helicon source PECVD reactor uses an RF frequency (13.56 MHz) antenna to couple power into the plasma. As shown in Figure 2.9, the antenna consists of two loops placed diametrically on the outside of the source chamber. This antenna produces a transverse RF magnetic field perpendicular to both the main chamber axis and the constant axial magnetic field generated by the solenoids shown in the figure. The RF field excites one mode of the helicon wave in the source tube, which in turn transfers energy to the plasma electrons. Various frequencies ranging from 2 to 70 MHz can be used with excellent results, but the use of 13.56 MHz is historically practical and has the added benefit of giving a plasma wavelength of 22cm, a convenient size for reactor geometry.<sup>8</sup>

Gases were introduced into the chamber in a configuration nearly identical to that of the ECR system, but with only O<sub>2</sub> and SiH<sub>4</sub> available. Oxygen gas entered the chamber at the top of the source tube where the helicon plasma was generated. Silane was flowed evenly over the wafer using a gas distribution ring that was located approximately 3 cm

Figure 2.9. Schematic diagram of the helicon source PECVD process chamber (from A.J. Perry et al., J. Vac. Sci. Technol., B 9 (2), 1991). Missing from the diagram is the SiH<sub>4</sub> ring that evenly distributes the gas from a distance of ~3cm from the surface of the substrate.

above the wafer. Typical process pressures were in the 1 to 12 mTorr range, with exact values depending on the gas flow rates and turbo valve aperture.

#### 2.3.2 Experiments

A variety of helicon chamber process conditions were run to determine the best achievable oxide interface and bulk characteristics. Initially, experiments were run to determine the maximum possible power that could be used with plastic substrates. Wafers cut from 175µm-thick PET were placed in the chamber and the plasma was run for 10 minutes at 400W, 500W, 600W, and 700W. SiH<sub>4</sub> and O<sub>2</sub> were introduced into the

chamber at the equal rate of 10sccm. The plastic suffered no damage, even when run at 700W for 10 minutes. The separation between the helicon resonance zone and the wafer itself is approximately 40cm, so the physical ion bombardment is relatively low. All subsequent experiments were performed at 700W to achieve the highest possible plasma density.

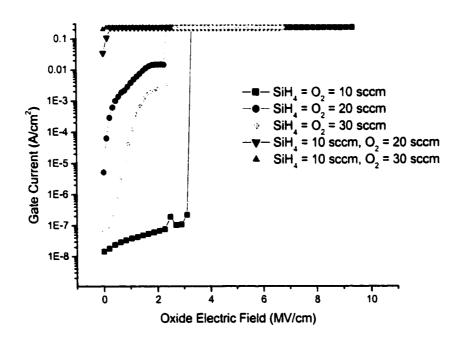

Since ECR and helicon sources generate plasmas with similar characteristics, the main objective was first to develop a dense, low leakage oxide. Blanket oxides were deposited on Si wafers, and oxide characteristics were measured using a mercury probe. Figure 2.10 shows the leakage currents for oxides deposited using various gas flows and SiH<sub>4</sub>/O<sub>2</sub> ratios. Increasing oxygen flow has the effect of increasing the deposition rate, leading to porous, leaky oxides. However, the pressure was a variable in the experiment because the pumping speed remained the same for all gas flows.

Figure 2.10. Leakage characteristics for helicon oxides deposited on Si wafers using the indicated gas flows. 100nm-thick oxides were deposited at 700W without substrate heating.

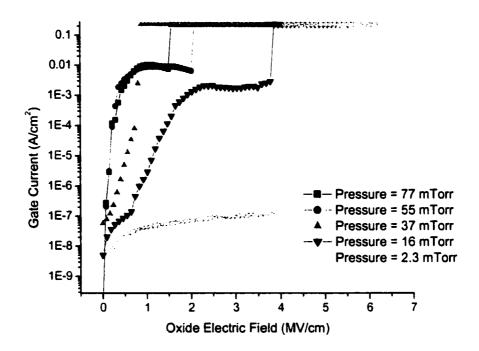

An experiment was then performed to determine the effect of pressure on leakage current. Using the best result from Figure 2.10 (SiH<sub>4</sub>=O<sub>2</sub>=10 sccm), the turbo pump valve aperture was systematically adjusted to control the pressure in the chamber during deposition. Figure 2.11 shows the leakage currents for oxides deposited at five different pressures. Leakage increases monotonically with pressure, so it is best to use the lowest possible chamber pressure. In the helicon system, this condition is achieved by flowing silane and oxygen at 10sccm and fully opening the turbo pump valve.

Figure 2.11. Leakage characteristics for helicon oxides deposited at various pressures. (SiH<sub>4</sub>=O<sub>2</sub>=10sccm; power=700W; T<sub>ox</sub>=100nm)

Similar to the ECR system, oxygen plasma pre-treatment in the helicon system improves interface quality. Plasma oxidation of Si wafers was performed at low pressure (2.5mTorr, 20sccm O<sub>2</sub> flow) and high power (700W) for various durations. Then, the thin oxides were capped with 100nm-thick 100°C RF PECVD oxides for testing. CV

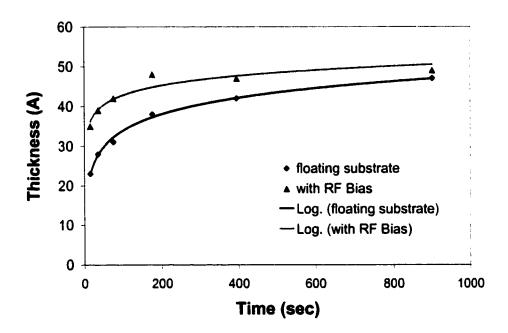

characteristics for this experiment are shown in Figure 2.12 (w/o RF substrate bias) and 2.13 (w/ RF substrate bias). After approximately 6.5 minutes of plasma oxidation, there is no further improvement. Measurement of the thin oxide shows a logarithmic growth curve (Figure 2.14), where little change in oxide thickness occurs after 400 seconds (~6.5 minutes). There is no added benefit to longer plasma oxidation durations, only possible downsides such as temperature elevation, plasma damage, etc. The use of RF bias on the substrate does not change the oxide quality significantly, but it changes the shape of the plasma so that thickness uniformity is degraded slightly. These results indicate that the use of RF bias is not necessary.

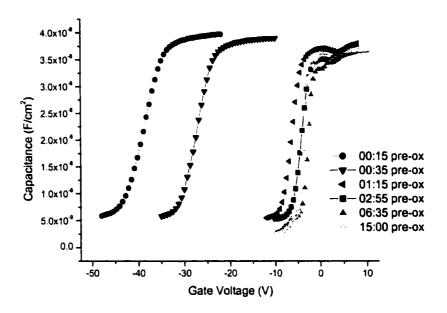

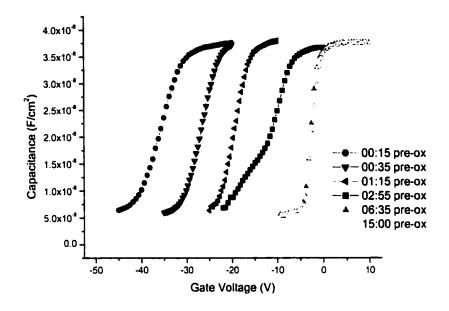

Figure 2.12. Effect of helicon plasma pre-oxidation on interface quality. No improvement is seen after 6:35 of oxygen plasma treatment. Plasma conditions: Pressure=2.5mTorr, O<sub>2</sub>=20sccm, Power=700W, no RF bias.

Figure 2.13. Same as Figure 2.12, but with RF substrate bias (-55V DC). Plasma conditions: Pressure=2.5mTorr, O<sub>2</sub>=20sccm, Power=700W, with RF bias.

Figure 2.14. Helicon plasma oxidation growth curve. (Same oxygen plasma conditions as in Figure 2.12.) Little growth occurs after 400 seconds, corresponding to the limit on interface improvement as seen in Figure 2.12. The solid lines are a logarithmic fit to the measured data points.

## 2.4 References

- <sup>1</sup> S. Wolf and R.N. Tauber, Silicon Processing for the VLSI Era, Volume 1 Process Technology, Lattice Press, 1986

- <sup>2</sup> R.S. Muller and T.I. Kamins, *Device Electronics for Integrated Circuits*, Wiley & Sons, 1986

- <sup>3</sup> N.D.Young, R.M.Bunn, R.W. Wilks, D.J.McCullough, G.Harkin, S.C.Deane, M.J.Edwards, and A.D.Pearson, "AMLCDs and electronics on polymer substrates," *in EURO Display '96*, pp. 555-558, 1996.

- <sup>4</sup> F. Plais, B. Agius, F. Abel, J. Siejka, M. Puech, G. Ravel, P. Alnot, and N. Proust, "Low Temperature Deposition of SiO<sub>2</sub> by Distributed Electron Cyclotron Resonance Plasma-Enhanced Chemical Vapor Deposition," *J. Electrochem. Soc.*, Vol. 139, No. 5, May 1992

- <sup>5</sup> J. Asmussen, "Electron cyclotron resonance microwave discharges for etching and thinfilm deposition," J. Vac. Sci. Technol., A 7(3), pp. 883-93, May/Jun 1989

- <sup>6</sup> N-I. Lee, J-W. Lee, S-H. Hur, H-S. Kim, and C-H. Han, "Highly Reliable Polysilicon Oxide Grown by Electron Cyclotron Resonance Nitrous Oxide Plasma," *IEEE Electron Device Lett.*, Vol. 18, no. 10, pp. 486-8, 1997.

- <sup>7</sup> A. Komori, T. Shoji, K. Miyamoto, J. Kawai, and Y. Kawai, "Helicon waves and efficient plasma production," *Phys. Fluids B*, vol.3, no.4, pp. 893-898, April 1991.

- <sup>8</sup> A.J. Perry, D. Vender, and R.W. Boswell, "The application of helicon source to plasma processing," *J. Vac. Sci. Technol.*, B 9 (2), pp. 310-7, 1991

# Chapter 3

# **Ultra-Low Temperature Fabrication of**

# **Poly-Si TFTs**

## 3.1 Introduction

Flat-panel displays that are high-resolution, low power, lightweight, rugged, and portable will be well suited for wide ranging applications in both military and commercial sectors. If the feature of flexibility in displays were added, a vast array of entirely new markets could be created. The development of a high-performance active-matrix technology that is adaptable to plastic substrates is critical to achieving this vision for the future. In this chapter, a method for fabricating high-performance poly-Si TFTs at a maximum process temperature of 100°C is described. This process was demonstrated to

yield the highest performance TFTs for any technology compatible with polyester substrates, at the time of the work.

### 3.1.1 Polymer substrates: Advantages and Disadvantages

The primary advantages of plastic substrates with respect to glass are a reduction in the weight of the display and an alleviation of the problem of display breakage<sup>1</sup>, both during fabrication and use. Plastic substrates are also significantly cheaper than the types of glass currently used in displays. The vast majority of plastics typically cost only cents per square foot while the cost of Corning Code 1737 glass, used in AMLCDs, is orders of magnitude higher. Another advantage for displays fabricated on plastic substrates is the potential to be more compact, since plastic thicknesses are usually <200µm, compared to 0.5mm for glass. Polymer substrates are also an ideal platform for the development of ultra-large displays, such as those used in advertising and other large-scale information systems, due to their compatibility with roll-to-roll processing.

Clear plastic substrates would therefore appear to be a superb alternative to glass. However, the introduction of plastic into a poly-Si TFT fabrication process has its attendant disadvantages. Standard processing techniques for both amorphous and polycrystalline TFTs require temperatures far in excess of those compatible with commonly available plastics. The maximum standard processing temperatures ( $T_{max}$ ) of 350°C for conventional a-Si:H TFTs and 600°C for poly-Si TFTs are well above the glass transition temperature ( $T_G$ ) for most varieties of polymer substrates. Plastic also has poor thermal stability compared to glass; the coefficient of thermal expansion (CTE) for plastics generally range from 20-100x10<sup>-6</sup> °C<sup>-1</sup> while Corning Code 1737 glass has a CTE of 3.8x10<sup>-6</sup> °C<sup>-1</sup>, which is much closer to that of silicon (CTE of Si is 2.5x10<sup>-6</sup> °C<sup>-1</sup>). The

large thermal expansion mismatch can produce significant stress in the deposited Si (or SiO<sub>2</sub>) films when the samples are heated during processing. This has led some researchers to attempt to reduce the T<sub>max</sub> needed to fabricate a-Si:H TFTs with promising results<sup>2,3,4</sup>. It remains to be seen whether or not these modified processing techniques are readily transferable to commercial application. But for *poly-Si* TFTs, simple modifications of standard processing techniques to reduce the T<sub>max</sub> to one suitable for plastic substrates are clearly not feasible. Previously, the process barrier for poly-Si on plastic was dictated by the lowest temperature needed to crystallize a-Si using some form of solid-phase crystallization, e.g. conventional furnace annealing or rapid thermal processing (RTP).