#### Investigations of Tunneling for Field Effect Transistors

by

#### Peter Matheu

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Applied Science & Technology

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Tsu-Jae King Liu, Chair Professor Sayeef Salahuddin, Member AS&T Professor Chenming Hu, Outside Member

Spring 2012

#### Investigations of Tunneling for Field Effect Transistors

Copyright 2012 by Peter Matheu

#### Abstract

Investigations of Tunneling for Field Effect Transistors

by

Peter Matheu

Doctor of Philosophy in Applied Science & Technology

University of California, Berkeley

Professor Tsu-Jae King Liu, Chair

Over 40 years of scaling dimensions for new and continuing product cycles has introduced new challenges for transistor design. As the end of the technology roadmap for semiconductors approaches, new device structures are being investigated as possible replacements for traditional metal-oxide-semiconductor field effect transistors (MOSFETs). Band-to-band tunneling (BTBT) in semiconductors, often viewed as an adverse effect of short channel lengths in MOSFETs, has been discussed as a promising current injection mechanism to allow for reduced operating voltage for beyond MOSFET technology.

This dissertation discusses the proposal of BTBT for tunneling field effect transistors (TFETs). Some early work is briefly reviewed to better appreciate the academic research landscape regarding BTBT. Then, experimental observations of a steeply switching enhanced-Schottky-barrier MOSFET are analysed in detail and the steep characteristic is plausibly explained by metal impurity trap states near the source tunneling junction. Next, follow-up experiments to investigate the role of traps in BTBT are reviewed with a likely explanation that traps in close proximity to the tunneling junction can lower the activation energy for BTBT. Finally, a source design study for a planar homojunction germanium-on-insulator TFET finds that a static reverse bias can dramatically alter the optimal doping profile for the source tunneling junction and highlights the importance of tight electrostatic control for improved  $I_{\rm ON}/I_{\rm OFF}$  in TFETs.

To my family and friends.

For their continual support throughout my graduate school odyssey, most especially my parents and my siblings for their limitless patience and understanding.

# Contents

| Contents                  |                                        | ii                                 |                                |  |

|---------------------------|----------------------------------------|------------------------------------|--------------------------------|--|

| $\mathbf{Li}$             | $\operatorname{st}$ of                 | Figures                            | iv                             |  |

| List of Tables            |                                        |                                    | vi                             |  |

| 1                         | Intr<br>1.1<br>1.2<br>1.3<br>1.4       | CMOS Solid State Switching Devices | 1<br>1<br>2<br>4<br>5          |  |

| $\mathbf{B}^{\mathbf{i}}$ | bliog                                  | graphy                             | 7                              |  |

| 2                         |                                        | Introduction                       | 9<br>9<br>12<br>13<br>15<br>25 |  |

| $\mathbf{B}^{\mathbf{i}}$ | bliog                                  | graphy                             | 26                             |  |

| 3                         | Eng<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Introduction                       | 29<br>31<br>33<br>36<br>42     |  |

| $\mathbf{B}^{\mathbf{i}}$ | Bibliography                           |                                    |                                |  |

| 4            | $\mathbf{Erb}$ | ium Trap Assisted TFET                                                                       | 45         |

|--------------|----------------|----------------------------------------------------------------------------------------------|------------|

|              | 4.1            | Introduction                                                                                 | 45         |

|              | 4.2            | Experimental Design Goals                                                                    | 46         |

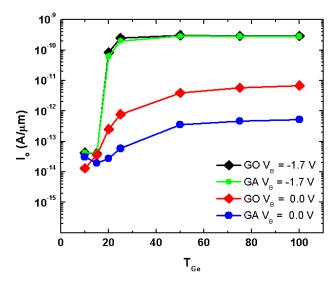

|              | 4.3            | Electrical Characterization and Temperature Dependence                                       | 47         |

|              | 4.4            | Conclusion                                                                                   | 53         |

| Bi           | bliog          | graphy                                                                                       | 55         |

| 5            | Des            | ign Optimization of Homojunction TFETs with Back Biasing                                     | 56         |

|              | 5.1            | Introduction                                                                                 | 56         |

|              | 5.2            | Simulation Structure to Investigate Lower $E_{\rm g}$ Materials for Planar Homojunction TFET | 58         |

|              | 5.3            | Planar GeOI TFET Performance Enhancement via Back Bias                                       | 60         |

|              | 5.4            | Conclusion                                                                                   | 69         |

| Bi           | bliog          | graphy                                                                                       | 70         |

| 6            | Cor            | nclusion                                                                                     | 72         |

|              | 6.1            | Summary of Contributions                                                                     | 72         |

|              | 6.2            | TFET Design Challenges                                                                       | 73         |

|              | 6.3            | Concluding Remarks                                                                           | 74         |

| Bi           | bliog          | graphy                                                                                       | <b>7</b> 5 |

| $\mathbf{A}$ | App            | pendix: Process Flow Template                                                                | <b>7</b> 6 |

# List of Figures

| 1.1  | MOSFET Schematic                                    | 1 |

|------|-----------------------------------------------------|---|

| 1.2  | MOSFET Operation                                    | 2 |

| 1.3  | MOSFET I-V Alternative                              | 4 |

| 2.1  | SB-MOSFET Schematic                                 | 0 |

| 2.2  | SB Band Diagram                                     | 1 |

| 2.3  | SB MOSFET Band Diagram                              | 1 |

| 2.4  | SB TFET Schematic                                   | 4 |

| 2.5  | Fabricated SB TFET                                  | 5 |

| 2.6  | Pocket SB-MOSFET                                    | 6 |

| 2.7  | Enhanced SB-MOSFET Initial Transfer Characteristics | 7 |

| 2.8  | Enhanced SB-MOSFET Transfer Characteristics         | 8 |

| 2.9  | Enhanced SB-MOSFET Activation Energy                | 9 |

| 2.10 | Enhanced SB-MOSFET Band Diagram                     | 0 |

| 2.11 | Enhanced SB-MOSFET $SS$                             | 1 |

|      | Enhanced SB-MOSFET I-V $(V_B)$                      | 2 |

|      | Enhanced SB-MOSFET $SS(V_B)$                        | 3 |

|      | Enhanced SB-MOSFET Output Characteristics           | 3 |

| 2.15 | Enhanced SB-MOSFET Output Characteristics           | 4 |

| 3.1  | Esaki Diode Band Diagram                            | 0 |

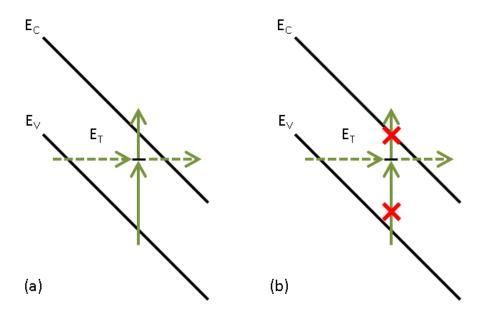

| 3.2  | Trap Assisted Tunneling Models                      | 0 |

| 3.3  | Trap Assisted Tunneling                             | 2 |

| 3.4  | Erbium Heterodiode Splits                           | 4 |

| 3.5  | Erbium Ion Implantation                             | 5 |

| 3.6  | Phosphorus n-well Split                             | 5 |

| 3.7  | p-i-n Heterodiode I-V                               | 7 |

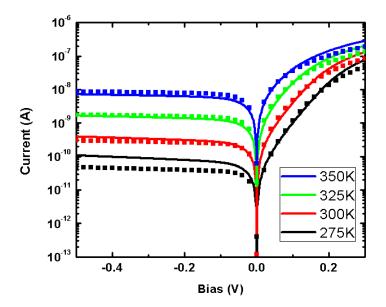

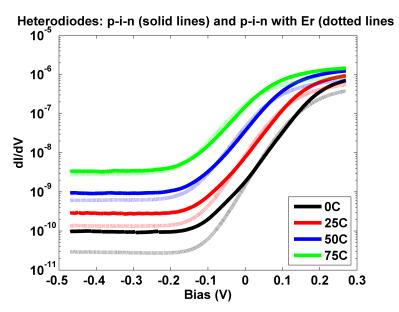

| 3.8  | p-i-n Heterodiode $dI/dV$                           | 8 |

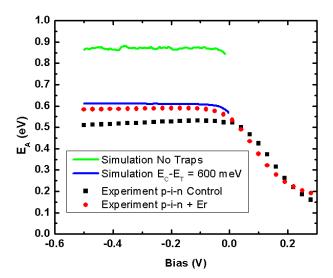

| 3.9  | Heterodiode $E_{\rm A}$                             | 9 |

| 3.10 | p+/n+ Heterodiode I-V(T)                            | 0 |

| 3.11 | p+/n+ Heterodiode Band Alignment                    | 1 |

|      | $p+/n+$ Heterodiode $E_{\Lambda}$                   | 1 |

| 4.1  | Er TATFET Cross-sectional Schematic                                     | 45 |

|------|-------------------------------------------------------------------------|----|

| 4.2  | Er TATFET Band Diagram                                                  | 46 |

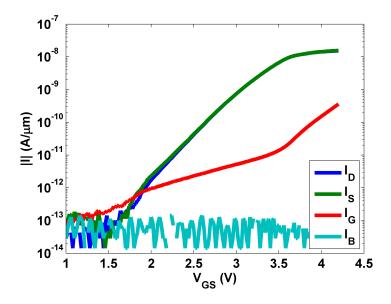

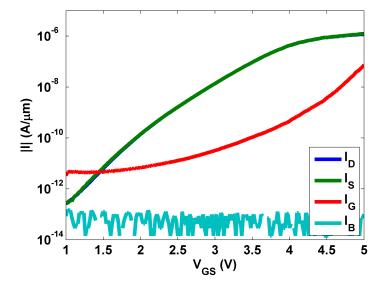

| 4.3  | Typical Transfer Characteristics for Er-TATFETs                         | 48 |

| 4.4  | Typical Transfer Characteristics for Control TFETs                      | 48 |

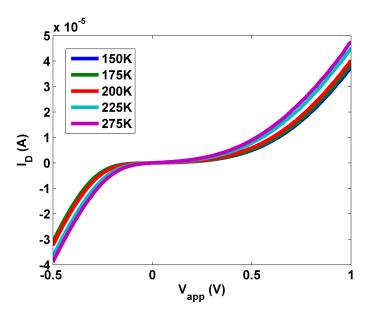

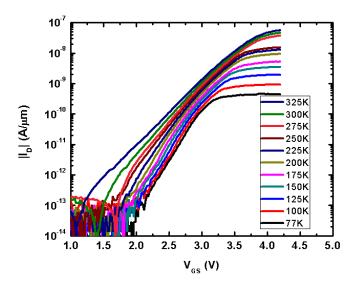

| 4.5  | Temperature Dependent Transfer Characteristics for an Er-TATFET         | 49 |

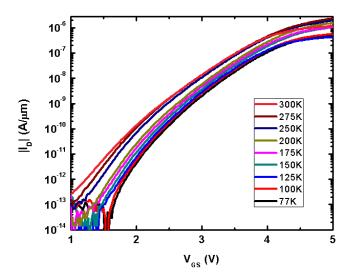

| 4.6  | Temperature Dependent Transfer Characteristics for a p-i-n Control TFET | 49 |

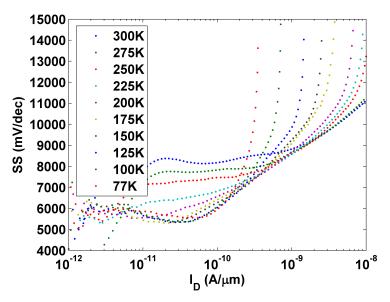

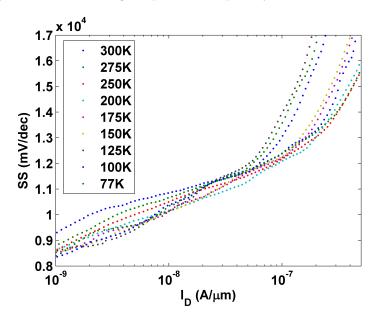

| 4.7  | SS for an Er-TATFET                                                     | 51 |

| 4.8  | SS for a Control TFET                                                   | 51 |

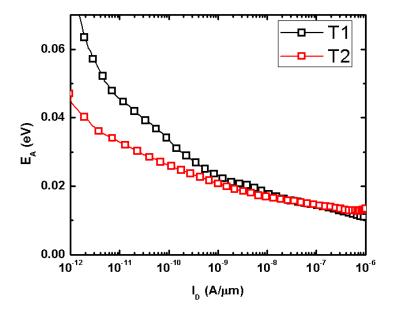

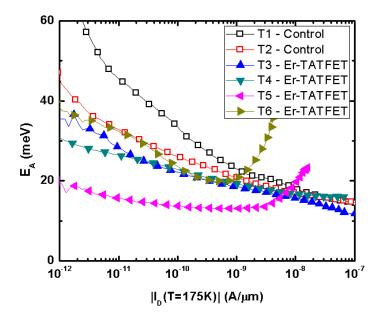

| 4.9  | $E_{\rm A}$ for p-i-n Control TFETs                                     | 52 |

| 4.10 | Activation Energy for Er-TATFETs                                        | 53 |

| 4.11 | Thought Experiment                                                      | 54 |

| 5.1  | Simulated SOI TFET Transfer Characteristics                             | 57 |

| 5.2  | Simulated SOI TFET $I_{\rm ON}/I_{\rm OFF}$                             | 58 |

| 5.3  | Enhanced SOI TFET Transfer Characteristics                              | 59 |

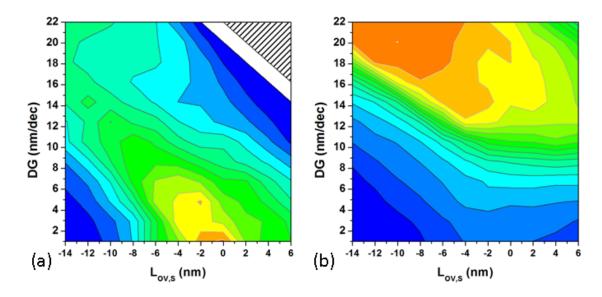

| 5.4  | GeOI Optimal Source Parameters for $I_{\rm ON}/I_{\rm OFF}$             | 61 |

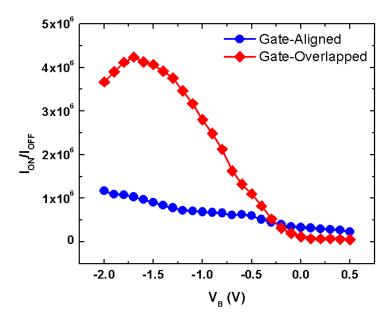

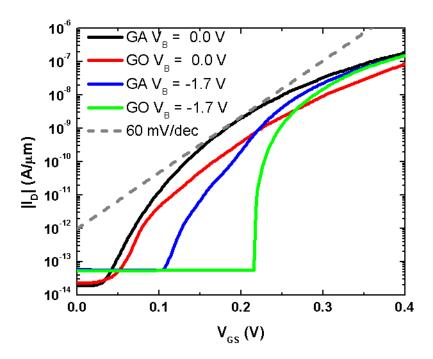

| 5.5  | Simulated GeOI $I_{\rm ON}/I_{\rm OFF}(V_{\rm B})$                      | 62 |

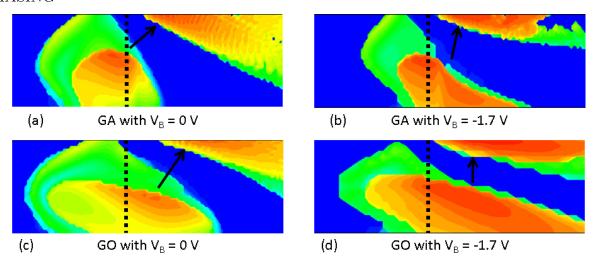

| 5.6  | Simulated GeOI BTBT Contours                                            | 63 |

| 5.7  | GeOI Transfer Characteristics                                           | 64 |

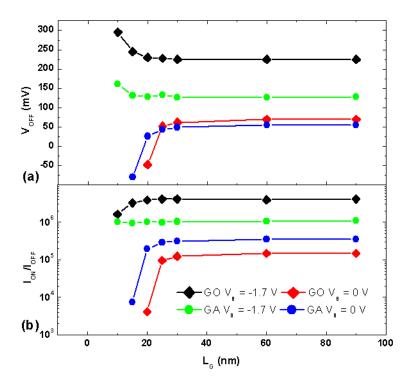

| 5.8  | GeOI TFET with $L_{ m G}$ Scaling                                       | 65 |

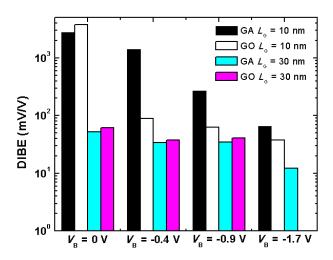

| 5.9  | GeOI TFET Drain Induced Barrier Effects                                 | 66 |

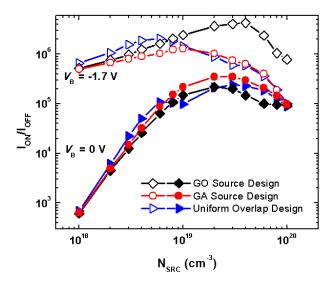

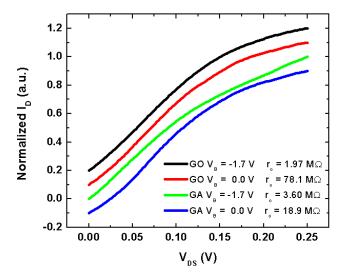

| 5.10 | GeOI TFET Source Design Overlap Comparison                              | 67 |

| 5.11 | Simulated GeOI TFET Output Characteristics                              | 68 |

| 5.12 | GeOI TFET Ge Body Thickness Dependence                                  | 68 |

# List of Tables

| 3.1 | Experimental heterodiode splits and rectifying device yield | 36 |

|-----|-------------------------------------------------------------|----|

| 4.1 | Transistor dimensions for control and experimental devices  | 50 |

#### Acknowledgments

I would like to acknowledge the support of my colleagues throughout my graduate academic career. My first advisor, Professor Edward T. Yu, was instrumental in guiding me in my early days as a researcher. His patience and keen eye towards analyzing my work will always be appreciated. I learned a great deal about research and the scientific method through my work with him and the other graduate students in his group, namely Daniel Derkacs, Swee-Hoe Lim, Jeremy Law, Hongtao Zhang, and Sourobh Raychaudhuri. Professor Peter Asbeck, Professor Yu-Hwa Lo, and Professor Yu's unyielding support no doubt greatly improved my candidacy to pursue a doctoral degree at the University of California, Berkeley.

After arriving at Cal, my current advisor, Professor Tsu-Jae King Liu, guided me through the competitive atmosphere of top tier academic research with unwavering patience. I sincerely thank Professor King Liu for seeing a greater potential in what I could accomplish than I at first saw in myself. While I have learned a lot about semiconductor device physics in the classroom and the lab, Professor King brings intangible qualities to my education that I now count as more valuable than the sum of all of my academic work. Her exemplary advising and management truly sets an uncompromising tone for the pursuit of research excellence. I am in her debt and truly appreciative of the opportunity to work in her research group here at Berkeley.

Additionally, I am grateful to Professors Chenming Hu and Sayeef Salahuddin for their help in designing my experiments, interpreting results, and for greatly enriching my experience at Berkeley. I would also like to thank Professors Ming Wu, Junqiao Wu, David Attwood, and Eugene Haller for participating as preliminary and qualifying exam committee members.

While I often strive for a high degree of self-reliance as a Ph.D. candidate, this dissertation would not be possible without the help and advice of so many others. For process calibration, design, and troubleshooting in the Berkeley Microlab and Nanolab, the following individuals extended a helping hand beyond expectations: Sia Parsa, Jimmy G. M. Chang, Kim Chan, Joe Donnelly, Brian McNeil, Bob Hamilton, Jay Morford, and Danny Pestal. To my colleagues for their help with training, experiments, and discussions: Joanna Lai, Donovan Lee, Changhwan Shin, Byron Ho, Zachery Jacobson, Sung-Hwan Kim, Vincent Pott, Louis Hutin, Jaeseok Jeon, Xin Sun, Nattapol Damrongplasit, Nuo Xu, Eung Seok Park, Sapan Argawal, Pratik Patel, Anupama Bowonder, and Kanghoon Jeon. Others for their help in troubleshooting equipment (and my sanity) in the lab: Patrick Bennett, Roger Chen, Amit Lakhani, Jodi Iwata, Jack Yaung, Philip Chen, Adrienne Higa, Stevan Djordjevic, Lee Fok, Jason Valentine, Erick Ulin-Avila, Guy Bartal, Christopher Rhodes, and Nathan Emley.

Lastly, I have to thank a few friends I have made along the way whose guidance was greatly appreciated (whether they would admit to mentoring me or not): Dr. David F. P. Pile, Prof. Rupert Oulton, Dr. David Hammond, Dr. Muralidhar Ambati, Prof. Geoffroy Lerosey, Dr. Ze'ev Abrams, and Christopher Gladden.

# Chapter 1

#### Introduction

#### 1.1 CMOS Solid State Switching Devices

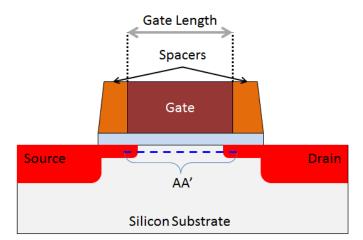

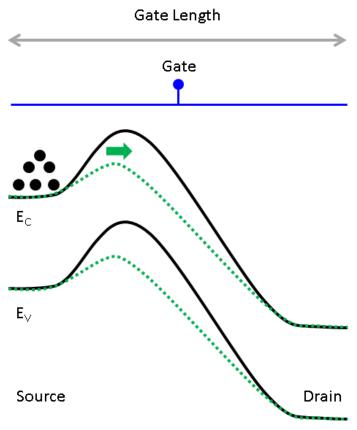

The continued improvement of metal-oxide-semiconductor field effect transistor (MOSFET) performance is due in large part to the scalability of semiconductor manufacturing and demand driven new-product cycles. A simple description of a MOSFET is as follows: with a bias applied between the source and the drain, the gate electrode can dramatically alter the resistance of the channel by capacitively coupling to the semiconductor region immediately below the gate. A schematic cross-section of a MOSFET is presented in Fig. 1.1. The gate capacitively couples to the silicon (Si) substrate and controls a source side energy barrier, modulating the current flowing from the source to the drain (see Fig. 1.2).

Figure 1.1: A schematic cross-section of a typical MOSFET. Historically, scaling down the printed gate length improved  $I_{\rm ON}$ . MOSFET design requires a balance between the separation distance between the source and drain doping profiles and the operating voltage of the device. The cut-line AA' approximately references the location of the channel for the band diagram in Fig. 1.2

Scaling, or reducing key physical dimensions of the transistor structure, has regularly

improved device performance and density for over 40 years. With decreasing critical dimensions and increasing device density, new design challenges are continually addressed to meet the demand in a growing market for electronics. An important concern raised in literature (e.g., reference [1]) is that an increase in the passive power density for current MOSFET technology is unavoidable with continued scaling. Various alternative devices have been proposed to replace or complement MOSFETs and all are designed to maintain or improve performance while reducing the off-state power consumption.

**Figure 1.2:** A band diagram for the MOSFET from the AA' cutline in Fig. 1.1. The off-state (black lines) presents a source side energy barrier to prevent carriers from entering the channel. In the on state (green dotted lines), the barrier is lowered and carriers move from the source to the drain.

#### 1.2 Proposed Alternatives to CMOS-based Logic

A lower limit for the switching efficiency of a MOSFET relates the strength of the capacitive coupling of the gate to the distribution of mobile charge carriers in the source. For MOSFETs, the distribution of carriers in the source is sometimes referred to as a Boltzmann distribution in energy peaking near the conduction (valence) band edge for an n-channel (a

p-channel) device. [2] A metric for the efficiency of gate coupling to the channel is the inverse subthreshold slope, SS:

$$SS = \left(\frac{d(\log_{10} I_{\rm D})}{dV_{\rm GS}}\right)^{-1} = \ln(10) \frac{k_{\rm B}T}{q} \left(1 + \frac{C_{\rm dm}}{C_{\rm ox}}\right). \tag{1.1}$$

In equation 1.1,  $k_{\rm B}$  is Boltzmann's constant, q is the charge of one electron,  $C_{\rm ox}$  is the areal gate oxide capacitance and  $C_{\rm dm}$  is the areal depletion layer capacitance. Equation 1.1 approaches a lower limit of approximately 60 mV/dec at T = 300K when  $C_{\rm dm}/C_{\rm ox}$  is close to zero.

Scaling has historically involved decreasing  $L_{\rm G}$  and increasing  $C_{\rm ox}$  (by decreasing the effective oxide thickness) so as to increase  $I_{\rm ON}$ . Even with the co-optimization of material properties (e.g., peak doping concentration, strain engineering), an aggressively scaled MOS-FET can exhibit short channel effects that reduce the gate control of the channel. New device structures have been proposed to replace MOSFETs when decreasing  $L_{\rm G}$  and increasing  $C_{\rm ox}$  is no longer possible due to material constraints (or economically viable).

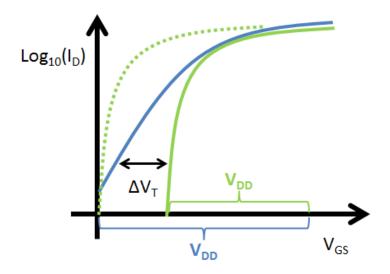

A promising alternative for new current injection mechanisms is any switch that is not limited to a  $\frac{k_{\rm B}T}{q} \ln{(10)}$  minimum. Fig. 1.3 qualitatively shows the benefit of a low SS for an alternative device. A steeply switching device allows for a lower threshold voltage,  $V_{\rm T}$ , (hence a lower power supply voltage,  $V_{\rm DD}$ ) and the possibility of a lower  $I_{\rm OFF}$  which decreases the passive power consumption.

Proposals for alternative devices include scaled down mechanical relays [3], impact ionization FETs [4], feedback FETs [5], FETs with negative gate capacitance [6], and band-to-band tunneling (BTBT) FETs.[7] This dissertation explores the properties of BTBT and trap-assisted tunneling (TAT) in the context of tunneling FETs (TFETs).

$<sup>^{1}</sup>SS$  equally refers to the subthreshold swing.

Figure 1.3: A steeply switching device proves a compelling goal for a MOSFET replacement. The blue curve represents a traditional MOSFET I-V transfer characteristic. The solid green curve comparatively highlights the main benefit of a steeper transfer characteristic: a reduction in the power supply voltage,  $V_{\rm DD}$ . Presumably, a steeper SS characteristic can be threshold-voltage shifted (as depicted in the dashed green curve).

# 1.3 Tunneling Field Effect Transistors: Basic Design and Operation

Models for the tunneling probability and the tunneling current (via BTBT) in semiconductors were succinctly and nearly simultaneously proposed by Leonid V. Keldysh and Evan O. Kane. [8, 9] Equation 1.2 gives the tunneling current density for a direct bandgap material commonly found in literature. [10]

$$J_{\rm T} = \frac{2\sqrt{2m^*}q^2F}{3\pi^3\hbar^2 E_{\rm g}^{1/2}} \exp\left[-\frac{\pi\sqrt{m^*}E_{\rm g}^{3/2}}{2\sqrt{2}\hbar qF}\right]$$

(1.2)

$m^*$  is the carrier effective mass, F is the electric field,  $E_{\rm g}$  is the semiconductor bandgap, and  $\hbar$  is Planck's constant. Consolidating the electric field pre-factors of equation 1.2 gives the more common expression for Kane's equation,

$$J_{\rm T} = AF \cdot e^{-B/F},\tag{1.3}$$

where A and B represent material properties for the semiconductor of interest. For a TFET, equation 1.3 implies that the BTBT generation rate of carriers into the channel is exponentially sensitive to the electric field at the tunneling junction. Whereas for a MOSFET, the population of carriers in the channel is exponentially sensitive to the surface potential (or the channel potential).

Immediately apparent in equations 1.2 and 1.3 is that a larger electric field at the tunneling junction produces a larger BTBT current (i.e., a larger  $I_{\rm ON}$ ). Incorporating a larger built-in electric field into the design of a TFET should then increase  $I_{\rm ON}$  (and thus performance) for a given power supply voltage. A conventional TFET design typically utilizes a very steep doping profile in the source in order to realize a large built-in electric field near the BTBT junction. Despite advancements in low energy ion implantation, flash annealing, and in situ doping during epitaxial growth, fabricating very steep doping profiles remains a challenge.

In 1994, Reddick and Amaratunga proposed and fabricated the first known Si based BTBT transistor.[11] Motivated by the potential for increased functionality due to negative differential resistance observed in other tunneling devices, a gated reverse biased diode was fabricated on bulk Si. This proposed structure called for modulating the tunneling current by modulating the tunneling barrier width, determined in part by the band gap  $(E_g)$ , the applied bias, and the depletion width.[11] Reddick and Amaratunga also acknowledged the potential advantage of a necessarily narrow tunneling barrier for the purpose of scaling beyond complementary MOS (CMOS) transistor technology limits.

Since 1994, numerous experimental avenues seeking sub-60 mV/dec SS at room temperature have been explored. Most approaches have focused (and continue to focus) on the importance of a large built-in electric field obtained either by in situ epitaxial growth, heterostructure formation, 1D quantum confinement, or hyperabrupt depleted pocket doping.[7, 12–15]

#### 1.4 Thesis Organization

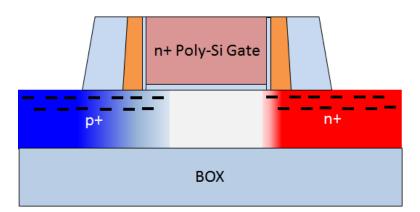

This dissertation details three experiments investigating the role of traps within or near a tunneling junction and follows with a new design approach for a simplified source doping profile design without an ambitiously steep gradient. In chapter 2, a SB-MOSFET structure is modified to take advantage of a steep doping profile obtained via dopant segregation from silicide. Sub- $\frac{k_{\rm B}T}{q} \ln{(10)}$  SS is observed and interpreted as a trap based tunneling process followed by thermionic emission of carriers near the source.

In chapter 3, erbium (Er) impurity atoms are purposely introduced into Si near a heterojunction formed with p+ poly-crystalline germanium (Ge). The presence of traps in p-i-n heterodiodes is verified with temperature dependent measurements and a trap-assisted tunneling simulations using a commercially available TCAD semiconductor device simulation software package. A very low activation energy,  $E_{\rm A}$ , is observed for a p+/n+ heterodiode with Er electronic trap states present within the bandgap of Si and TCAD simulations highlight the limitations of tunneling models for tunneling into and out of trap states.

Er based trap-assisted TFETs (Er-TATFETs) were fabricated on silicon-on-insulator (SOI) substrates and subsequently characterized. Results from temperature-dependent measurements are presented in chapter 4. Low temperatures (T  $\leq \sim 200$ K) were necessary in order to mitigate thermal generation current due to trap states. The  $E_{\rm A}$  in the subthreshold

regime for Er-TATFETs was found to be slightly lower in comparison to the  $E_{\rm A}$  for p-i-n control TFETs.

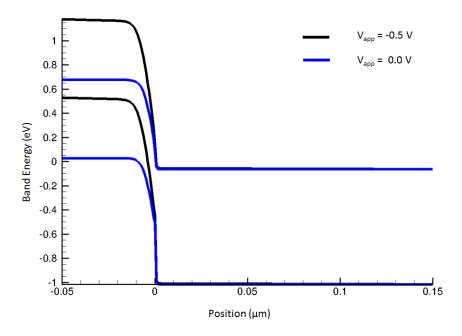

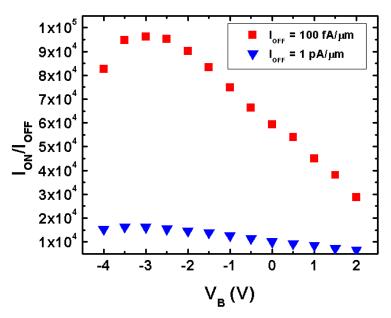

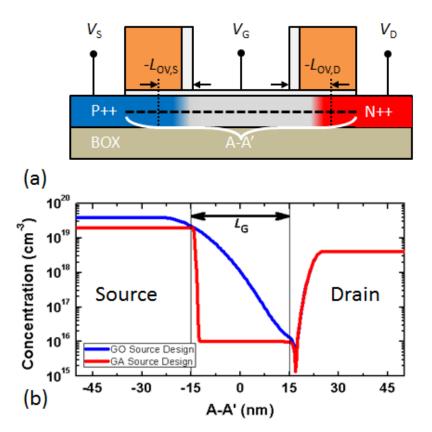

Chapter 5 extends an SOI TFET simulation study to explore the role of reverse back bias for n-channel germanium-on-insulator (GeOI) based TFETs. A gate-overlapped source is found to provide superior  $I_{\rm ON}/I_{\rm OFF}$  enhancement with  $V_{\rm B} < 0V$  in comparison to a steeply graded gate-aligned source. Applying a reverse back bias with a gate-overlapped source can trigger a large area tunneling junction at turn-on and also mitigate some SCEs.

Finally, chapter 6 summarizes this dissertation and highlights some of challenges facing TFET devices.

# Bibliography

- [1] W. Haensch, E. J. Nowak, R. H. Dennard, P. M. Solomon, A. Bryant, O. H. Dokumaci, A. Kumar, X. Wang, J. B. Johnson, and M. V. Fischetti, "Silicon CMOS devices beyond scaling," *IBM Journal of Research and Development*, vol. 50, no. 4.5, pp. 339 –361, Jul. 2006, ISSN: 0018-8646. DOI: 10.1147/rd.504.0339.

- [2] Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices. Cambridge, UK: Cambridge University Press, 1998.

- [3] V. Pott, H. Kam, R. Nathanael, J. Jeon, E. Alon, and T.-J. K. Liu, "Mechanical computing redux: relays for integrated circuit applications," *Proceedings of the IEEE*, vol. 98, no. 12, pp. 2076 –2094, Dec. 2010, ISSN: 0018-9219. DOI: 10.1109/JPROC. 2010.2063411.

- [4] W. Y. Choi, J. Y. Song, J. D. Lee, Y. J. Park, and B.-G. Park, "70-nm impact-ionization metal-oxide-semiconductor (I-MOS) devices integrated with tunneling field-effect transistors (TFETs)," in *Electron Devices Meeting*, 2005. IEDM Technical Digest. IEEE International, Dec. 2005, pp. 955–958. DOI: 10.1109/IEDM.2005.1609519.

- [5] A. Padilla, C. W. Yeung, C. Shin, C. Hu, and T.-J. K. Liu, "Feedback fet: a novel transistor exhibiting steep switching behavior at low bias voltages," in *Electron Devices Meeting*, 2008. IEDM 2008. IEEE International, Dec. 2008, pp. 1–4. DOI: 10.1109/IEDM.2008.4796643.

- [6] A. I. Khan, D. Bhowmik, P. Yu, S. J. Kim, X. Pan, R. Ramesh, and S. Salahuddin, "Experimental evidence of ferroelectric negative capacitance in nanoscale heterostructures," *Applied Physics Letters*, vol. 99, no. 11, 113501, p. 113501, 2011. DOI: 10.1063/1.3634072. [Online]. Available: http://link.aip.org/link/?APL/99/113501/1.

- [7] A. Seabaugh and Q. Zhang, "Low-voltage tunnel transistors for beyond CMOS logic," *Proceedings of the IEEE*, vol. 98, no. 12, pp. 2095 –2110, Dec. 2010, ISSN: 0018-9219. DOI: 10.1109/JPROC.2010.2070470.

- [8] L. V. Keldysh, "Behaviour of Non-Metallic Crystals in Strong Electric Fields.," Soviet Physics: J. Exptl. Theoret. Phys., vol. 33, pp. 994–1003, 1957.

- [9] E. O. Kane, "Theory of tunneling," Journal of Applied Physics, vol. 32, no. 1, pp. 83–91, 1961. DOI: 10.1063/1.1735965. [Online]. Available: http://link.aip.org/link/?JAP/32/83/1.

BIBLIOGRAPHY 8

- [10] S. M. Sze, *Physics of Semiconductor Devices*, 2nd ed. Wiley, 1981.

- [11] W. M. Reddick and G. A. J. Amaratunga, "Silicon surface tunnel transistor," *Applied Physics Letters*, vol. 67, no. 4, pp. 494–496, 1995. DOI: 10.1063/1.114547. [Online]. Available: http://link.aip.org/link/?APL/67/494/1.

- [12] K. Bhuwalka, S. Sedlmaier, A. Ludsteck, C. Tolksdorf, J. Schulze, and I. Eisele, "Vertical tunnel field-effect transistor," *Electron Devices, IEEE Transactions on*, vol. 51, no. 2, pp. 279–282, Feb. 2004, ISSN: 0018-9383. DOI: 10.1109/TED.2003.821575.

- [13] S. H. Kim, H. Kam, C. Hu, and T.-J. K. Liu, "Germanium-source tunnel field effect transistors with record high  $I_{\rm ON}/I_{\rm OFF}$ ," in *VLSI Technology*, 2009 Symposium on, Jun. 2009, pp. 178–179.

- [14] J. Appenzeller, Y.-M. Lin, J. Knoch, and P. Avouris, "Band-to-band tunneling in carbon nanotube field-effect transistors," *Phys. Rev. Lett.*, vol. 93, p. 196805, 19 Nov. 2004. DOI: 10.1103/PhysRevLett.93.196805. [Online]. Available: http://link.aps.org/doi/10.1103/PhysRevLett.93.196805.

- [15] P. Patel, K. Jeon, A. Bowonder, and C. Hu, "A low voltage steep turn-off tunnel transistor design," in *Simulation of Semiconductor Processes and Devices*, 2009. SISPAD '09. International Conference on, Sep. 2009, pp. 1–4. DOI: 10.1109/SISPAD.2009. 5290257.

# Chapter 2

# Enhanced Schottky Barrier MOSFET with Steep Subthreshold Swing at Low Current

#### 2.1 Introduction

When a metal is placed in intimate contact with a semiconductor surface, an intrinsic potential barrier forms at the interface between the metal and the semiconductor and is referred to as a Schottky barrier (SB).[1] A non-zero barrier acts to disrupt (though not prohibit) the free flow of charge carriers across the interface and a depletion region forms in equilibrium to maintain charge neutrality.<sup>1</sup> The value of this SB and how it can be modified is important when designing low resistance contacts to semiconductor devices such as diodes, transistors, and resistors.

Metal-semiconductor alloys are routinely formed to reduce the contact resistance of semi-conductor devices. For a silicon based device, the alloy is a silicide and serves as the metal in a metal-semiconductor junction. Silicides are the result of an elevated temperature alloying process referred to as silicidation. For a MOSFET, proper design of the transistor allows for self-aligned silicidation to take place. For example, platinum is deposited as a blanket film on top of a MOSFET structure; under thermal treatment, platinum-silicide (PtSi) forms where Si is exposed to the Pt film. If Pt does not react with the underlying material, the silicidation process is selective and forms only where Si is exposed.

A Schottky barrier MOSFET (SB-MOSFET) is similar to a conventional MOSFET but utilizes a SB interface at the source and drain junctions instead of an impurity doped semi-conductor. A generic SB-MOSFET is schematically shown in Fig. 2.1. The main difference between the two device structures is that the source-side potential barrier of a MOSFET is replaced by a SB with an associated Schottky barrier height (SBH). Replacing the source and drain doping profiles with a silicide holds some promise towards addressing challenges

<sup>&</sup>lt;sup>1</sup>For real material systems.

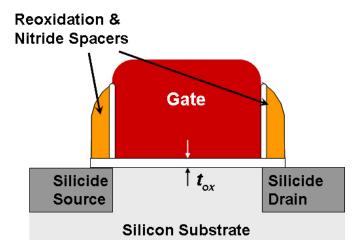

Figure 2.1: A SB-MOSFET device structure. The metal (or silicide) source and drain are well aligned with the gate edge.

associated with scaling the source and drain profiles in a conventional MOSFET. Reference [2] provides a good introduction to SB interfaces, some underlying physics and assumptions, as well as a topical review of the present state of SB-MOSFETs.

Ideally, a well-designed SB-MOSFET provides a solution to various scaling problems including:[2, 3]

- Low parasitic resistance or access resistance.

- Reduced variability due to source and drain extension profiles near the channel.

- Improved mitigation of short channel effects (SCE).

- Reduced off-state leakage due to the intrinsic SBH.

- Elimination of parasitic bipolar action.

In Fig. 2.1, the source and drain SB junctions are closely aligned to the gate edge with no gate-to-metal overlap. Aligning the SB interface near the gate edge is important so that capacitive control of the channel is not compromised.

A key design goal for a SB-MOSFET is a low SBH for carriers injected into the channel. A low SBH increases the on-current  $(I_{\rm ON})$  (in strong inversion) and presumably the transistor performance. The intrinsic SBH is determined by the silicide-silicon work function difference. A SBH can be modified, however, by doping the silicon near the SB.[4] Figure 2.2 shows a band diagram alignment for a SB interface with and without dopants modifying the SBH.

Optimal SB-MOSFET design necessitates the careful choice of metal for the silicide formation. An additional requirement is that the silicide formation must also be manageable from a fabrication perspective. The silicidation process involves the co-diffusion of Si into

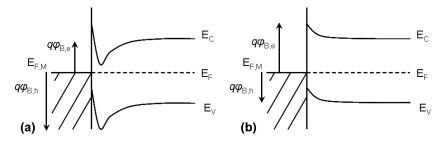

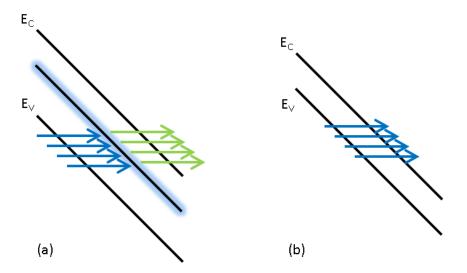

Figure 2.2: Band diagram of a metal-semiconductor interface with (a) and without (b) dopants. Dopants near the interface are used to engineer, or adjust, the SBH.  $\phi_{\rm B}$  is the SB potential.

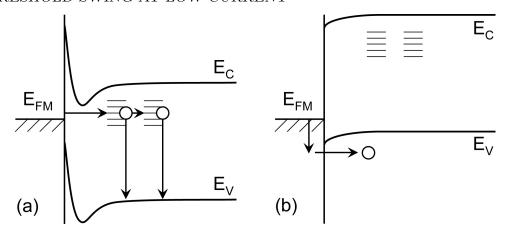

**Figure 2.3:** Qualitative band diagrams of a SB-MOSFET in the (a) off-state and (b) the on-state. Various leakage (a) and current injection routes (b) are highlighted in the schematic.

the metal and vice-versa. This alloying reaction produces a reactive interface, or reaction front, which moves away from the original metal-silicon interface. [5] The choice of the metal, optional interface materials, silicidation temperature, and geometry of the silicon device all factor into the final position of the silicide-silicon interface. Consequently, SB junctions well aligned to the gate edge present a processing and device physics challenge.

Fig. 2.3 shows band diagrams in the off-state and on-state of a SB-MOSFET. When the potential drop across the source-side SB junction is large enough, the depletion width in the semiconductor narrows such that field emission tunneling current,  $I_{\rm FE}$ , through the thin triangular barrier is appreciable and becomes the dominant current injection mechanism. In this way,  $I_{\rm ON}$  is limited by the SBH at the source. When the SBH is too large, a smaller fraction of the available states in the metal source contributes to current injection. In general, SB-MOSFET non-idealities include low  $I_{\rm ON}$ , subsurface SB junction leakage away from the active channel of the device, and parasitic metal-semiconductor diode behavior apparent in the output characteristics ( $I_{\rm D}(V_{\rm GS},V_{\rm DS})$  vs.  $V_{\rm DS}$ ).[2]

SB-MOSFET fabrication techniques provide an additional avenue towards fabricating an alternative solid-state switching device. Modifying the SBH using dopant segregation of impurities implanted into silicide (ITS), relatively steep doping profiles can be realized with a low thermal budget.[4] As discussed in chapter 1, a steep doping profile yields a large built-in potential and thus a large built-in electric field near the proposed tunneling junction. Since the band-to-band tunneling (BTBT) probability increases nearly exponentially with the electric field, a large built-in potential near the tunneling junction is desirable.

#### 2.2 Silicide/Silicon Interface

An inherent shortcoming of any thermal process in forming a silicide is the stochastic nature of small imperfections in the initial conditions during semiconductor processing. Most theoretical and empirical models typically assume an atomically abrupt interface regarding metal-semiconductor junctions. [2, 6] However, the formation of a silicide by thermal processing necessarily involves co-diffusion of metal atoms into Si and Si atoms into the metal. [5] Fick's law of diffusion can be applied to a silicide growth system assuming steady state conditions <sup>2</sup> during certain phases of the growth. [7, 8] For diffusion limited silicide formation, the final atomic profile of a metal impurity in silicon represents an exponential decay extending from the silicide/silicon interface. [9] The metal impurity peak concentration is strongly correlated with the final silicide stoichiometry and nearly equals the atomic density of crystalline silicon. The characteristic decay length is governed by the time and temperature of the silicidation process.

Another consideration is the orientation of silicide grains as the silicide forms. While on aggregate the reaction interface can be smooth (as schematically depicted in [5]), silicides commonly considered for SB-MOSFET applications are known to be poly-crystalline. As such, each grain in the poly-crystalline silicide forms in an energetically favorable orientation for that particular localized reaction front. Consequently, silicide/silicon interfaces appear rough on a scale close to or less than the average grain size. This is unfortunate in the context of scaled SB-MOSFETs in that the silicide/silicon interface is not atomically abrupt and inherently leads to variability.[10] The stochastic nature of the resulting interface increases device sensitivity to key device parameters such as subthreshold swing (SS) and threshold voltage,  $V_{\rm T}$ . Reducing variability is important in almost any type of device scaling, especially for alternative devices such as TFETs where the SS is very sensitive to local electric field fluctuations at the tunneling junction.

As a result, a silicide/silicon interface for the purpose of a steeply switching transistor must, in addition to previous requirements on processing and device design, be uniform across the width of the device if the interface is close to the tunneling junction. One contributing factor to a rough interface is the rapid thermal anneal (RTA) process often used to form a silicide. While an RTA process can reduce the thermal budget, poly-crystalline grain size can be sensitive to RTA process parameters. By trading a short RTA process time for a longer temperature ramping time, localized temperature fluctuations at the silicide reaction front can be mitigated.

<sup>&</sup>lt;sup>2</sup>Such as constant flux or diffusion limited growth.

Finally, using a Kissinger analysis to model the silicide thickness with the classical growth rate equation (equation 2.1) yields a predictive RTA process parameter set which can be incorporated into a modified SB-MOSFET design. The growth rate equation predicts the silicide thickness, Z, for a known activation energy,  $E_A$ , temperature dependent diffusivity,  $D = D_0 \exp\left(\frac{-E_A}{k_B T}\right)$ , pre-exponential diffusion coefficient,  $D_0$ , a given temperature range from  $T_0$  to T, and a known temperature ramp rate, dt/dT: [5, 8, 11]

$$Z^{2} = \int_{0}^{t} Ddt = \int_{T_{0}}^{T} D\left(\frac{dT}{dt}\right)^{-1} dT$$

$$= D_{0} \left(\frac{dT}{dt}\right)^{-1} \frac{k_{B}}{E_{A}} \left\{ T^{2} \exp\left(-\frac{E_{A}}{k_{B}T}\right) - T_{0}^{2} \exp\left(-\frac{E_{A}}{k_{B}T_{0}}\right) \right\}. \quad (2.1)$$

When the temperature remains constant, the thickness is simply estimated by integrating 2.1 (without a variable substitution) to obtain

$$Z^2 = D(T) \cdot t. \tag{2.2}$$

Predictive modeling of the silicide thickness allows for a lower temperature ramp rate with the end goal of a uniform silicide/silicon interface.

Additionally, when engineering the SBH with doping near the interface, the ITS method piles up dopants near the interface, similar to dopant segregation induced by silicidation. However, the ITS method results in a steeper doping profile.[12]

Thus, key requirements for an adequate silicide/silicon interface include:

- Known diffusion coefficients and activation energies for the metal-silicon material system.

- A steep, electronically active impurity doping profile near the gate edge.

- A desirable work function yielding a low SBH for the injected charge carriers.

- A uniform, or smooth, silicide/silicon interface parallel to the gate edge.

#### 2.3 Modified Designs for Band-to-Band Tunneling

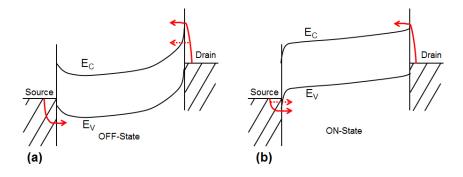

PtSi was chosen as the lead candidate material for the source and drain for a modified SB-MOSFET design. PtSi formation is relatively well understood with a low intrinsic SBH for holes for p-channel FET operation and satisfies many of the aforementioned requirements.[4, 5, 8, 12] To redesign a SB-MOSFET for BTBT current, an asymmetric p-i-n doping profile is incorporated across the channel region. An additional method to enhance the built-in electric field near the tunneling junction involves creating a small depletion region, or pocket

**Figure 2.4:** Schematic cross-section of a p-i-n TFET with SB junctions very near the source and drain. In (a), a pocket doping profile via ITS is introduced prior source ion implantation. In (b), a p-i-n doping profile via ITS is proposed as a control structure to examine the effect of the pocket formation via ITS. The ITS method is proposed to form the steep doping profiles necessary for a lower threshold for BTBT.

of opposite doping, near the source tunneling junction.[13] Fig. 2.4 shows a schematic cross-section of a SB based TFET with and without a doped pocket profile.

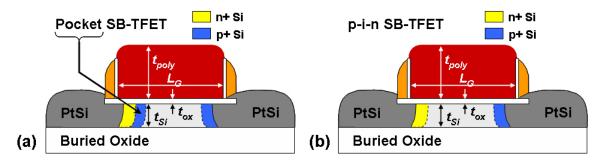

Figure 2.5 highlights key fabrication steps for the devices and shows a plan-view scanning electron micrograph of the fabricated device. The fabrication process for the SB-MOSFET is described in more detail in section 2.3. The PtSi formation was accomplished with the following RTA process parameters:

- 1. 20°C/min temperature ramp rate.

- 2. 300°C for 5 min.

- 3. 25°C/min temperature ramp rate.

- 4. 400°C for 5 min.

- 5. 25°C/min temperature ramp rate.

- 6.  $425^{\circ}$ C for 3 min. with  $O_2$  flowing at 25 sccm.

- 7. Cool down to room temperature.

Out-diffusion of Si to the surface of the PtSi occurs during the final thermal steps. Flowing oxygen during the final step is necessary to form a protective  $SiO_x$  layer on top of the PtSi. This protective  $SiO_x$  layer prevents removal of the PtSi during a necessary soak in heated, dilute aqua regia to remove the remaining Pt that did not react with Si.[14]

#### Fabrication of p-Channel SB S/D FETs

A lightly p-type doped  $(1 \cdot 10^{15} \text{ cm}^{-3})$  silicon-on-insulator (SOI) wafer was used as the starting substrate. Conventional planar processing steps were used to fabricate SB-FETs with a body

**Figure 2.5:** The sequence of key device fabrication process steps is shown on the left, and a plan-view scanning electron micrograph of a fabricated device is shown on the right with the source, gate, and drain labeled.

thickness  $t_{\rm Si}=25$  nm and a thermal gate-oxide thickness  $t_{\rm ox}=2.8$  nm. Note that the self-aligned PtSi formation step is performed prior to the introduction of any source or drain dopants. This silicide was formed by sputter deposition of a 17 nm-thick Pt layer followed by thermal annealing according to the steps listed in the previous section and similar to the process in [14]. Following silicidation, the n-type source and p-type drain regions were sequentially formed by ITS processes as follows. First,a drain-masked As<sup>+</sup> implantation process  $(1 \cdot 10^{15} \ {\rm cm}^{-2} \ {\rm at} \ 10 \ {\rm keV})$  followed by a dopant segregation anneal in N<sub>2</sub> at 450 °C for 15 min was used to form the n-type source region. Second, a source-masked BF<sub>2</sub><sup>+</sup> implantation process  $(1 \cdot 10^{15} \ {\rm cm}^{-2} \ {\rm at} \ 10 \ {\rm keV})$  followed by a dopant segregation anneal in N<sub>2</sub> at 500 °C for 5 min was used to form the p-type drain region. The peak doping concentration in the Si is primarily a function of the segregation anneal temperature [15] and Secondary Ion Mass Spectrometry (SIMS) analysis of test samples in [15] indicates that the peak As concentration at the PtSi-Si interface is between  $10^{19} \ {\rm cm}^{-3}$  and  $10^{20} \ {\rm cm}^{-3}$ .

Preliminary n-channel SB-MOSFETs were fabricated similar to reference [15] to verify the silicidation and ITS processing parameters. Experimental splits included pocket SB-TFETs with control p-i-n SB-TFETs along with temperature and time variations in the final RTA dopant segregation anneals.

#### 2.4 Device Characterization and Discussion

Device characterization was performed using an HP4155C semiconductor parameter analyzer and a wafer-probe station with a temperature-controlled chuck. Long integration time was used so that the noise floor is approximately 10 fA.<sup>3</sup> While fabricated n-channel SB-MOSFETs showed decent transfer characteristics to verify the process flow design (similar to [15]), SB-MOSFETs modified as pocket TFETs did not yield promising results. A working hypothesis is as follows:

<sup>&</sup>lt;sup>3</sup>Each data point represents an average of values measured over a period of 266 ms.

- Silicide formation inherently involves a Si supply from the SOI substrate and, thus, the active area of the device.

- When Si diffuses and reacts with Pt, vacancy sites are left behind in near the silicide/silicon interface.

- The RTA process following ITS uses a low temperature anneal and yields electronically active dopants near the interface.

- If dopant atoms are electronically active, then the dopant atoms occupy lattice sites.

- The formation of a pocket doping profile via a second ITS procedure with a subsequent dopant segregation necessarily involves the second impurity species displacing the first impurity species from lattice sites between the PtSi-Si interface and the pocket profile

- If the second impurity species does not displace an appreciable fraction of the first impurity species in a controlled manner, then the second species merely compensates the first species resulting in a poorly performing asymmetric SB-MOSFET.

Fig. 2.6 highlights typical transfer characteristics exhibited by pocket SB-TFETs cofabricated with p-i-n modified SB-MOSFETs. The pocket transistors display ambipolar behavior. Similar to SB-MOSFET operation, carriers are likely injected over a thermal barrier due to a poorly defined pocket dopant profile.

**Figure 2.6:** Transfer characteristic of a modified SB-MOSFET with a pocket doping profile near the source. Low  $I_{\text{ON}}/I_{\text{OFF}}$  and poor SS are representative of a typical pocket TFETs fabricated in this manner.

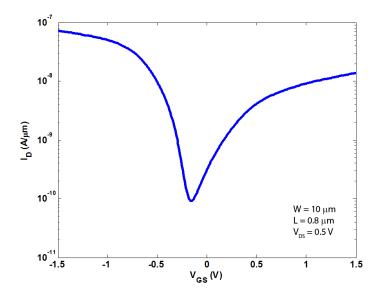

Figure 2.7: Initial measurements of the transfer characteristics of a p-channel enhanced SB-MOSFET (with channel length  $L_{\rm G}=5~\mu{\rm m}$  and channel width W = 0.7  $\mu{\rm m}$ ) at two temperatures. The gate voltage step is 10 mV and  $V_{\rm DS}=$  -0.5 V. Solid symbols are used for the source current at every third gate voltage step.

Fig. 2.7 shows the initially measured transfer characteristics ( $|I_{\rm D}|$  vs.  $V_{\rm GS}$ ) for an interesting p-channel p-i-n SB-FET at two temperatures, 300 K and 323 K. A large negative gate voltage is required to invert the surface of the source region due to the n+ poly gate material and heavy source doping.<sup>4</sup> Note that a change in polarity for  $I_{\rm D}$  is evident near  $V_{\rm GS}=-0.6$  V. This polarity change is likely due to reverse-bias diode leakage, which could account for the observed small opposite-polarity component (approximately 50 fA/ $\mu$ m) of drain current for  $V_{\rm GS}>-0.6$  V.

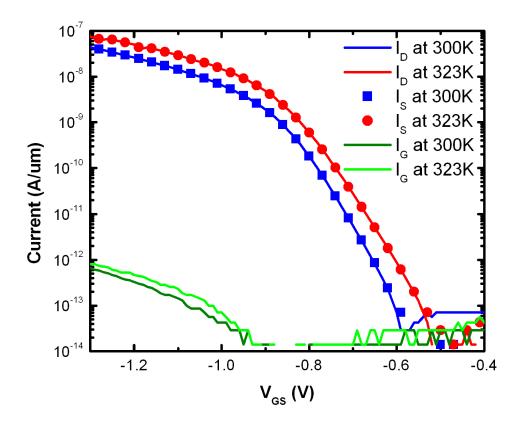

Subsequent, more detailed measurements of the transfer characteristics are shown in Fig. 2.8. The increased gate current is most likely due to cumulative stress over many measurements made using a long integration time. Despite this increase in the direct gate

$<sup>^4|</sup>V_{\rm T}|$  can be lowered to be close to 0 V by using a gate material with a larger work function (e.g. p+poly-Si) and also by lowering the active source doping concentration (by adjusting the dopant segregation anneal conditions.

Figure 2.8: Measured transfer characteristics of a p-channel enhanced SB-MOSFET (with channel length  $L_{\rm G}=5~\mu{\rm m}$  and channel width W = 0.7  $\mu{\rm m}$ ) at 300K for various values of  $V_{\rm DS}$ . The gate voltage step is 10 mV. The light-gray dashed line indicating 60 mV/dec sub-threshold swing is shown for reference. The solid magenta line is the measured gate current for  $V_{\rm DS}=$  -0.5 V.

current,  $I_{\rm D}$  is unchanged and continues to show steep switching behavior. Also of note, the opposite-polarity component of  $I_{\rm D}$  is independent of both  $V_{\rm GS}$  and  $V_{DS}$  (Figs. 2.7 and 2.8). The hollow square symbols in Fig. 2.8 correspond to a two-dimensional (2-D) device simulation of a SB-MOSFET,[16] discussed in more detail below. For a low operating voltage, this device exhibits a relatively high on/off current ratio:  $I_{\rm ON}/I_{\rm OFF}=1.17\cdot10^3$  for 0.2 V gate-voltage swing (from -0.63 V to -0.83 V) at  $V_{\rm DS}=$  -0.2 V. Although this device exhibits relatively low drive current (even at high voltages), an appreciable  $I_{\rm ON}/I_{\rm OFF}$  is observed.

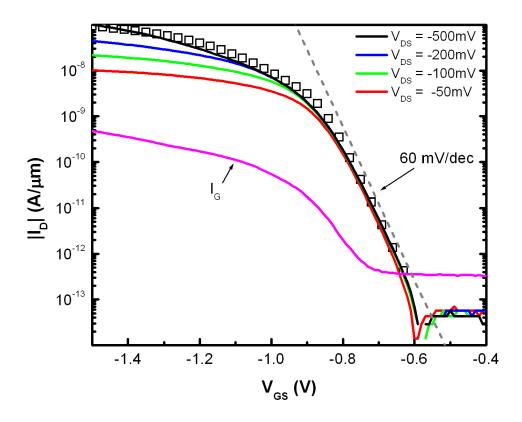

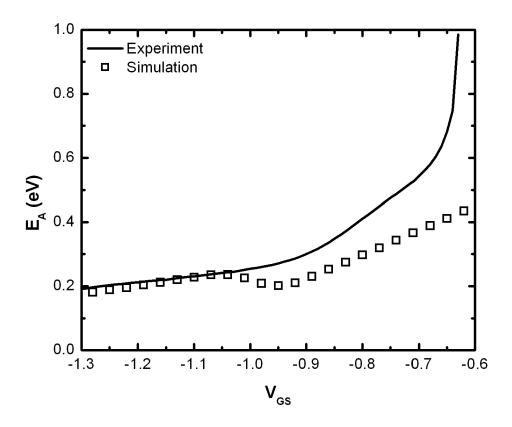

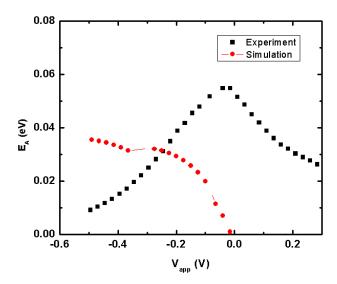

To elucidate the limiting mechanism of carrier transport in this device,  $E_{\rm A}$  was extracted from the more detailed  $|I_{\rm D}|$ -vs.- $V_{\rm GS}$  measurements made in the temperature range from 10 °C to 50 °C ( $V_{\rm DS}=$  -0.5 V).  $E_{\rm A}$  is only calculated for  $|I_{\rm D}|>|I_{\rm G}|$ , corresponding to  $V_{\rm GS}<$ -0.63 V, in order to avoid any artifacts due to the aforementioned small opposite-polarity

Figure 2.9: The inset shows the activation energy  $(E_{\rm A})$  extracted from measurements of log  $|I_{\rm D}|$  vs. 1/T, for T in the range from 10 °C to 50 °C. The open squares (shown for every third gate-voltage step) correspond to 2-D device simulation for  $V_{\rm DS} = -0.5$  V.

component of drain current. The dependence of  $E_{\rm A}$  on  $V_{\rm GS}$  (Fig. 2.9) indicates that the current-limiting mechanism changes with gate bias: at low biases ( $|V_{\rm GS}| < 0.7$  V)  $E_{\rm A}$  is very large (which suggests that the current is limited by thermionic emission of holes either over a large barrier or from deep traps) and changes more rapidly than  $qV_{\rm GS}$ . At moderate biases (0.7 V <  $|V_{\rm GS}| < 0.9$  V),  $E_{\rm A}$  decreases directly with increasing  $|V_{\rm GS}|$ , as expected for a SB-MOSFET when the thermal barrier is greater than the SBH. At high biases ( $|V_{\rm GS}| > 0.9$  V),  $E_{\rm A}$  becomes a weaker function of  $|V_{\rm GS}|$  as the current becomes limited by SB tunneling.

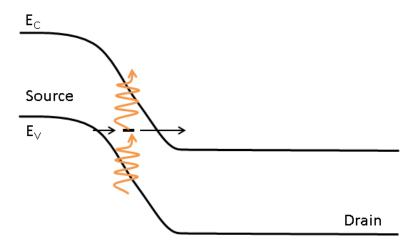

The rapid change in  $E_{\rm A}$  near turn-on is most likely due to thermionic emission of holes from deep acceptor-like trap states into the valence band (see Fig. 2.10). These trap states are associated with metallic impurities and/or crystalline defects located close to the PtSi/Si interface, and holes can be supplied to them via tunneling from the PtSi, a process that turns on abruptly with increasing  $|V_{\rm GS}|$ . As the gate overdrive increases to bring the Si into strong inversion, injection of holes into the channel from trap states is eventually superseded by

Figure 2.10: Schematic energy band diagrams illustrating two carrier injection mechanisms in an enhanced p-channel SB MOSFET. (a) Before the Si is inverted, holes tunnel to and can hop between electronic trap states which are distributed both in energy and space near the metal source. They then move to the Si valence band via thermionic emission. (b) When the Si is inverted, carrier injection is dominated by traditional thermionic emission over the Schottky barrier from the metal source.

thermionic emission of holes over the source side Schottky barrier.

The transfer characteristic in Fig. 2.8 was simulated using Synopsys Sentaurus Device TCAD software [16]. The design parameters for the simulated structure are the same as for the fabricated device:  $L_{\rm G}=5~\mu{\rm m},~{\rm W}=0.7~\mu{\rm m},~t_{\rm Si}=25~{\rm nm},~t_{\rm ox}=2.8~{\rm nm},~{\rm n}$ -type source doping  $N_{\rm D}=10^{19}~{\rm cm}^{-3},$  and p-type drain doping  $N_{\rm A}=10^{19}~{\rm cm}^{-3}.$  By employing a SB at the source and drain electrodes with an effective SBH of 0.33 eV and a reduced minority carrier lifetime (300 ns) to reflect the presence of traps, good agreement between simulated and measured characteristics (for  $V_{\rm DS}=-0.5~{\rm V}$ ) is achieved for the gate voltage range beyond the steep switching regime. The difference between the simulated and experimental  $E_{\rm A}$  (see Fig. 2.9) highlights the fact that the device simulator does not account for the effect of tunneling into trap states with a metal boundary condition. As an additional note, no BTBT model was invoked in the device simulator; thus the simulated device characteristic does not show sub-60mV/dec switching behavior.

The relatively slow temperature ramp rate described in the previous section (20 °C/min, see 2.3) and extended anneal time used for the silicidation process in this work likely resulted in a very extended spatial distribution of Pt atoms within the silicon, as has been observed for Ni silicidation [9, 17]. Pt impurities in n-type Si have been reported to behave as deep-level acceptor-like traps [18], supporting the explanation of the large activation energy at turn-on.

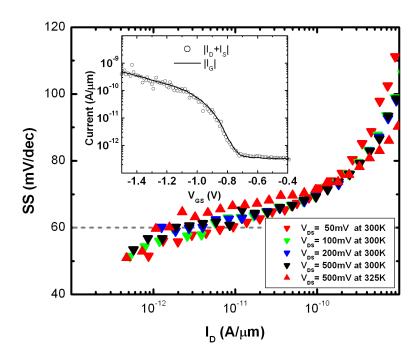

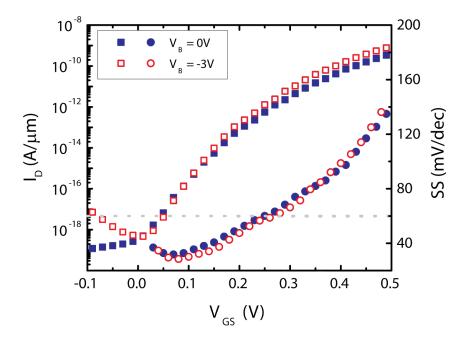

Consistent with the  $E_{\rm A}$  measurements,  $SS < 60~{\rm mV/dec}$  is seen at low current levels (below 10 pA/ $\mu$ m) corresponding to  $|V_{\rm GS}| < 0.7~{\rm V}$ , for multiple values of  $V_{\rm DS}$  as well as at elevated temperature (Fig. 2.11). SS values are shown only for  $|I_{\rm D}| > |I_{\rm G}|$ , again to avoid any artifacts due to the aforementioned small opposite polarity component of drain current.

Figure 2.11: Sub-threshold swing (SS) vs. drain current, derived from the measurements in Fig. 2.8. The sub-60 mV/dec behavior seen below 5 pA/ $\mu$ m is only weakly dependent upon  $V_{\rm DS}$  and temperature. The inset shows that no charging is occurring (to possibly account for the sub-60 mV/dec behavior) for  $V_{\rm DS} = -0.5$  V since  $|I_{\rm D} + I_{\rm S}|$  matches  $|I_{\rm G}|$  very well.

The inset of Fig. 2.11 shows that even after many measurements  $I_{\rm G}$  remains relatively low and that all current is accounted for in the measurement (i.e., no charge build-up occurs to possibly account for the sub-60 mV/dec behavior). Also,  $I_{\rm G}$  cannot possibly cause the observed sub-60 mV/dec SS since  $I_{\rm G}$  changes gradually in the range  $|V_{\rm GS}| < 0.7$  V. At higher current levels, SS increases with  $I_{\rm D}$  as expected for a SB-MOSFET.

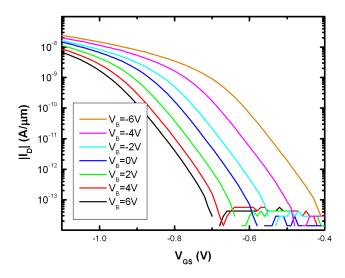

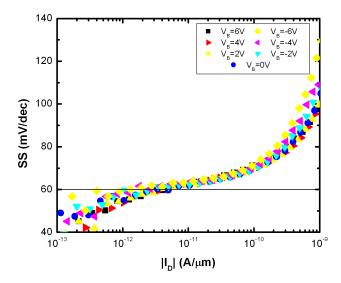

The transfer characteristics in Fig. 2.12 show that with back bias  $(V_{\rm B})$  the threshold voltage (for Si inversion) is reduced with forward back biasing  $(V_{\rm B} < 0)$ , and increased with reverse back biasing  $(V_{\rm B} > 0)$ .<sup>5</sup> The dependence on  $V_{\rm B}$  with increasing reverse back biasing decreases as the backside of the n-type source region becomes accumulated. Note that SS below 60 mV/dec is maintained with back biasing. The results in Fig. 2.13 further suggest that the hole tunneling process occurs in series with thermionic emission into the valence band (as illustrated in Fig. 2.10(a)), since  $V_{\rm B}$  does not affect the range of  $I_{\rm D}$  over which steep switching is observed.

<sup>&</sup>lt;sup>5</sup>Similar to a SOI-MOSFET.

Figure 2.12: Transfer characteristics for various back biases.

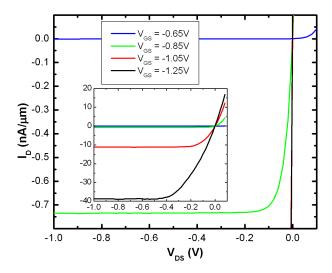

Fig. 2.14 shows the measured output characteristics ( $I_D$  vs.  $V_{DS}$ ) for the same device. Linear behavior is seen at low  $V_{DS}$ , which is consistent with a p+ doped drain [19, 20]. (The current is limited by carrier drift across the channel region (rather than by SB tunneling) at low drain biases [19].)

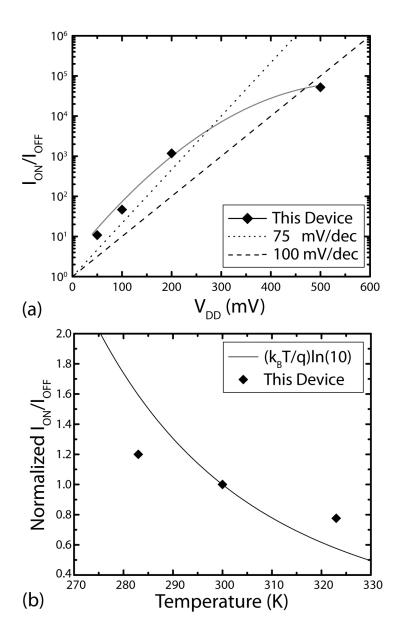

The on/off current ratios in Fig. 2.15 are derived from the transfer characteristics presented in Fig. 3, for each value of  $V_{\rm DD}$ . The two reference lines in Fig. 2.15(a) represent  $SS=75~{\rm mV/dec}$  and 100 mV/dec, which span a range of typical values for conventional short-channel MOSFETs. It can be seen that the enhanced SB-MOSFET achieves a higher on/off current ratio than a conventional MOSFET for  $V_{\rm DD}<\sim0.25~{\rm mV}$ . In Fig. 2.15(b), the on/off current ratios at  $V_{\rm DD}=0.2~{\rm V}$  are presented as a function of temperature. The enhanced SB-MOSFET shows a reduced temperature dependence compared to the lower limit of temperature dependence for a conventional MOSFET. This is consistent with a carrier injection mechanism that is not limited by thermionic emission. One example of a carrier injection mechanism not limited by thermionic emission would be band-to-band tunneling and a previous study of band-to-band tunneling transistors also shows a reduced dependence on temperature [21].

Figure 2.13: SS in the steep-switching regime shows little dependence on  $V_B$ , suggesting that electronic trap states near the silicide/silicon interface provide for an alternative hole injection process.

Figure 2.14: Measured output characteristics of the enhanced SB-MOSFET of Fig. 2.7.  $I_D$  is linear with  $V_{DS}$ , at low values of  $V_{DS}$ . The inset shows a zoomed-out view of the same plot, so that the curves for larger gate biases can be seen.

Figure 2.15: On/off current ratios for the reported device.  $I_{\rm ON}$  is taken to be  $I_{\rm D}$  at  $V_{\rm GS}$  -  $V_{\rm T} = V_{\rm DD}$  while  $I_{\rm OFF}$  is taken to be  $I_{\rm D}$  at  $V_{\rm GS} = V_{\rm T}$ .  $V_{\rm T}$  is defined to be  $V_{\rm GS}$  for  $|I_{\rm D}| = |I_{\rm G}|$ , in this case  $V_{\rm T} = -0.63$  V. In part (a), the on/off current ratio is plotted as a function of  $V_{\rm DD}$  and with log-linear reference lines of 75 mV/dec and 100 mV/dec for comparison. A polynomial fit (grey curve) helps illustrate the low power on/off performance trend for this device. Part (b) shows the on/off current ratio at  $V_{\rm DD} = 0.2$  V as a function of temperature and a lower thermal limit reference line of a conventional MOSFET device calculated for a voltage range of 0.2 V.

#### 2.5 Summary

The experimental results reported in this chapter indicate that the presence of trap states within a narrow, barrier-enhancing doped silicon region next to a Schottky source junction offers an interesting approach towards observing sub-60 mV/dec SS for MOSFET devices. Similar work has been presented in literature.[22–24] Silicide TFET devices presented in the literature perhaps utilize the same or similar operating mechanism, though each article typically explains the steep switching as a result of BTBT. In general, a exponential decay with a high concentration of metal impurity atoms in a transition zone in close proximity to a silicide-silicon interface may augment the electronic band structure such that the effective band gap for tunneling is reduced.

# **Bibliography**

- [1] S. M. Sze, *Physics of Semiconductor Devices*, 2nd ed. Wiley, 1981.

- [2] J. Larson and J. Snyder, "Overview and status of metal S/D Schottky-barrier MOS-FET technology," *Electron Devices, IEEE Transactions on*, vol. 53, no. 5, pp. 1048 –1058, May 2006, ISSN: 0018-9383. DOI: 10.1109/TED.2006.871842.

- [3] L. Hutin, M. Vinet, T. Poiroux, C. Le Royer, B. Previtali, C. Vizioz, D. Lafond, Y. Morand, M. Rivoire, F. Nemouchi, V. Carron, T. Billon, S. Deleonibus, and O. Faynot, "Dual metallic source and drain integration on planar single and double gate SOI CMOS down to 20nm: performance and scalability assessment," in *Electron Devices Meeting (IEDM)*, 2009 IEEE International, Dec. 2009, pp. 1 –4. DOI: 10.1109/IEDM. 2009.5424425.

- [4] Z. Zhang, Z. Qiu, R. Liu, M. Ostling, and S.-L. Zhang, "Schottky-barrier height tuning by means of ion implantation into preformed silicide films followed by drive-in anneal," *Electron Device Letters*, *IEEE*, vol. 28, no. 7, pp. 565–568, Jul. 2007, ISSN: 0741-3106. DOI: 10.1109/LED.2007.900295.

- [5] T Stark, H Grnleitner, M Hundhausen, and L Ley, "Deriving the kinetic parameters for Pt-silicide formation from temperature ramped in situ ellipsometric measurements," *Thin Solid Films*, vol. 358, no. 1-2, pp. 73–79, 2000.

- [6] K. Shenai and R. Dutton, "Current transport mechanisms in atomically abrupt metal-semiconductor interfaces," *Electron Devices, IEEE Transactions on*, vol. 35, no. 4, pp. 468 –482, Apr. 1988, ISSN: 0018-9383. DOI: 10.1109/16.2481.

- [7] E. C. Zingu, C. Comrie, and R. Pretorius, "The effect of interposed silicide thickness on growth rate in bilayer silicide thin-film structures: the Si <111>/Pd<sub>2</sub>Si/Cr system," *Journal of Applied Physics*, vol. 54, no. 5, pp. 2392–2401, 1983. DOI: 10.1063/1.332353. [Online]. Available: http://link.aip.org/link/?JAP/54/2392/1.

- [8] G Larrieu, E Dubois, X Wallart, X Baie, and J Katcki, "Formation of platinum-based silicide contacts: Kinetics, stoichiometry, and current drive capabilities," *JOURNAL OF APPLIED PHYSICS*, vol. 94, no. 12, 7801–7810, Dec. 2003, ISSN: 0021-8979. DOI: {10.1063/1.1605817}.

BIBLIOGRAPHY 27

[9] M. Tsuchiaki, K. Ohuchi, and A. Nishiyama, "Suppression of thermally induced leakage of NiSi-silicided shallow junctions by pre-silicide fluorine implantation," *Japanese Journal of Applied Physics*, vol. 44, no. 4A, pp. 1673–1681, 2005. DOI: 10.1143/JJAP. 44.1673.

- [10] Z. Zhang, J. Lu, Z. Qiu, P.-E. Hellstrom, M. Ostling, and S.-L. Zhang, "Performance fluctuation of FinFETs with Schottky barrier source/drain," *Electron Device Letters, IEEE*, vol. 29, no. 5, pp. 506 –508, May 2008, ISSN: 0741-3106. DOI: 10.1109/LED. 2008.920284.

- [11] E. G. Colgan and F. M. d'Heurle, "Kinetics of silicide formation measured by in situ ramped resistance measurements," *Journal of Applied Physics*, vol. 79, no. 8, pp. 4087–4095, 1996. DOI: 10.1063/1.361771. [Online]. Available: http://link.aip.org/link/?JAP/79/4087/1.

- [12] Z. Qiu, Z. Zhang, M. Ostling, and S.-L. Zhang, "A comparative study of two different schemes to dopant segregation at NiSi/Si and PtSi/Si interfaces for Schottky barrier height lowering," *Electron Devices, IEEE Transactions on*, vol. 55, no. 1, pp. 396–403, Jan. 2008, ISSN: 0018-9383. DOI: 10.1109/TED.2007.911080.

- [13] P. Patel, K. Jeon, A. Bowonder, and C. Hu, "A low voltage steep turn-off tunnel transistor design," in *Simulation of Semiconductor Processes and Devices, 2009. SISPAD '09. International Conference on*, Sep. 2009, pp. 1 –4. DOI: 10.1109/SISPAD.2009. 5290257.

- [14] Z. Zhang, S.-L. Zhang, M. Ostling, and J. Lu, "Robust, scalable self-aligned platinum silicide process," *Applied Physics Letters*, vol. 88, no. 14, 142114, p. 142114, 2006. DOI: 10.1063/1.2194313. [Online]. Available: http://link.aip.org/link/?APL/88/142114/1.

- [15] Z. Zhang, Z. Qiu, P.-E. Hellstrom, G. Malm, J. Olsson, J. Lu, M. Ostling, and S.-L. Zhang, "SB-MOSFETs in UTB-SOI featuring PtSi source/drain with dopant segregation," *Electron Device Letters, IEEE*, vol. 29, no. 1, pp. 125–127, Jan. 2008, ISSN: 0741-3106. DOI: 10.1109/LED.2007.911990.

- [16] Sentaurus Device User Guide. Synopsys, Inc., 2010.

- [17] M. Tsuchiaki, K. Ohuchi, and C. Hongo, "Junction leakage generation by nisi thermal instability characterized using damage-free n+/p silicon diodes," *Japanese Journal of Applied Physics*, vol. 43, no. 8A, pp. 5166–5173, 2004. DOI: 10.1143/JJAP.43.5166. [Online]. Available: http://jjap.jsap.jp/link?JJAP/43/5166/.

- [18] J.-U. Sachse, E. Ö. Sveinbjörnsson, W. Jost, J. Weber, and H. Lemke, "New interpretation of the dominant recombination center in platinum doped silicon," *Applied Physics Letters*, vol. 70, pp. 1584–1586, Mar. 1997. DOI: 10.1063/1.118198.

BIBLIOGRAPHY 28

[19] J. Kedzierski, P. Xuan, E. Anderson, J. Bokor, T.-J. King, and C. Hu, "Complementary silicide source/drain thin-body MOSFETs for the 20 nm gate length regime," in *Electron Devices Meeting*, 2000. IEDM Technical Digest. International, 2000, pp. 57–60. DOI: 10.1109/IEDM.2000.904258.

- [20] R. Jhaveri, V. Nagavarapu, and J. C. S. Woo, "Asymmetric Schottky Tunneling Source SOI MOSFET Design for Mixed-Mode Applications," *IEEE Transactions on Electron Devices*, vol. 56, pp. 93–99, Jan. 2009. DOI: 10.1109/TED.2008.2008161.

- [21] Y. Yoon and S. Salahuddin, "Inverse temperature dependence of subthreshold slope in graphene nanoribbon tunneling transistors," *Applied Physics Letters*, vol. 96, no. 1, 013510, p. 013510, 2010. DOI: 10.1063/1.3280379. [Online]. Available: http://link.aip.org/link/?APL/96/013510/1.

- [22] K. Jeon, W.-Y. Loh, P. Patel, C. Y. Kang, J. Oh, A. Bowonder, C. Park, C. Park, C. Smith, P. Majhi, H.-H. Tseng, R. Jammy, T.-J. Liu, and C. Hu, "Si tunnel transistors with a novel silicided source and 46 mv/dec swing," in *VLSI Technology (VLSIT)*, 2010 Symposium on, Jun. 2010, pp. 121–122. DOI: 10.1109/VLSIT.2010.5556195.

- [23] R. Gandhi, Z. Chen, N. Singh, K. Banerjee, and S. Lee, "Vertical si-nanowire n-type tunneling FETs with low subthreshold swing ( < 50 mV/decade ) at room temperature," *Electron Device Letters, IEEE*, vol. 32, no. 4, pp. 437 –439, Apr. 2011, ISSN: 0741-3106. DOI: 10.1109/LED.2011.2106757.

- [24] —, "CMOS-compatible vertical-silicon-nanowire gate-all-around p-type tunneling FETs with <50 mv/decade subthreshold swing," *Electron Device Letters, IEEE*, vol. 32, no. 11, pp. 1504 –1506, Nov. 2011, ISSN: 0741-3106. DOI: 10.1109/LED.2011. 2165331.

# Chapter 3

# Engineered Electronic Trap States in Tunneling Diodes

#### 3.1 Introduction

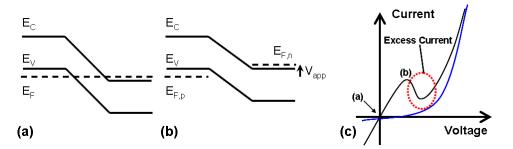

Well documented investigations of the role of traps in band-to-band tunneling (BTBT) typically focus on reverse biased or Esaki-like tunneling diode structures.[1–3] These structures offer simple device physics modeling for studying tunneling since there is only a single pn junction. A motivating factor for investigating trap states and BTBT is the unexplained observation of excess current in Esaki diodes.[4] At a low forward bias, an Esaki diode conducts current primarily via BTBT up to an applied bias corresponding to a peak bias (see Fig. 3.1). When the band overlap reaches zero, BTBT should cease and the current should diminish to the normal forward bias diode current (approximately given by the diode equation). However, an excess current is observed due to tunneling into and out of electronic trap states located within the band gap as well as from states located within the band edge tails.[4]

Figure 1 in [4] schematically presents various trap assisted tunneling routes as a basis for modeling the excess current. Excess current is often attributed to intrinsic defects in crystalline silicon and a deliberate introduction of crystal imperfections by radiation bombardment correlates with a dramatic increase in the excess current (see Figure 4 in [4]).

Early theoretical and experimental investigations into BTBT laid the foundation for understanding the role of tunneling in leakage for scaled down silicon MOSFET devices.[5]<sup>1</sup> Modeling work by Hurkx and later Schenk led to improvements in the BTBT models incorporated into semiconductor device simulations.[3, 5, 6] Qualitatively, when these models are employed in a device simulation, the BTBT generation rate is calculated at each grid point. This generation rate is heavily dependent on the value of the electric field at that grid point. Other factors, such as minority carrier lifetimes and the presence of trap states,

<sup>&</sup>lt;sup>1</sup>For example, increasing the peak doping concentrations or utilizing steep doping profiles while scaling down dimensions

Figure 3.1: An Esaki diode in thermal equilibrium (a). The heavily doped p and n quasi-neutral regions cause band overlap between the valence and conduction bands in the off state. (b) A small forward bias is applied such that the band overlap is zero. (c) Qualitative I-V characteristics for a typical Esaki diode (black line) show excess current greater than the forward bias diode current (blue line) when the applied voltage exceeds the bias point labeled as (b). The bias points for parts (a) and (b) are labeled in part (c).

are incorporated into calibration parameters for improvements to the model. While these models work well in predicting the tunneling rate in and around a reverse biased pn junction, the models do not account for any spatially dependent term in the calculation of the BTBT generation rate.

Figure 3.2: In (a), a BTBT generation rate is calculated with (blue arrow) and without (green dots) a spatial dependence for the tunneling model. Part (b) illustrates both thermal excitation to and from traps (solid green arrow) and an additional path for carriers exiting from traps, field emission tunneling (dashed green arrow). Field emission from the trap is modified in a local tunneling model by calibration parameters.

A spatial dependence is necessary for accurate device structure modeling when the band-

to-band overlap occurs over an appreciable distance. Without a spatially dependent term in the tunneling model, tunneling from an occupied state to an unoccupied state is approximated by a tunneling generation rate calculated at a single point. Additionally, the role of traps is relegated to generation and recombination models near the grid point when the tunneling rate is calculated. Figure 3.2 highlights the difference between a local and nonlocal tunneling model. These models are approximations and therefore insufficient for TFET design and simulation where the role of traps in BTBT is under investigation.

The Synopsys TCAD Sentaurus simulation engine includes a robust dynamic nonlocal BTBT tunneling model which greatly improves the accuracy of TFET simulation and design work. The dynamic nonlocal trap-assisted tunneling model, however, does not explicitly model tunneling into and out of electronic trap states in conjunction with the BTBT tunneling model. [7] Rather, this model incorporates previous trap-assisted tunneling models (e.g., Hurkx and Schenk) with a modified electric field calculated by the maximum of the gradient of the potential profile. This highlights a shortcoming of most tunneling models to accurately calculate discrete tunneling into and out of electronic trap states.

The lack of a robust numerical tunneling model for traps necessitates the use of experimental methods to further investigate the role of traps in BTBT. A powerful analysis for investigating electronic trap state properties is to calculate the activation energy,  $E_{\rm A}$ , from temperature dependent current-voltage measurements (see 2.9). Calculation of the activation energy is possible with an Arrhenius analysis [8] and calculating  $E_{\rm A}$  as a function of the applied bias assists in determining how trap states affect the normal operation of a tunneling device.

For an Arrhenius analysis, the data is presumed to have an exponential dependence related to the thermal energy:

$$I \propto A \cdot \exp\left(\frac{-E_{\rm A}}{k_{\rm B}T}\right)$$

. (3.1)

A is an exponential prefactor and  $k_{\rm B}T$  is the thermal energy. Taking the natural logarithm of both sides yields the slope intercept form  $y=m\cdot x+b$  where the slope is  $\frac{-E_{\rm A}}{k_{\rm B}}$  and the dependent variable is  $\frac{1}{T}$ .

$$\ln\left(I\right) \propto \ln\left(A\right) - \frac{E_{\rm A}}{k_{\rm B}} \cdot \frac{1}{T},\tag{3.2}$$

The slope of a best fit line of the natural logarithm of the temperature dependent data versus  $\frac{1}{T}$  allows the straight forward calculation of  $E_{\rm A}$ . For electronic trap states, determining  $E_{\rm A}$  helps identify the energy level of the trap state as well as the dominant current injection method.

#### 3.2 Impurity Selection for Electronic Trap State

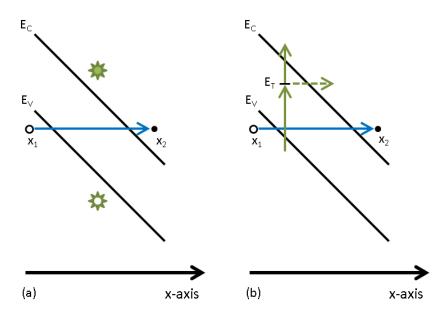

Fig. 3.3 shows four possible routes for carriers to enter and exit an electronic trap state located within the band gap. By lowering the temperature of the semiconductor, carriers

exhibit a lower thermal energy and so reduces the probability of thermal excitation into and out of the trap. Ideally, a low enough temperature will quench the trap assisted thermal excitation process. As suggested in the example in Fig. 3.3, this leads to a greater fractional tunneling component in the generation rate of carriers in the conduction band. An electronic trap state energy level,  $E_{\rm T}$ , appreciably far from both the valence and conduction bands can assist in isolating the role of tunneling into and out of trap states in a dynamically biased semiconductor junction.  $E_{\rm T}$  sufficiently far from both band edges at a low temperature should enhance the tunneling probability into and out of the trap as the thermal excitation probability is decreased. Heterodiodes were fabricated to explore the role of traps states in close proximity to a BTBT junction.

Figure 3.3: Four routes are shown in (a) for carriers entering and exiting a trap state and energy  $E_{\rm T}$ . Thermal excitation is shown in solid green arrows while tunneling into and out of the trap is shown with dashed green arrows. (b) Lowering the temperature of the measurement can reduce the thermal excitation components.

A dated but comprehensive chart of electronic trap state types and energy levels appears in section 1.4.2 of [8]. From the chart in [8], chromium is immediately identified as a single level trap close to the mid-gap of Si ( $E_{\rm C}-E_{\rm T}=0.41\,{\rm eV}$ ). However, very few reports exist detailing the electronic properties of chromium in Si. A more detailed search of the literature suggests erbium (Er) as another likely candidate for engineered electronic trap states.[9–12] A majority of the literature regarding Er impurities in Si focuses on the opto-electronic properties for the purpose of integrated Si based photonics. Er typically exhibits a trap state energy level between the mid-gap of Si and the conduction band edge. A trap located close to the mid-gap of Si is advantageous since a larger energy is necessary to excite a carrier either to or from a trap.

Various reports identify multiple energy levels for Er in Si ranging from  $0.18\,\mathrm{eV} < E_\mathrm{C} - E_\mathrm{T} < 0.6\,\mathrm{eV}$  with mid gap trap states seemingly more likely to occur in [9–11, 13] The concentration of Er atoms, the background doping of the Si, as well as the proximity of oxygen atoms and crystalline defects in the Si all influence the electronic trap state properties. With this in mind, reference [12] notes that the optically active Er concentration is limited to approximately  $3 \cdot 10^{17}\,\mathrm{cm}^{-3}$ . The work reported here targets an Er concentration close to  $10^{17}\,\mathrm{cm}^{-3}$  so as to avoid adverse effects of a high concentration of impurities, some of which may not be fully electronically active.

#### 3.3 Experimental Design Goals

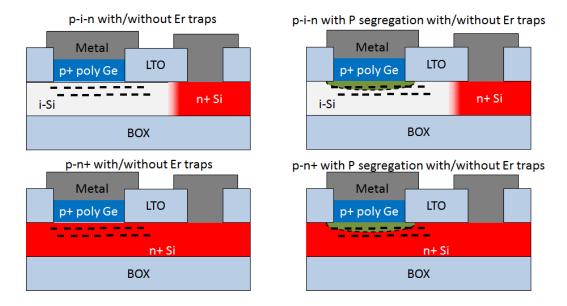

To explore the role of traps in BTBT, Er was purposely introduced into heterodiode devices, schematically depicted in Fig. 3.4. On-wafer splits were employed to provide control samples for co-fabricated devices. The device structures consist of either a p+-i-n+ or p+/n+ heterodiode with p+ poly-germanium (Ge) selectively deposited on the Si surface of an silicon-on-insulator (SOI) wafer. For the Er<sup>+</sup> on-wafer split, the top half of the wafer remained in the original state while the bottom half was implanted with Er<sup>+</sup> ions with a dose of  $7 \cdot 10^{11}$  cm<sup>-2</sup> and an implant energy of 10 keV. Ge was chosen for the heterostructure material since Ge has a lower band gap than Si and poly-crystalline Ge can be selectively deposited onto Si using low pressure chemical vapor deposition (LPCVD). Fig. 3.4 shows four experimental splits incorporated into the top and bottom half of the wafer for a total of eight splits.

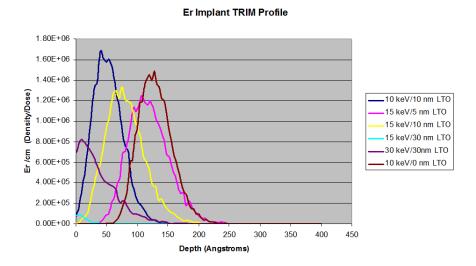

TRIM simulations using SRIM software were used to predict a peak concentration for the device structure.[14] Low temperature oxide (LTO) deposited by LPCVD was used to protect the surface of the structure during ion implantation and can be easily removed with a hydrofluoric (HF) acid wet etch prior to further processing. Fig. 3.5 shows the results of numerical calculations performed by SRIM (using a TRIM calculation) of Er<sup>+</sup> ions implanted into a test structure. Nearly all of the Er<sup>+</sup> ions remain within the first 15nm (150 angstroms) of Si for a 10 keV energy implant through a 10nm thick LTO film. Ideally, engineering the trap profile to be close to the Si surface will promote a trap assisted BTBT (TA-BTBT) process since tunneling junction is designed to coincide with the heterojunction.

Sample preparation involved typical planar processing techniques with the following key fabrication steps listed below:

- Active area definition.

- Er<sup>+</sup> ion implantation for the bottom half of wafer.

Energy = 10 keV, Dose =

$$7.10^{11}$$

cm<sup>-2</sup>

• As<sup>+</sup> ion implantation.

Energy =

$$10 \text{ keV}$$

,  $Dose = 10^{15} \text{ cm}^{-2}$

**Figure 3.4:** Four device structures are shown, each co-fabricated on the same wafer. Each of the four splits was fabricated with and without implanted Er<sup>+</sup> for a total of eight splits. Trap states are represented in the diagrams as narrow hyphenated marks.

Split for a blanket As<sup>+</sup> and masked As<sup>+</sup>. (See Fig. 3.4.) Solid phase epitaxy regrowth (SPER) anneal at 550°C for 4 hours. Rapid thermal anneal (RTA) at 1050°C for 10 seconds.

- Selective p+ poly-Ge deposition with *in situ* doping near 3·10<sup>19</sup> cm<sup>-3</sup>. LPCVD 425°C with 3:1 ratio of BCl<sub>3</sub>:GeH<sub>4</sub> gas flow.

- P<sup>+</sup> ion implantation split.

P segregation anneal for 1 hour at 700°C.

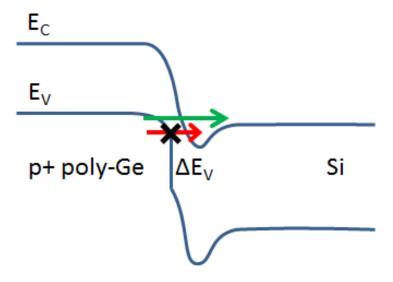

The intention of the phosphorus implant and segregation anneal split is to test a phosphorus "pile up" at the poly-Ge/Si interface. Such a pile up could induce a deeper n-type well as a test for cutting off BTBT at energies from the valley of the well to  $E_{\rm C,Si}$  beyond the well. Fig. 3.6 qualitatively highlights this proposal for cutting off the BTBT near the tunneling heterojunction.

**Figure 3.5:** Erbium ion implantation numerical calculations performed by SRIM software. Various combinations of the Er<sup>+</sup> implant energy and LTO film thickness are displayed. The curves are plotted from the silicon substrate surface and implanted concentrations normalized to the dose.

Figure 3.6: As proposed, an n-type well near the tunneling heterojunction should cut off some BTBT paths. The majority of the band gap difference between Ge and Si is represented by  $\Delta E_{\rm V}$ .

# 3.4 Diode I-V Characteristics and Temperature Dependence