#### Advanced MOSFET Designs and Implications for SRAM Scaling

By

## Changhwan Shin

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Tsu-Jae King Liu, Chair Professor Borivoje Nikolić Professor Eugene E. Haller

Spring 2011

# Advanced MOSFET Designs and Implications for SRAM Scaling

Copyright © 2011

by

Changhwan Shin

#### Abstract

#### Advanced MOSFET Designs and Implications for SRAM Scaling

by

#### Changhwan Shin

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Tsu-Jae King Liu, Chair

Continued planar bulk MOSFET scaling is becoming increasingly difficult due to increased random variation in transistor performance with decreasing gate length, and thereby scaling of SRAM using minimum-size transistors is further challenging. This dissertation will discuss various advanced MOSFET designs and their benefits for extending density and voltage scaling of static memory (SRAM) arrays. Using three-dimensional (3-D) process and design simulations, transistor designs are optimized. Then, using an analytical compact model calibrated to the simulated transistor current-vs.-voltage characteristics, the performance and yield of six-transistor (6-T) SRAM cells are estimated. For a given cell area, fully depleted silicon-on-insulator (FD-SOI) MOSFET technology is projected to provide for significantly improved yield across a wide range of operating voltages, as compared with conventional planar bulk CMOS technology. Quasi-Planar (QP) bulk silicon MOSFETs are a lower-cost alternative and also can provide for improved SRAM yield. A more printable "notchless" QP bulk SRAM cell layout is proposed to reduce lithographic variations, and is projected to achieve six-sigma yield (required for terabit-scale SRAM arrays) with a minimum operating voltage below 1 Volt.

Professor Tsu-Jae King Liu, Chair Dissertation Committee Chair

To my parents for their unbounded love and support, to my brother for his sincere encouragement, and to my wife for her devoted love.

# **Contents**

| Table of Contents                         | 11   |

|-------------------------------------------|------|

| List of Figures                           | viii |

| List of Tables                            | X    |

| Acknowledgements                          | xi   |

| <b>Table of Contents</b>                  |      |

| Chapter 1: Introduction                   | 1    |

| 1.1 Static Random Access Memory (SRAM)    | 1    |

| 1.1.1 SRAM Basics                         | 1    |

| 1.1.2 Alternative SRAM Cell Architectures | 3    |

| 1.1.3 Sources of V <sub>T</sub> Variation | 5    |

| 1.1.3.1 Random Dopant Fluctuations (RDF)  | 6    |

| 1.1.3.2 Gate Length Fluctuations          | 7    |

1.1.3.3 Gate Work-Function Variation (WFV) ......8

1.1.4 Approaches to Mitigating the Impact of V<sub>T</sub> Variation for SRAM ......8

|                | Ç                                                                                                                                  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------|

| 9              | 1.2.1 Planar Silicon-on-Insulator (SOI) MOSFETs                                                                                    |

| 9              | 1.2.1.1 Partially-depleted SOI (PD-SOI) MOSFET                                                                                     |

| 10             | 1.2.1.2 fully-depleted SOI (FD-SOI) MOSFET                                                                                         |

| 12             | 1.2.2 Multiple-Gate MOSFETs                                                                                                        |

| 12             | 1.2.2.1 Double-Gate FinFET and SOI Tri-Gate MOSFETs .                                                                              |

| 13             | 1.2.2.2 Gate-All-Around (GAA) MOSFET                                                                                               |

| 14             | 1.3 Research Objectives and Thesis Overview                                                                                        |

| 15             | 1.4 References                                                                                                                     |

|                |                                                                                                                                    |

|                |                                                                                                                                    |

| 23             | Chapter 2: Performance and Area Scaling Benefits of FD-SOI<br>Technology for 6-T SRAM Cells at the 22nm node                       |

|                | •                                                                                                                                  |

| 23             | Technology for 6-T SRAM Cells at the 22nm node                                                                                     |

| 23             | Technology for 6-T SRAM Cells at the 22nm node  2.1 Introduction                                                                   |

| 23             | Technology for 6-T SRAM Cells at the 22nm node  2.1 Introduction  2.2 Thin-BOX FD-SOI Technology                                   |

| 23<br>23<br>23 | Technology for 6-T SRAM Cells at the 22nm node  2.1 Introduction  2.2 Thin-BOX FD-SOI Technology  2.2.1 MOSFET Design Optimization |

| V <sub>DD</sub>                                                                                                                                                                                                                      | •               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 2.4 Yield-Aware SRAM Cell Design                                                                                                                                                                                                     | 31              |

| 2.4.1 Iso-Area Comparison                                                                                                                                                                                                            | 32              |

| 2.4.2 Iso-Yield Comparison                                                                                                                                                                                                           | 33              |

| 2.4.3 Minimum Operating Voltage $(V_{min})$ for read and write operation                                                                                                                                                             | 33              |

| 2.5 Summary                                                                                                                                                                                                                          | 34              |

| 2.6 References                                                                                                                                                                                                                       | 35              |

|                                                                                                                                                                                                                                      |                 |

| 2.A Appendix                                                                                                                                                                                                                         | 37              |

| 2.A Appendix  Chapter 3: Study of Random Dopant Fluctuation (RDF) Effects for the Quasi-Planar Bulk MOSFET                                                                                                                           |                 |

| Chapter 3: Study of Random Dopant Fluctuation (RDF) Effects                                                                                                                                                                          | 38              |

| Chapter 3: Study of Random Dopant Fluctuation (RDF) Effects for the Quasi-Planar Bulk MOSFET                                                                                                                                         | <b>38</b><br>38 |

| Chapter 3: Study of Random Dopant Fluctuation (RDF) Effects for the Quasi-Planar Bulk MOSFET  3.1 Introduction                                                                                                                       | 38<br>38        |

| Chapter 3: Study of Random Dopant Fluctuation (RDF) Effects for the Quasi-Planar Bulk MOSFET  3.1 Introduction  3.2 Device Simulation Approach                                                                                       | 38<br>39        |

| Chapter 3: Study of Random Dopant Fluctuation (RDF) Effects for the Quasi-Planar Bulk MOSFET  3.1 Introduction  3.2 Device Simulation Approach  3.2.1 Nominal Bulk MOSFET Designs                                                    | 383939          |

| Chapter 3: Study of Random Dopant Fluctuation (RDF) Effects for the Quasi-Planar Bulk MOSFET  3.1 Introduction  3.2 Device Simulation Approach  3.2.1 Nominal Bulk MOSFET Designs  3.2.2 Methodology for Atomistic Device Simulation | 38393939        |

| 3.3.3 Assessment of V <sub>TH</sub> Adjustment Approaches                       | 43 |

|---------------------------------------------------------------------------------|----|

| 3.4 Summary                                                                     | 45 |

| 3.5 References                                                                  | 45 |

| Chapter 4: Full three-dimensional Simulation of 6-T SRAM Cell for the 22nm node |    |

| 4.1 Introduction                                                                | 47 |

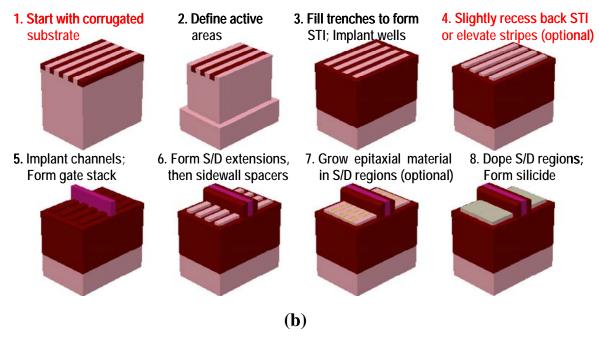

| 4.2 Segmented Bulk MOSFET Structure and Fabrication Process                     | 49 |

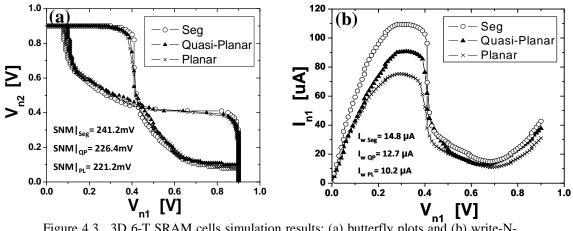

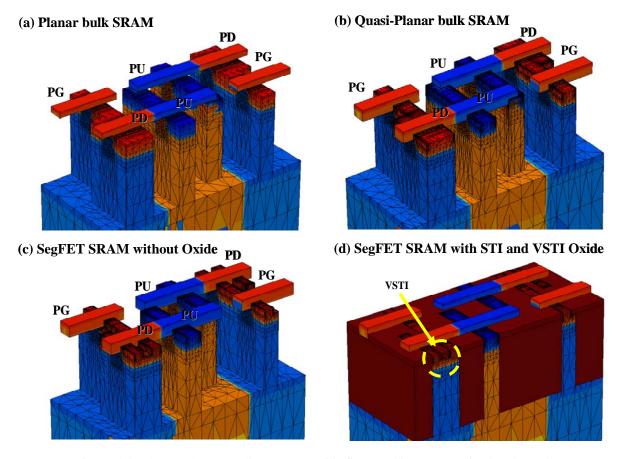

| 4.3 6-T SRAM Cell Designs                                                       | 49 |

| 4.4 Global and Local Variation Analysis                                         | 52 |

| 4.5 Simulation of Single-Event-Upset                                            | 53 |

| 4.6 Summary                                                                     | 55 |

| 4.7 References                                                                  | 55 |

| Chapter 5: Quasi-Planar Bulk CMOS Technology for Improved SRAM Scalability      | 58 |

| 5.1 Introduction                                                                | 58 |

| 5.2 Device Fabrication                                                          | 59 |

| 5.3 Results and Discussion                                                      | 61 |

| 5.3.1 Quasi-Planar vs. Planar MOSFETs                                                                           |

|-----------------------------------------------------------------------------------------------------------------|

| 5.3.1.1 Improved Performance                                                                                    |

| 5.3.1.2 Suppressed V <sub>TH</sub> Variation62                                                                  |

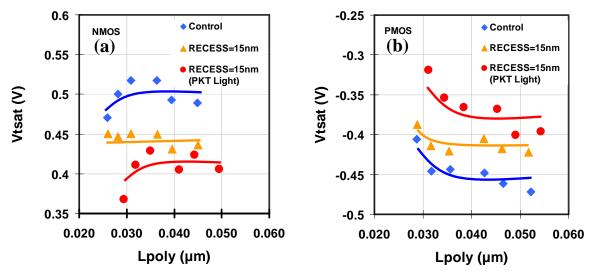

| 5.3.1.3 Improved Short-Channel Effect                                                                           |

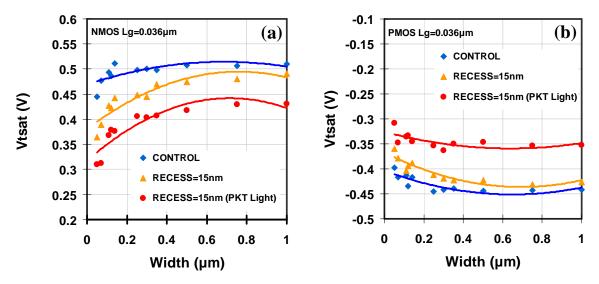

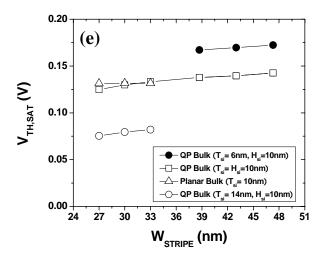

| 5.3.1.4 Increased Narrow Width Effect                                                                           |

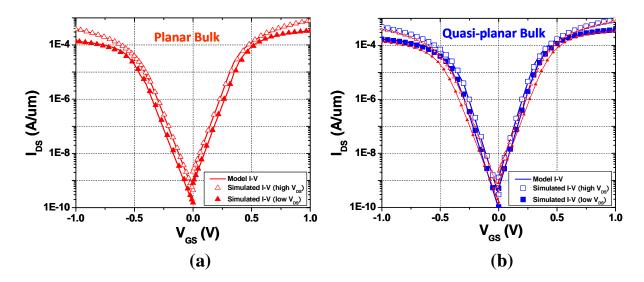

| 5.3.1.5 Compact Transistor Model65                                                                              |

| 5.3.1.4 Increased Narrow Width Effect                                                                           |

| 5.3.2 Benefits of Quasi-Planar Bulk CMOS Technology for 6-T SRAM67                                              |

| 5.3.2.1 Cell Yield Enhancement                                                                                  |

| 5.3.2.2 Supply-Voltage Reduction                                                                                |

| 5.3.1.2 Suppressed V <sub>TH</sub> Variation62                                                                  |

| 5.4 Summary68                                                                                                   |

| 5.5 References69                                                                                                |

|                                                                                                                 |

| Chapter 6: Performance and Yield Benefits of Quasi-Planar Bulk CMOS Technology for 6-T SRAM at the 22 nm Node71 |

| 6.1 Introduction71                                                                                              |

| 6.2 Quasi-Planar Bulk Technology                                                                                |

| 6.2.1 Optimized MOSFET Performance                                                                              |

| 6.2.2 Impact of Rando                 | om and Systematic Variations                              | 75 |

|---------------------------------------|-----------------------------------------------------------|----|

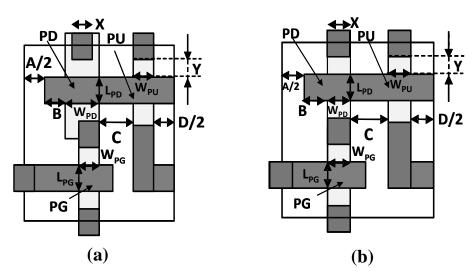

| 6.3 Notchless 6-T SRAM Cell D         | Designs                                                   | 77 |

| 6.4 SRAM Yield Estimation             |                                                           | 81 |

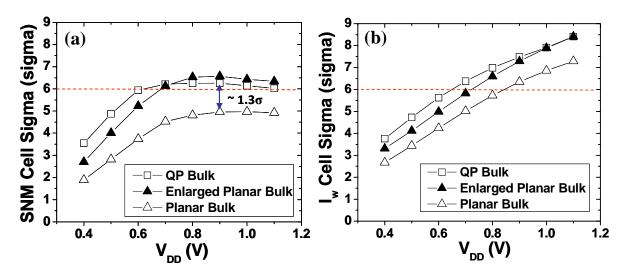

| 6.4.1 Iso-Area and Iso between Planar | o-Yield Comparisons<br>and Quasi-Planar Bulk Cell Designs | 81 |

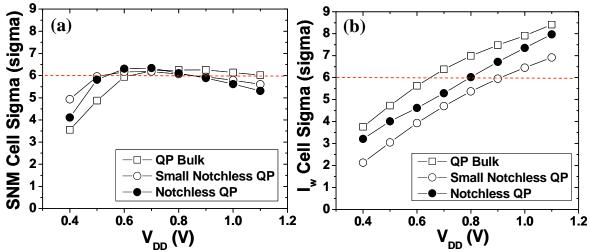

| 6.4.2 Notchless Quas                  | si-Planar Bulk SRAM Cell Yield                            | 82 |

| 6.5 Summary                           |                                                           | 83 |

| 6.6 References                        |                                                           | 83 |

| Chapter 7: Conclusion                 |                                                           | 87 |

| 7.1 Contribution of This Work         |                                                           | 87 |

| 7.2 Suggested Future Work             |                                                           | 90 |

| A. Improved M                         | Ianufacturability                                         | 91 |

| B. Independen                         | nt Biasing Transistors                                    | 92 |

| C. Compatibil                         | ity with Advanced Device Architecture                     | 92 |

| 7.3 References                        |                                                           | 93 |

# **List of Figures**

| 1.1 Circuit schematic for a six-transistor (6-T) SRAM cell                       | 2     |

|----------------------------------------------------------------------------------|-------|

| 1.2 Definition of the static noise margin and write-ability current              | 3     |

| 1.3 Alternative SRAM bit-cell architecture                                       | 4     |

| 1.4 Standard deviation of threshold voltage vs. channel length                   | 5     |

| 1.5 Randomly distributed dopant atoms in an n-channel MOSFET                     | 6     |

| 1.6 Illustration of a nano-scale MOSFET showing line-edge-roughness              | 7     |

| 1.7 Illustration of hypothetical metal gate film                                 | 8     |

| 1.8 Transmission electron micrograph image of a PD-SOI n-MOSFET with HK/MG       | 9     |

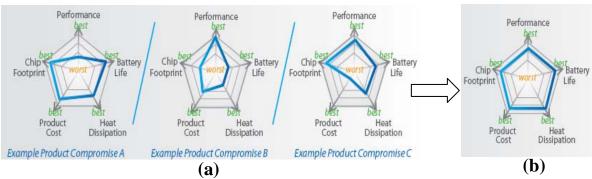

| 1.9 Product design compromises for planar bulk, PD-SOI, and FD-SOI               | 10    |

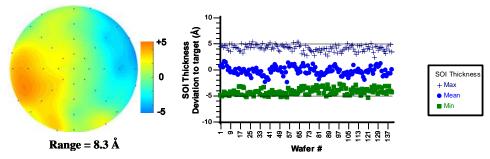

| 1.10 Experimental data for SOI layer thickness variation                         | 11    |

| 1.11 FD-SOI technology features                                                  | 12    |

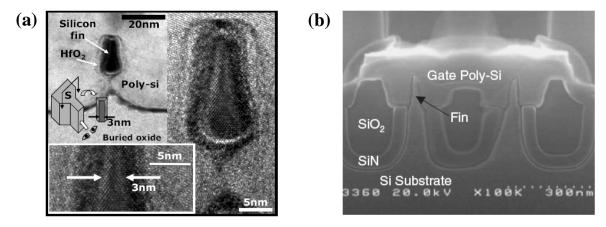

| 1.12 Transmission electron micrograph image of FinFET structures                 | 13    |

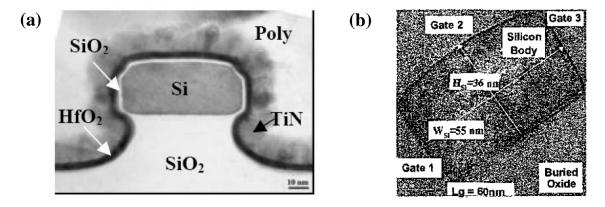

| 1.13 Transmission electron micrograph image of Omega-/Tri-gate MOSFET structure  | es 13 |

| 1.14 Transmission electron micrograph image of twin silicon nanowire MOSFET      | 14    |

|                                                                                  |       |

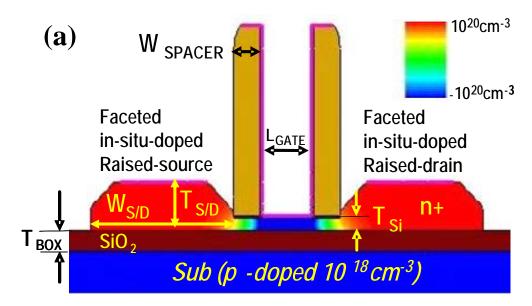

| 2.1a Cross-sectional view of a thin-BOX FD-SOI MOSFET structure                  | 24    |

| 2.1b Experimental data for SOI thickness variation                               | 25    |

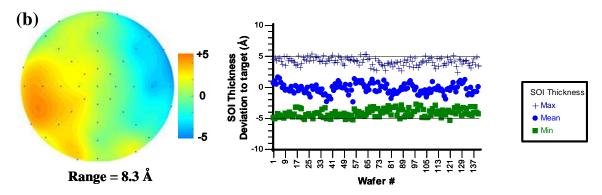

| 2.2 Transfer characteristics of planar bulk and FD-SOI MOSFETs                   | 26    |

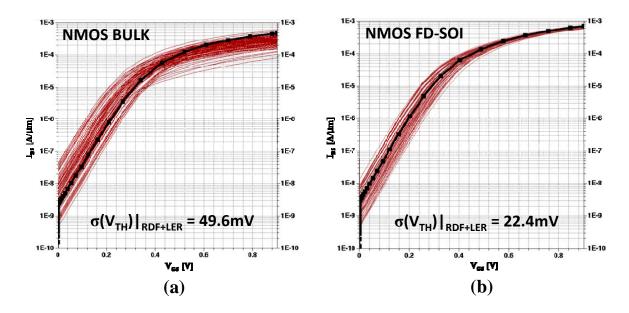

| 2.3 Simulated I-V curves of pull-down transistor for LER/RDF                     | 26    |

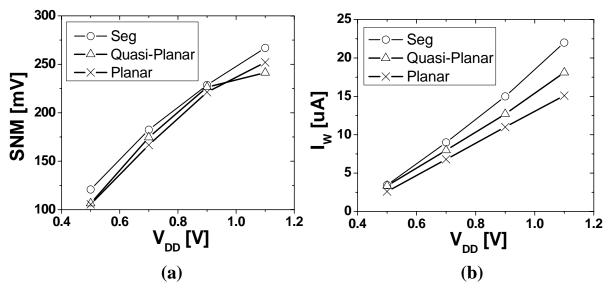

| 2.4 Comparisons of SNM and write current                                         | 29    |

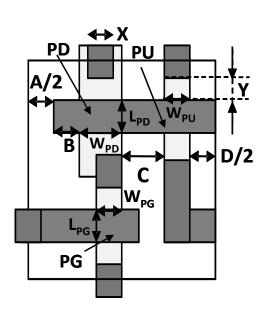

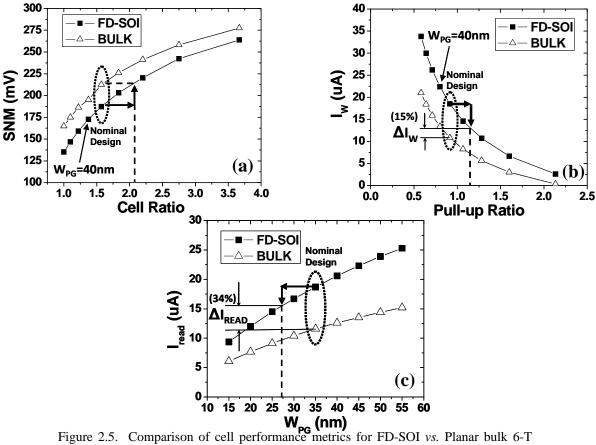

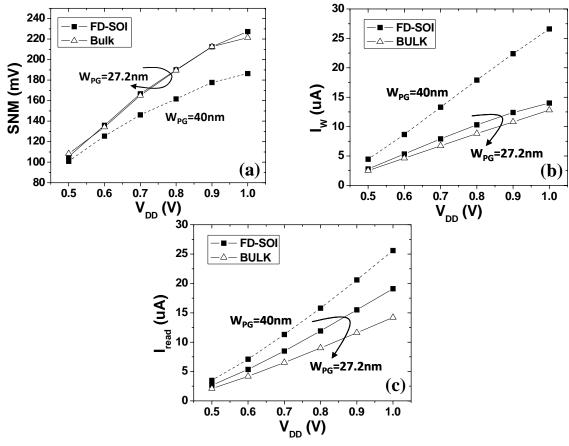

| 2.5 Comparison of SRAM cell performance metrics                                  | 30    |

| 2.6 Impact of V <sub>DD</sub> scaling on 6-T SRAM cell performance metrics       | 31    |

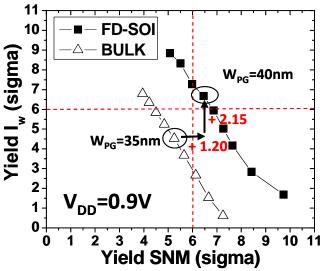

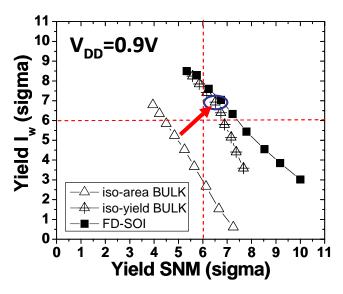

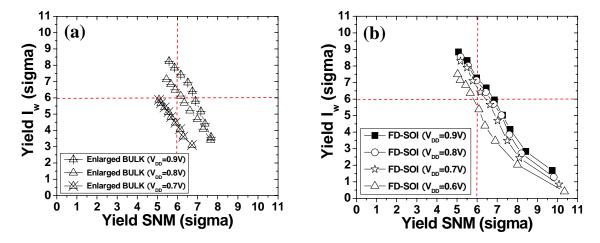

| 2.7 Yield of I <sub>w</sub> vs. Yield of SNM for FD-SOI and planar bulk          | 32    |

| 2.8 Yield of I <sub>w</sub> vs. Yield of SNM for FD-SOI and enlarged planar bulk | 33    |

| 2.9 Dependence of yield on V <sub>DD</sub>                                       | 34    |

|                                                                                  |       |

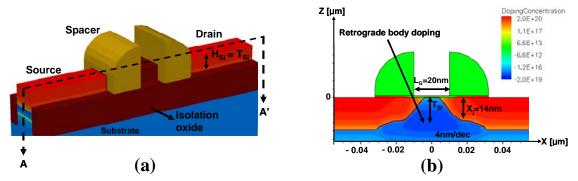

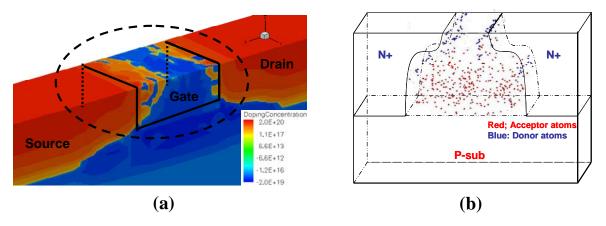

| 3.1 3D bird-eye view and cross-sectional view of the quasi-planar bulk MOSFET    | 39    |

| 3.2 Example of a QP bulk MOSFET with atomistic doping profiles and isometric vie | ew 40 |

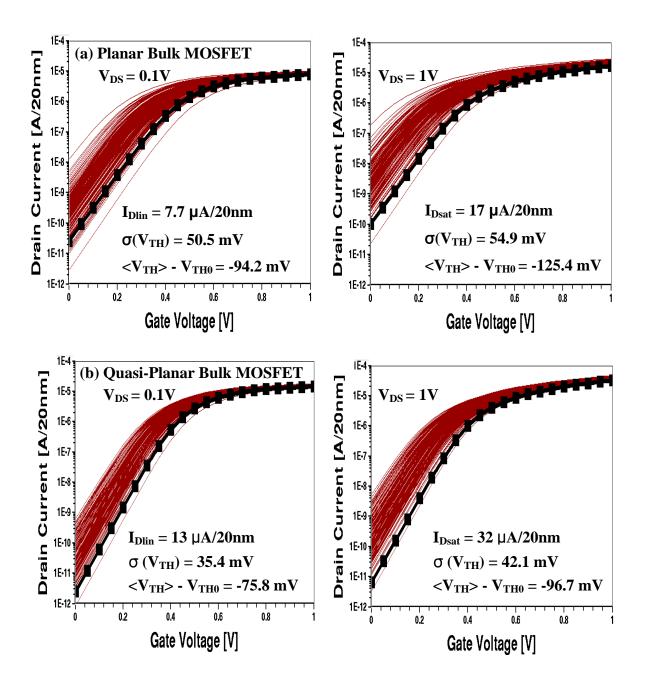

| 3.3 Simulated I-V curves for planar and QP bulk MOSFETs with atomistic doping    | 41    |

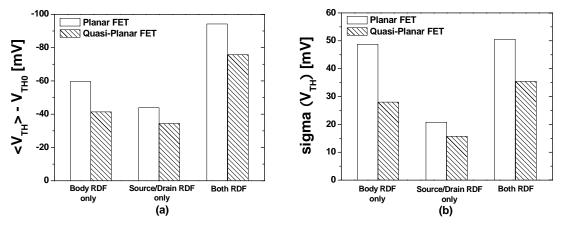

| 3.4 Comparison of body RDF vs. source/drain RDF effects                          | 43    |

| 3.5 Impact of nominal $V_{TH}$ adjustment on $V_{TH}$ variation                  | 44    |

|                                                                                  |       |

| 4.1a Cross-sectional views of a two-striped SegFET                               | 48    |

| 4.1b Front-end-of-line fabrication process steps for a SegFET                    | 48    |

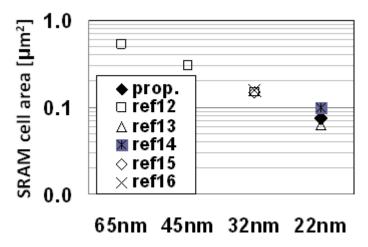

| 4.2 6T-SRAM cell area scaling trend                                                   | 49    |

|---------------------------------------------------------------------------------------|-------|

| 4.3 3D 6-T SRAM cells simulation results                                              | 50    |

| 4.4 3D 6T-SRAM cell structures with fine meshing                                      | 51    |

| 4.5 SNM and $I_w vs. V_{DD}$                                                          | 52    |

| 4.6 SegFET vs. planar MOSFET comparison                                               | 53    |

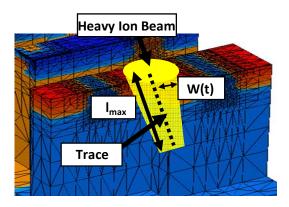

| 4.7 Heavy ion beam modeling                                                           | 54    |

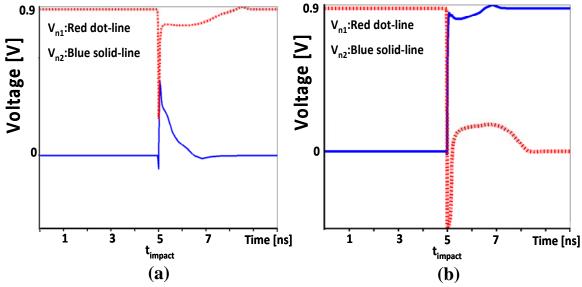

| 4.8 Transient simulations of heavy-ion-beam strike on the high storage node           | 54    |

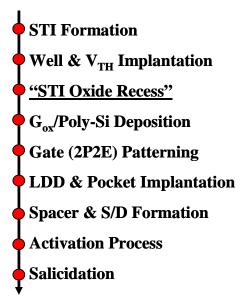

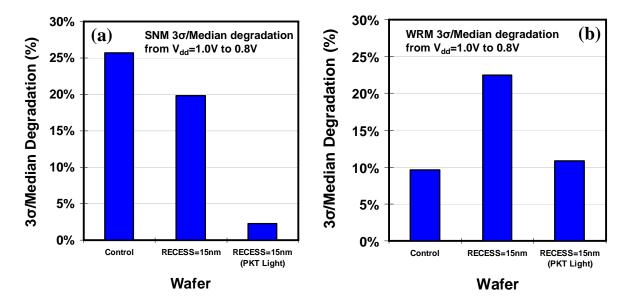

| 5.1 Sequence of front-end-of-line CMOS fabrication process steps for QP MOSFET        | 60    |

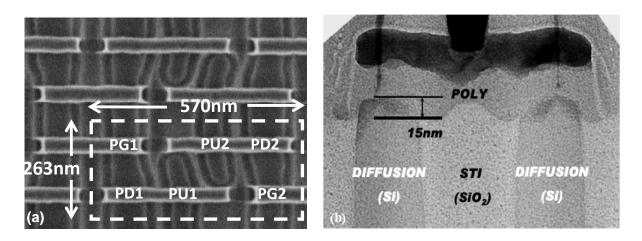

| 5.2a 0.149µm² SRAM cell plan-view CDSEM image after gate patterning                   | 60    |

| 5.2b XTEM taken along a poly-Si gate electrode in an SRAM array                       | 60    |

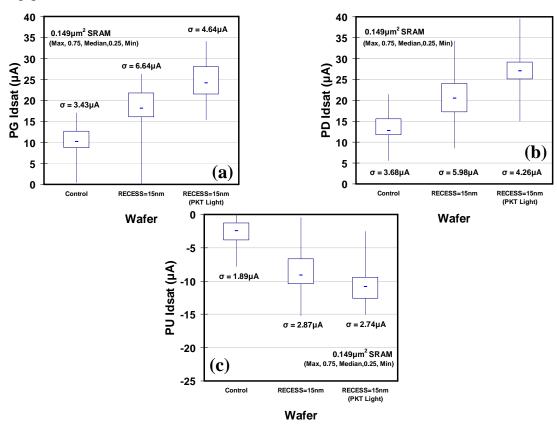

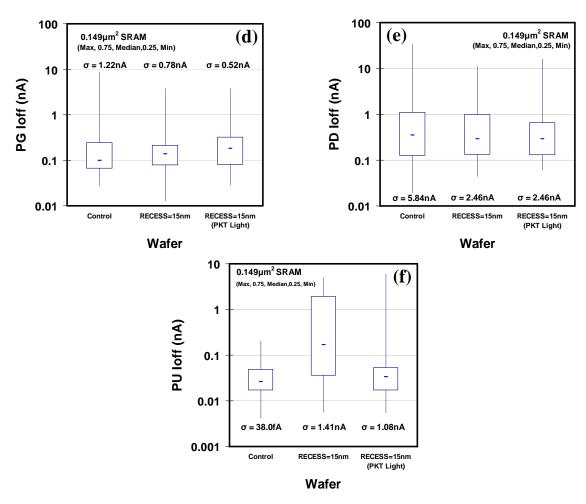

| 5.3 Comparison of ON/OFF current statistics for planar vs. QP MOSFETs                 | 61-62 |

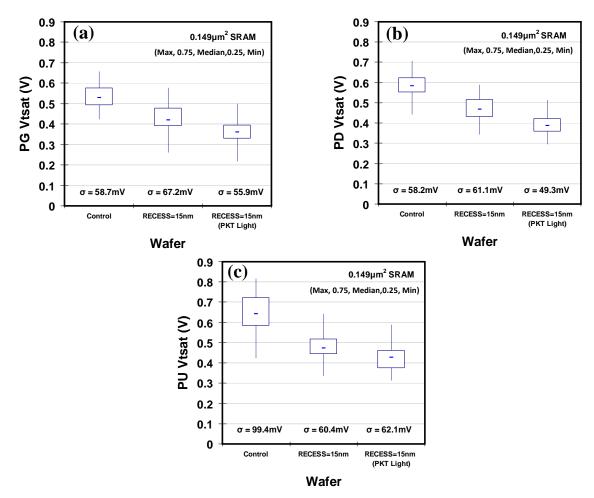

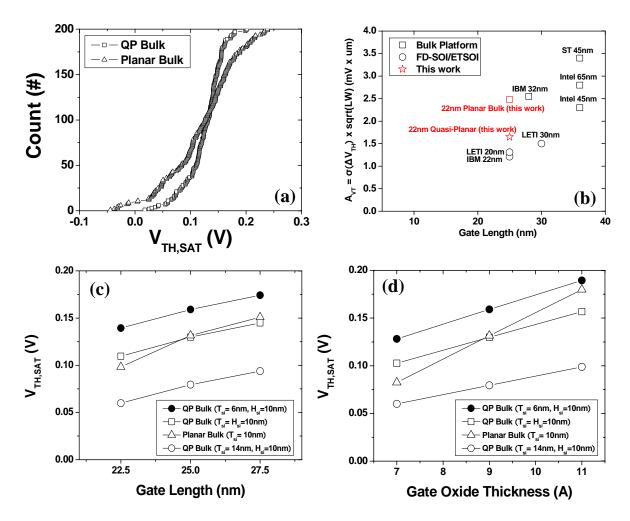

| 5.4 Comparison of saturation $V_{TH}$ statistics for planar vs. QP MOSFETs            | 63    |

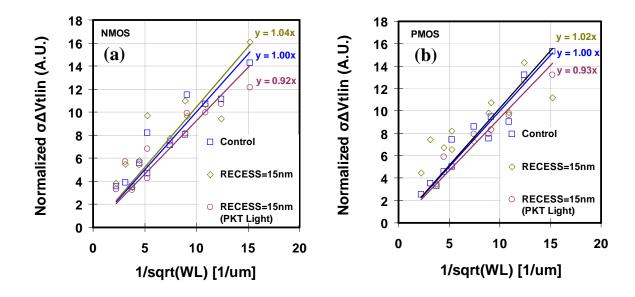

| 5.5 Pelgrom plots for NMOS and PMOS logic devices                                     | 64    |

| 5.6 Saturation threshold voltage with decreasing gate length                          | 64    |

| 5.7 Measured reverse narrow width effect for devices with 36nm gate length            | 65    |

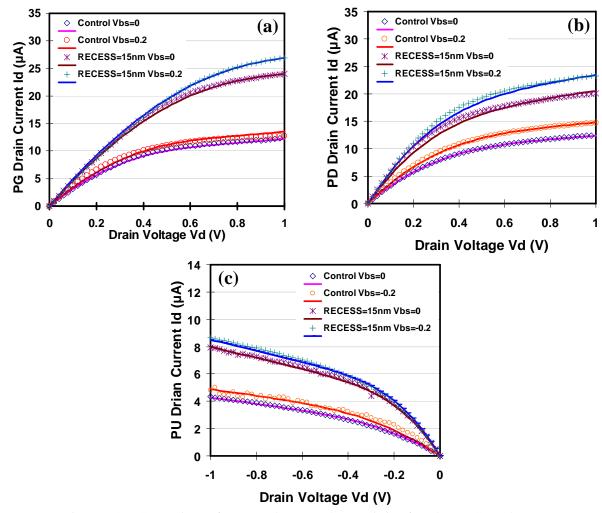

| 5.8 Comparison of measured and modeled output characteristics                         | 66    |

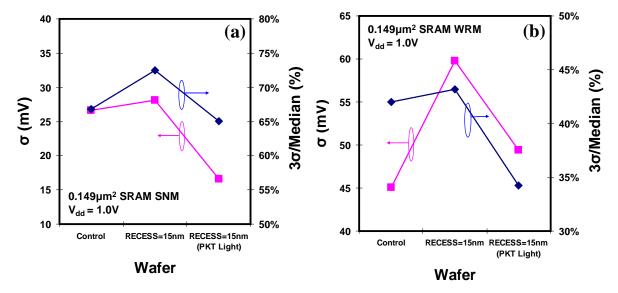

| 5.9 Sigma and 3-sigma/median values for SNM and WRM                                   | 67    |

| 5.10 Degradation in 3-sigma/median for SNM and WRM                                    | 68    |

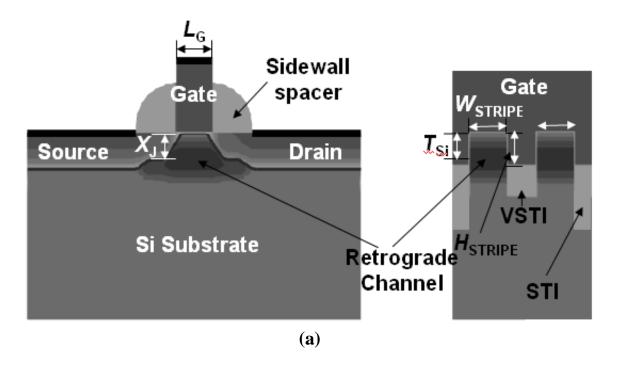

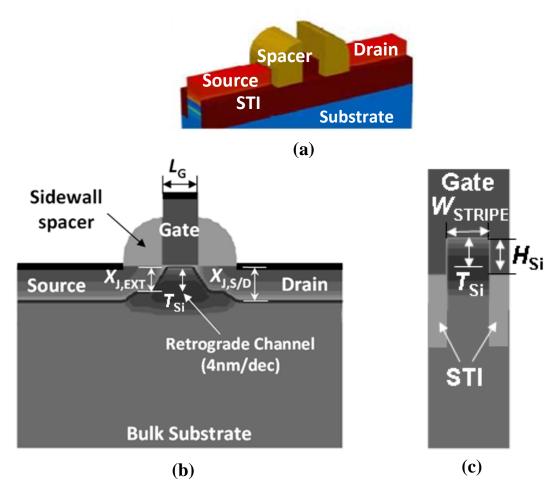

| 6.1 Bird-eye view of a quasi-planar bulk MOSFET and along/across the channel          | 72    |

| 6.2 Simulated transfer characteristics for planar and quasi-planar bulk MOSFETs       | 73    |

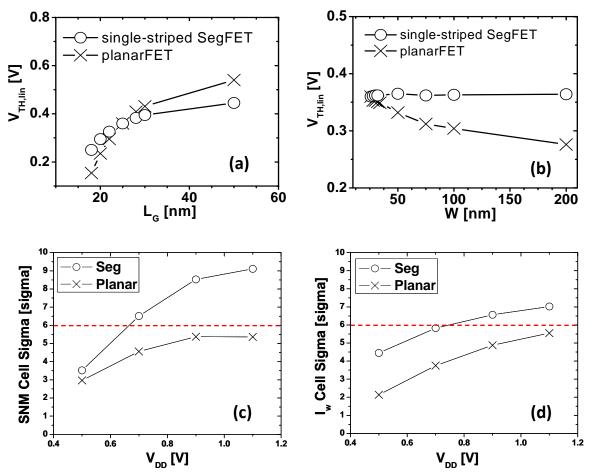

| 6.3 Simulated V <sub>TH,SAT</sub> for planar bulk vs. quasi-planar bulk MOSFETs       | 76    |

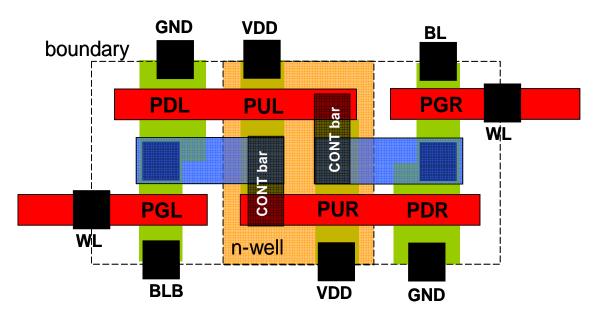

| 6.4 Half-bit cell layouts for notched and notchless SRAM cell designs                 | 78    |

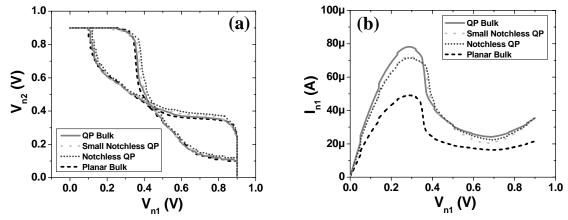

| 6.5 3-D 6-T SRAM cell simulation results                                              | 79    |

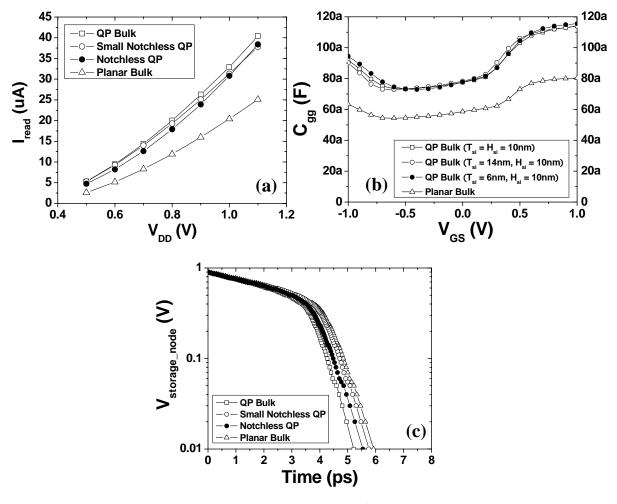

| 6.6a SRAM cell read current                                                           | 80    |

| 6.6b PD device gate capacitance                                                       | 80    |

| 6.6c Pseudo-transient simulation of the storage-node voltage during a write operation | . 80  |

| $6.7$ SRAM cell sigma comparisons for SNM and $I_W$                                   | 82    |

| $6.8$ SRAM cell sigma comparisons for SNM and $I_W$                                   | 82    |

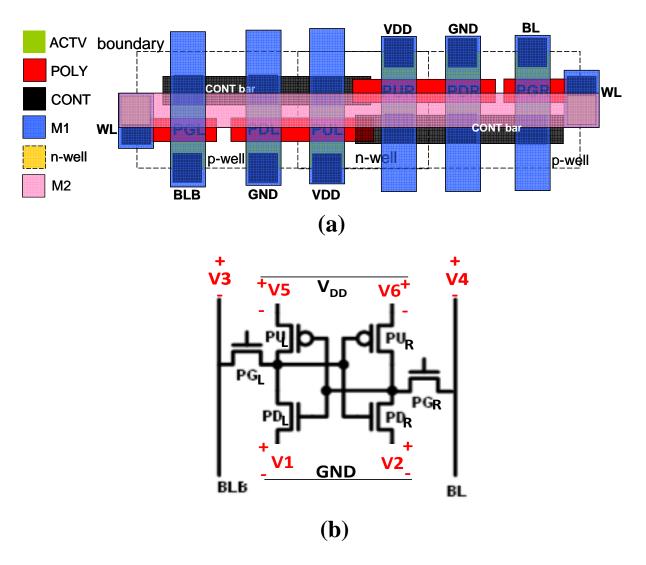

| 7.1a Proposed new layout of the 6-T SRAM bit-cell                                     | 91    |

| 7.1b Circuit schematic of the 6-T SRAM bit-cell with external voltage skews           | 91    |

| 7.2 Conventional layout of a 6-T SRAM bit-cell                                        | 92    |

# **List of Tables**

| 2.1 | Optimized thin-BOX FD-SOI and Planar bulk MOSFET design parameters       | 25 |

|-----|--------------------------------------------------------------------------|----|

| 2.2 | Comparison of device performance parameters for $V_{DD} = 0.9 \text{ V}$ | 26 |

| 2.3 | FD-SOI 6-T SRAM cell dimensions                                          | 29 |

| 2.4 | Summary of SRAM cell performance metrics                                 | 34 |

| 4.1 | SegFET 6T-SRAM cell dimensions for the 22nm node                         | 50 |

| 6.1 | Summary of transistor performance parameters                             | 74 |

| 6.2 | 22nm-node 6-T SRAM cell layout parameters                                | 79 |

| 6.3 | Comparison of projected performance metrics and cell areas               | 81 |

| 7.1 | Comparison of three different device architectures                       | 9( |

# Acknowledgements

During my time at Berkeley, lots of people have sincerely guided my research. I would like to begin by appreciating all of their kind help.

In fact, I could not write this page without expressing my deepest thanks to my academic advisor, Professor Tsu-Jae King Liu, who is the epitome of a great mentor and guided me from unsure beginning as a fresh researcher to the bleeding-edge in my field of study. She has always been cordial, attentive, available and supportive throughout all the peaks and valleys of my Ph.D. course. In all research meeting, she never failed to advise me with her inspiring perspective, amazing engineering-intuition, tireless enthusiasm, and firm and solid knowledge. There is much about her management style that I would like to bring with me as I go into industry and/or academia.

I am grateful for all the support and advice of Professor Borivoje Nikolić, chairing my qualifying examination and serving as a member of my dissertation committee. His keen perspective on SRAM was exceptionally helpful, and his sincere advice on leading my research opportunities toward a very meaningful contribution to device and circuit cooptimization was tremendously valuable.

I also thank Professor Eugene E. Haller for serving on both my qualifying examination committee and my dissertation committee, and thank Professor Sayeef Salahuddin for serving my qualifying examination committee.

Dr. Yasumasa Tsukamoto, former visiting scholar, provided invaluable guidance on SRAM designs, for which I am greatly grateful. His firm and rigorous SRAM knowledge has provided a great advantage toward understanding SRAM and all its tradeoffs. His experience in industry was also helpful for my research and future career. I hope to be as informative and impactful with my future colleagues as he is with his.

Dr. Si-woo Lee, another former visiting scholar, became my wise counselor for both my research and life. While he was staying at Berkeley, I learned something new from him every day.

I would like to thank several former and current students with regards to this work. With Dr. Andrew Carlson, Dr. Xin Sun, Min Hee Cho, and Nattapol Damrongplasit, I could establish the foundation of my research. They provided kind assistance and several helpful discussions on SRAM, advanced device structures, and their variability. With Dr. Zheng Guo, Seng Oon Toh, Aikaterini Papadopoulou, and Jaehwa Kwak, I had a lot of discussions on SRAM in test chips. They also kindly assisted with the logistics of tapeout and testing.

In addition to the above, several others have provided indirect assistance. Dr. Donovan Lee and Dr. Joanna Lai helped me, among many other things, to acquire an American English language and to adapt myself to new circumstances at Berkeley. Jemin Park and Kanghoon Jeon sincerely helped me in times of need. Prof. Man Young Sung, Prof. Suki Kim, Prof. Soo-Won Kim, Prof. Tae-Geun Kim, Prof. Sang Bin Lee, Prof. Jae-Sung Rieh, Prof. Tae-Woong Yoon, Prof. James Jungho Pak, Prof. Woo-Young Choi, Prof. Songhwai Oh, Prof. Hyuck Choo, Dr. Vidya Varadarajan, Dr. Alvaro Padilla, Dr. Reinaldo Vega, Dr. Hei Kam, Dr. Louis Hutin, Dr. Jiwoong Lee, Dr. Daekyeong Moon, Dr. Jaein Jeong, Dr. Chuck Choongyeun Cho, Dr. Kihoon Kim, Dr. Gregory Freeman, Dr. Dae-kyu Park, Jason Cheng, Rhesa Nathanael, Zachery Jacobson, Wookhyun Kwon, Jaeseok "Jay" Jeon, Sung Hwan Kim, Byron Ho, Nuo Xu, Peter Matheu, Eung Seok Park, I-Ru "Tim" Chen, Yenhao "Philip" Chen, Jack Yaung, Sriramkumar V., Darsen D. Lu, Stan Baek, Ji-Hoon Park, Namseog Kim, Jung-Dong Park, Kwangmo Jung, Tae Joon Seok, Se Yong Park, Changho Suh, Kyoohyun Noh, Sunyoung Lee, Hyojin Kim, Hyerin Lee, Kangwook Lee, Sangyoon Han, Youngki Yoon, Shinwon Kang, Hongki Kang, Jaewon Jang, Chang-Seo Park, Yunsup Lee, Hyun Oh Song have also provided technical, educational, personal assistance in some form. I appreciate all of their help.

This work has been funded through a few sources. First of all, my financial stability for my Ph.D. work came from the Korea Foundation of Advanced Studies (KFAS) Fellowship. This work was also supported in part by the Center for Circuit & System Solutions (C2S2) Focus Center, which is one of five research centers funded under the Focus Center Research Program (a Semiconductor Research Corporation program). In addition, fabrication of a 28nm test chip for studying 28nm quasi-planar bulk technology and data for FD-SOI wafer was donated by UMC (Dr. Cheng-Tzung Tsai and all the other UMC engineers involved to the 28nm test chip) and Soitec (especially, Dr. Carlos Mazuré and Mrs. Bich-Yen Nguyen), respectively. I would like to express my sincere gratitude for the financial and technical supports, and I will not forget to contribute back to them in future.

Finally, I would not be here today were it not for my family. I can not thank my parents and my younger brother enough for their unbounded love and sacrifices. Their love will always hold a special place in my heart. Lastly, but most certainly not least, I would like to thank my wife, Yun Jeong Hwang, for her devoted love. She is my light at the end of the long tunnel, and I appreciate her.

# **Chapter 1**

# Introduction

Improvement in integrated circuit (IC) performance and cost has been achieved largely by transistor scaling (*i.e.*, minimum feature size reduction by a factor of 0.7 in every new technology node, or every 2 years) according to Moore's Law [1, 2]. The resultant exponential growth in device count per chip has been led by the miniaturization of the static-random-access-memory (SRAM) bit-cell. Increasing process-induced variations in transistor performance with miniaturization down to the 22 nm technology node and beyond is a major technical challenge for continued advancement of planar-bulk/partially-depleted silicon-on-insulator (PD-SOI) complementary metal-oxide-semiconductor (CMOS) technology [3, 4]. In particular, continued SRAM cell-area scaling for increased storage density, reduction in operating voltage (V<sub>DD</sub>) for lower stand-by power consumption, and enhanced yield necessary to realize larger-capacity SRAM arrays (*i.e.*, embedded level-2 or level-3 cache memory for microprocessor) become increasingly difficult to achieve. This thesis explores the benefits of advanced transistor structures and bit-cell design co-optimization for continued SRAM scaling.

# 1.1 Static Random Access Memory (SRAM)

#### 1.1.1 SRAM Basics

The SRAM cell incorporates a static latch, comprising two cross-coupled inverters, so that it does not require *periodic refreshing* to retain the stored information, provided that there is adequate power supply voltage for the cell (V<sub>DD.cell</sub>).

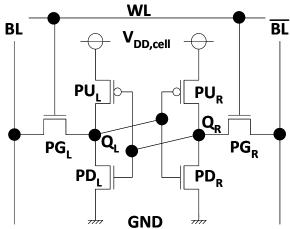

Figure 1.1. Circuit schematic for a six-transistor (6-T) SRAM cell, the most commonly used SRAM bit-cell architecture.

**Fig. 1.1** shows the most commonly used SRAM bit-cell architecture, that is the six-transistor (6-T) SRAM cell. It consists of two cross-coupled inverters (PMOS pull-up transistors  $PU_L$  and  $PU_R$  and NMOS pull-down transistors  $PD_L$  and  $PD_R$ ) and two access transistors (NMOS pass-gate transistors  $PG_L$  and  $PG_R$ ). When the horizontally-running word-line (WL) is enabled (*i.e.*, a row is selected in an array), the access transistors are turned on, and connect the storage nodes to the vertically-running bit-lines (BL and  $\overline{BL}$ ). In other words, they allow access to the cell for read and write operations, acting as bidirectional transmission gates.

The 6-T SRAM cell operates as follows: (1) For a read operation, the bit-lines are usually pre-charged to a high level (V<sub>DD</sub>) and then the word-line is selected (pulsed to a high level). On the side of the cell storing a logical '0' (i.e., a low voltage), the bit-line is discharged via the pass-gate transistor and pull-down transistor, so that a differential voltage develops between the bit-lines. This differential voltage should be large enough for a sense amplifier to detect the state of the cell. The differential voltage should not be too large, however; otherwise the cross-coupled inverters could flip their state. (The read operation should be *non-destructive*.) The cell beta ratio, which is the ratio of the strength (drive current) of the pull-down transistor to that of the pass-gate transistor, should be sufficiently large to ensure that such a read disturbance does not occur. (2) For a write operation, the bit-lines are driven to complementary voltage levels via a write driver and then the word-line is selected. On the side of the cell for which the bit-line voltage is logical '0' (i.e., a low voltage), the internal storage node is discharged through the pass-gate transistor. The cross-coupled inverters raise the voltage on the opposite storage node and latch the cell. The discharging strength of the pass-gate transistor must overcome the restoring strength of the pull-up transistor. The cell gamma ratio, which is the ratio of the strength of the pass-gate transistor to that of the pull-up transistor, should be sufficiently large to ensure that write failure does not occur.

Figure 1.2. (a) Definition of the static noise margin (SNM) from the read voltage transfer characteristics (VTC), or "butterfly curves" for a 6-T SRAM cell. The inset shows the biasing conditions for read operation. (b) Definition of the write-ability current from the write "N-curve." The inset shows the biasing conditions for write operation. Note that the storage node  $Q_L$  is at logical '0' voltage level.

Since Seevinck's seminal work [5] in 1987, the most common metric for SRAM read stability is the read static noise margin (SNM), illustrated in **Fig. 1.2(a)**. SNM is the maximum tolerable DC noise voltage at a storage node that does not cause a read disturbance, and it is the length of the side of the largest square that can fit into the "eyes" of the butterfly curves, *i.e.*, the read voltage transfer characteristics (VTC), for the SRAM cell. The other metric for read stability utilizes the read N-curve [6, 7], which is measured by sweeping the voltage at the storage node  $Q_L$  (or  $Q_R$ ) via the bit-line, with the word-line and two bit-lines biased at  $V_{DD}$ , and monitoring the current sourced into the storage node.

The write N-curve illustrated in Fig. 1.2(b) is obtained by sweeping the voltage at the storage node  $Q_R$  ( $Q_L$ ), with BL (BL) and WL biased at  $V_{DD}$  and BL (BL) biased at GND, and monitoring the current sourced into the storage node. The write-ability current [8, 9],  $I_w$ , is defined as the minimum current past the inverter  $PU_L$ - $PD_L$  trip point, and is a measure of the difference between  $PG_R$  and  $PU_R$  currents.

#### 1.1.2 Alternative SRAM Cell Architectures

As explained in the previous section, the transistors within a 6-T SRAM cell must be sized properly (since drive current is proportional to transistor width) for the cell to meet both read and write margin specifications to guarantee proper operation. There is a fundamental tradeoff, therefore, between cell yield and cell layout area (*i.e.*, cost). This tradeoff is worsened by the need to include design margin for process-induced variations in transistor threshold voltage ( $V_T$ ) since drive current is a function of  $V_{DD} - V_T$ .

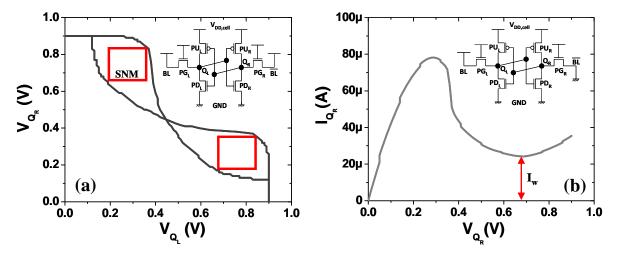

Figure 1.3. Alternative SRAM bit-cell architectures: (a) 4-T SRAM cell, (b) 7-T SRAM cell, (c) 8-T SRAM cell, and (d) 10-T SRAM cell.

Various alternative SRAM bit-cell architectures have been proposed to reduce cell area or to decouple the requirements for read stability and write-ability. The 4-T SRAM cell (**Fig. 1.3(a**)) consists of two PMOS pass-gate transistors and two NMOS pull-down transistors, resulting in relatively smaller cell area than the 6-T SRAM design [10-15]. It

maintains a logical '1' state at one of the internal storage nodes via PMOS transistor offstate leakage current. This results not only in higher static power consumption but also in larger susceptibility to V<sub>T</sub> variation (since transistor off-state leakage current varies exponentially with V<sub>T</sub>), so that the 4-T SRAM cell architecture is not promising for sub-22 nm SRAM technologies. The 7-T SRAM cell (Fig. 1.3(b)) [16] utilizes dedicated wordlines and bit-lines for read vs. write operations to avoid the possibility of a read disturbance even if the read SNM is lower than 0, so that minimum-width transistors can be used for minimal cell area. Takeda et al. [17] demonstrated 23% area-savings for a layoutoptimized 7-T SRAM array (vs. a 6-T SRAM array), for the same operating speed. However, it has complexity in layout. The 8-T SRAM cell (Fig. 1.3(c)) [18-21] also utilizes dedicated word-lines and bit-lines for read vs. write operations, but uses complementary bit-lines for write operation as does a 6-T SRAM cell. Write disturbance is still a general issue for these alternative cell architectures. The 10-T SRAM cell (Fig. 1.3(d)) [22] decouples the storage nodes from the bit-lines to improve read stability, but requires the use of peripheral write-assist circuitry. These alternative SRAM cell architectures each have undesirable tradeoffs in cell area or performance as compared to the 6-T SRAM cell. This thesis therefore focuses on technological approaches to improve the scalability of the 6-T SRAM cell.

#### 1.1.3 Sources of V<sub>T</sub> Variation

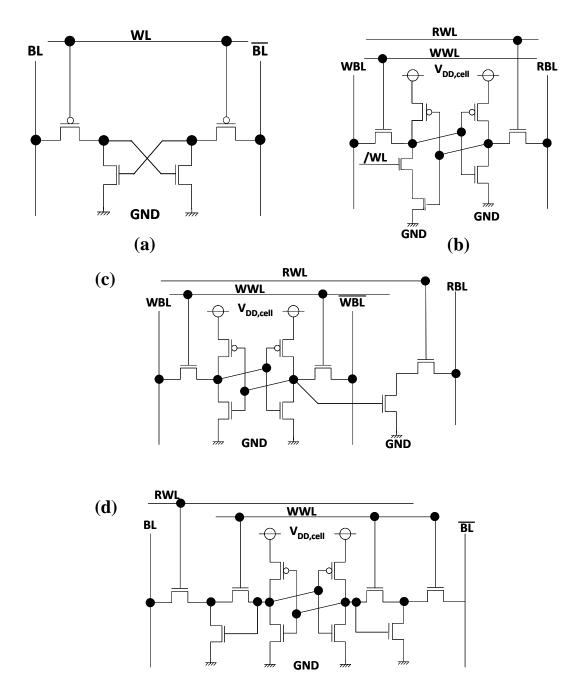

$V_T$  variation is caused by two types of sources: systematic and random. Systematic sources include lithography-induced variations in channel length and width, which are deterministic and predictable. Random sources include as gate line-edge-roughness (LER), random-dopant-fluctuation (RDF), and gate work-function variation (WFV), which are non-deterministic and are projected to be the dominant sources of  $V_T$  variation for transistors with channel length below 30 nm, as shown in **Fig. 1.4** [23].

Figure 1.4. Standard deviation of threshold voltage variation *vs.* channel length, for square planar bulk MOSFETs. Constant gate line edge roughness (4 nm) is assumed [23].

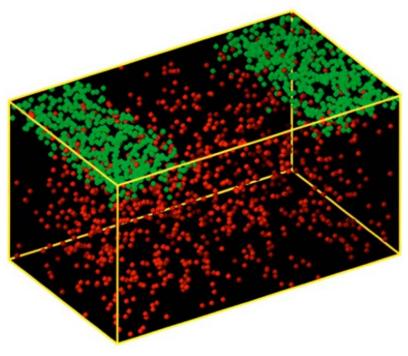

Figure 1.5. Randomly distributed dopant atoms in an n-channel MOSFET with channel length of 30 nm and channel width of 50 nm [24]. (Green-colored atoms are donors and red-colored atoms are acceptors.)

## 1.1.3.1 Random Dopant Fluctuations (RDF)

In the early 1970s, Keyes explored the effects of random fluctuation in the number of impurity atoms [25], as one of the issues for continued transistor scaling. Experiments confirmed his theory, for a wide range of fabricated devices [26]. Analytical models [3] and three-dimensional (3D) fine-grid statistical device simulations [27, 28] were subsequently used to understand and predict RDF-induced  $V_T$  variation in deep sub-micron devices. It is well known that RDF-induced  $V_T$  is inversely proportional to  $(W \times L)^{0.5}$ , where W and L are the transistor channel width and length, respectively. Recently, in a 100,000-sample 3D simulation study [29], the complete  $V_T$  distribution caused by RDF was constructed through the discrete convolution of a Poisson distribution with the mean (N) of the number of dopants in channel region, and a Gaussian distribution of  $V_T$  for a fixed N. As the channel doping and/or halo doping in conventional Planar-bulk/PD-SOI MOSFETs is increased with scaling to suppress short-channel effects, RDF-induced variation will worsen. The use of a lightly doped (fully depleted) SOI MOSFET structure with a thin (~10 nm-thick) buried oxide (BOX) and a heavily doped substrate has been reported to be effective for suppressing this variation [30].

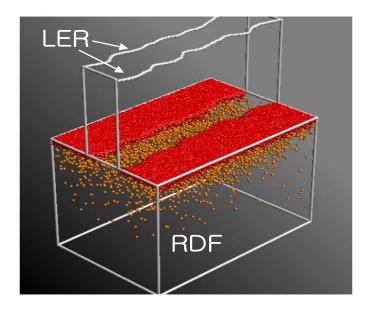

Figure 1.6. Illustration of a nano-scale MOSFET showing gate line-edge-roughness across the width of the transistor, with randomly placed dopants in the source/drain and channel regions [31].

#### 1.1.3.2 Gate Length Fluctuations

Polymer erosion at the edges of a photoresist line during the development process has been shown to create a rough profile [32, 33]. As a result, a lithographically patterned gate electrode exhibits line edge roughness (LER) across the width of the transistor, as shown in **Fig. 1.6**. Gate LER is not only dependent on the photoresist material and coat and develop process conditions, but also on the gate material microstructure and etch process conditions. As shown in **Fig. 1.4**, LER can become the dominant source of random V<sub>T</sub> variation for gate lengths below 20 nm, if it does not scale down with the transistor minimum dimension. Spacer gate lithography [34, 35] can suppress LER-induced variation in transistor performance, and is effective even if LER does not scale because the LER for the "outer edges" of the spacers will be strongly correlated with that of the "inner edges".

In addition to LER, proximity effects can affect the width of a developed photoresist feature. Diffraction effects limit the resolution of modern optical projection lithography systems: higher-order diffraction components are lost due primarily to the finite size of the focusing lens, resulting in a loss of fidelity in the printed image manifest as corner rounding. The use of a lens with higher NA (Numerical Aperture) results in a higher fidelity image.

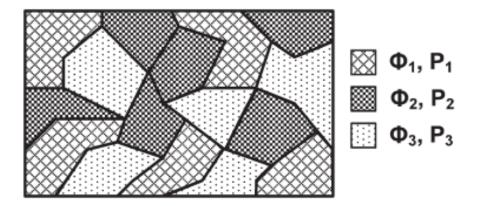

Figure 1.7. Illustration of a hypothetical metal gate film comprising grains of three different orientations and hence three different work-function values ( $\Phi_1 \sim \Phi_3$ ), each orientation having a certain occurrence probability ( $P_1 \sim P_3$ ) [36].

#### 1.1.3.3 Gate Work-Function Variation (WFV)

Beginning at the 45 nm generation of CMOS technology, advanced gate stack materials *i.e.*, high-permittivity gate dielectric and metal gate (HK/MG), have been used to reduce the effective gate-oxide thickness and thereby improve the electrostatic integrity of nano-scale transistors. As illustrated in **Fig. 1.7**, a metal film typically comprises microcrystalline grains of various orientations, each with an associate work function (WF). The random distribution of grains within a metal gate film results in a probabilistic distribution of WF values. WFV can become a significant source of random V<sub>T</sub> variation in future transistors with nano-scale gate length. Dadgour [36, 37] highlighted and experimentally verified this source of random V<sub>T</sub> fluctuation in HK/MG transistors and proposed a statistical framework to investigate device- and circuit-level implications.

## 1.1.4 Approaches to Mitigating the Impact of $V_T$ Variation for SRAM

Random V<sub>T</sub> variation presents a serious challenge for scaling SRAM cell area and operating voltage to the 22 nm technology node and beyond. Circuit-design approaches to address this challenge include read-assist and write-assist techniques which enhance SRAM read and write margins, respectively. Examples of these include read/write-assist column circuitry, word-line bias, pulsed bit lines, lower column supply voltages during write, and negative voltage on bit-line [38, 39]. These techniques inevitably result in lower array area efficiency. A complementary approach is to improve the robustness of the transistor design

to process-induced  $V_{\rm T}$  variation. In the following section, various advanced transistor designs are introduced.

# 1.2 Advanced Transistor Designs for the 22 nm Node and Beyond

New technologies have been introduced to enable continued scaling of the planar bulk MOSFET structure beyond the 130 nm technology node. These include HK/MG gate stacks [40, 41] and channel stress technology (*e.g.*, strained-silicon substrate [42], embedded-Si<sub>1-x</sub>Ge<sub>x</sub> (Si<sub>1-x</sub>C<sub>x</sub>) for p-channel (n-channel) MOSFETs [43], and raised source/drain [44]). Since the planar bulk MOSFET requires a heavily doped channel region and/or halo doping to suppress DIBL (Drain Induced Barrier Lowering) and the short-channel effect (V<sub>T</sub> reduction with decreasing gate length), it inevitably suffers RDF effects. To avoid the use of heavy channel doping, thin body (fully depleted) and multi-gate transistor structures have been investigated in recent years.

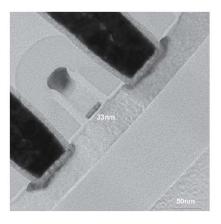

Figure 1.8. Transmission electron micrograph image of a partially depleted silicon-on-insulator (SOI) n-channel MOSFET with HK/MG stack. The channel length is 33 nm [45].

### 1.2.1 Planar Silicon-on-Insulator (SOI) MOSFETs

## 1.2.1.1 Partially-depleted SOI (PD-SOI) MOSFET

Partially depleted silicon-on-insulator (PD-SOI) transistors (**Fig. 1.8**) [45, 46] are used for high-performance applications because they have significantly reduced junction capacitances (the buried oxide (BOX) layer is typically >100 nm thick) and hence increased circuit operating speed compared to bulk silicon MOSFETs. However, PD-SOI MOSFETs suffer from the "floating-body" effect [47]: if the body region is not tied to a bias voltage, then majority carriers generated by impact ionization (when the transistor is in the on state)

accumulate in the body region and forward-bias the source junction, effectively lowering  $V_T$ . This results in an increase in on-state current that is dependent on the transistor operating history [48, 49]. In addition, like the planar bulk MOSFET, a PD-SOI MOSFET still requires a heavily doped channel region and/or halo doping to reduce DIBL and  $V_T$  roll-off, and thus inevitably suffers from RDF effects which limit its scalability.

#### 1.2.1.2 Fully-depleted SOI (FD-SOI) MOSFET

Increasing variability in transistor and circuit performance for planar bulk and/or PD-SOI CMOS technology requires more complex chip design, and hence results in non-optimal product design (**Fig. 1.9(a**)) [50]. Rather than doping the channel heavily to suppress off-state leakage, it can be made to be very thin to eliminate sub-surface leakage paths and reduce DIBL [51]. In the latter case, the channel/body region is so thin (with a thickness that is less than one fourth of the transistor channel length) that it is fully depleted of mobile charge carriers when the transistor is in the off state. Such a fully depleted MOSFET structure is most easily implemented with an extremely-thin SOI substrate [52]. The floating-body effect is negligible in an FD-SOI MOSFET because there is no quasineutral body region which serves as a potential well to hold majority carriers [53]. Also, RDF-induced V<sub>T</sub> variation can be dramatically lower in a FD-SOI MOSFET since light channel/body doping can be used [54]. FD-SOI technology compares well against planar bulk technology across key figures of merit (**Fig. 1.9(b**)). The same chip design flow can be used for FD-SOI technology as for planar bulk technology, which is advantageous for reduced design cost and time-to-market [54].

Figure 1.9. (a) There are product design compromises for planar bulk and/or PD-SOI CMOS technology. (b) FD-SOI technology is superior across all figures of merit [50].

FD-SOI technology faces a number of challenges for widespread adoption. First is the need for uniformly thin Si films. For gate lengths ( $L_g$ ) below 15 nm, the Si thickness ( $T_{si}$ ) should be less than 4 nm [52] in order to control short channel effect (*i.e.*,  $T_{si}$  should be less than a quarter of physical gate length). In this thickness range, quantum confinement effects (which cause  $V_T$  to increase geometrically with decreasing  $T_{si}$ ) make  $V_T$  very sensitive to variations in  $T_{si}$  [55]. Second is parasitic resistance associated with ultra-thin

source/drain regions. By thickening the source/drain regions via selective epitaxial growth, this resistance can be reduced, but at the cost of increased gate-to-source/drain capacitance [56]. Metallic source/drain regions can be used [57], but then a very low Schottky barrier technology would be needed. Third is the need for thin-BOX substrates to allow for  $V_T$  tuning via sub-BOX doping and/or dynamic  $V_T$  control via back-biasing [58], which come at the cost of increased source/drain junction capacitance. Recent progress in the manufacture of SOI substrates with uniformly ultra-thin Si ( $T_{si} \sim 10$  nm) and thin BOX ( $T_{BOX} \sim 25$  nm or less) has enabled successful demonstrations of nano-scale FD-SOI devices [59]. **Fig. 1.10** shows measured  $T_{si}$  variation across a wafer and across many wafer batches. The SOI Consortium is now promoting FD-SOI technology as a solution that can meet requirements for mobile applications with regard to power consumption, performance, manufacturability, scalability, and cost efficiency (**Fig. 1.11**).

Figure 1.10. Experimental data (courtesy of Soitec) for SOI layer thickness ( $T_{si}$ ) variation across a wafer (left) and from wafer to wafer (right). The peak-to-peak variation is less than 1 nm [59].

| М | obile Consumer                     | Great Apps, Faster Web Browsing, Dazzling Multimedia, Fantastic User Interaceswithout draining the battery                                      |                                                                             |                                                                                                                                                                            |                                                                 |

|---|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| 4 | Equipment                          | Avoiding system over-heat                                                                                                                       | Cost-optimize                                                               | d for Consumer Market                                                                                                                                                      | Longer usage time                                               |

|   | System                             | Superior "Power - Performance - Area - Cost - Time to Market" balance, across all use cases                                                     |                                                                             |                                                                                                                                                                            |                                                                 |

|   | I (Low Power operation/retention): |                                                                                                                                                 | Less design guard-band<br>Easier Timing Closure                             | s required                                                                                                                                                                 |                                                                 |

| П |                                    | Superior Analog Behavior  High Peak Performance Remarkable Performance at lower Vdd                                                             |                                                                             | Opportunities of enhanced efficiency for SoC<br>Design Techniques: Voltage Scaling (DVFS),<br>Retention Modes, Back-bias etc.  Flexibility to exploit new operating points |                                                                 |

| П |                                    |                                                                                                                                                 |                                                                             |                                                                                                                                                                            |                                                                 |

|   |                                    | Area efficiency                                                                                                                                 |                                                                             |                                                                                                                                                                            |                                                                 |

|   |                                    | Intrinsically low leakage                                                                                                                       |                                                                             | Essentially unchanged design flows, tools and methodologies                                                                                                                |                                                                 |

|   |                                    | Good receptivity to back-bias                                                                                                                   |                                                                             |                                                                                                                                                                            |                                                                 |

|   | Silicon<br>Technology              |                                                                                                                                                 |                                                                             | No 'Floating Body' or other SOI-specific effect                                                                                                                            |                                                                 |

|   |                                    | Excellent electrostatic and electrical behavior of transistors (DIBL, Subthreshold slope, GIDL, junction leakage) even in very small geometries |                                                                             | Co-integration of traditional bulk CMOS legacy + FD-SOI on same chip possible                                                                                              |                                                                 |

|   |                                    | Same fab equipment                                                                                                                              |                                                                             | Simpler process                                                                                                                                                            |                                                                 |

|   | Technology<br>Fundamentals         | Extremely uniform Ultra-Thin SOI starting wafers available for high volume manufacturing                                                        | <ul><li> Ultra-Thin Bo</li><li> Undoped Ch</li><li> Ultra-thin Bu</li></ul> |                                                                                                                                                                            | Planar CMOS approach<br>with no unconventional<br>process steps |

Figure 1.11. FD-SOI technology features lead to benefits for mobile products [50].

#### **1.2.2** Multiple-Gate MOSFETs

#### 1.2.2.1 Double-Gate FinFET and SOI Tri-Gate MOSFETs

The fundamental concept behind a multiple-gate MOSFET (in which the gates are all tied together) is to increase gate control (*vs.* drain control) of the channel potential, particularly the source-to-channel potential barrier. The double-gate MOSFET has two gates located on opposing sides of the Si channel/body region, to control the channel potential. It is most easily implemented as a vertical structure, with a single gate electrode running across (straddling the two opposing sides of) a tall and narrow Si channel/body "fin." This "FinFET" structure has been widely investigated [60-64], and can be implemented either on an SOI substrate [65] or a bulk-Si substrate [66] (**Fig. 1.12**).

To adequately suppress short-channel effects, the width of the Si fin in a FinFET should be uniformly less than one half of the channel length. For good layout area efficiency, the height of the Si fin should be tall [67] (>3x its width). The formation of tall and uniformly narrow Si fins presents significant manufacturing challenges, not only for lithography and etch processes but also for doping processes. High-tilt-angle ion implantation or plasma doping or solid-source diffusion are necessary to dope the source/drain regions. For bulk-Si FinFETs, the need for steep retrograde "channel-stop" doping at the bases of the tall fin channel/body regions presents a significant processing challenge. V<sub>T</sub> control is another manufacturing challenge for FinFET technology. For low-power (high V<sub>T</sub>) applications, a single gate material with work function corresponding to a Fermi level near the middle of the Si energy bandgap can be used. To achieve lower values of V<sub>T</sub>, tuning of the gate work function, or the use of different gate materials, is required [68]. (Alternatively, precise reduction in electrical channel length can be used [69].) Dynamic V<sub>T</sub> control requires physical separation and independent biasing of the front and back gates, which comes at the cost of added process complexity and layout area [70]. A design challenge for FinFET technology is the fact that transistor strength is adjusted not by changing the Si width but by changing the number of fins [60]. Thus, adaptations in automated design tools and cell libraries will be necessary for FinFET technology to be used for general purpose logic applications. For these reasons, the adoption of FinFET technology has been delayed. It is anticipated that FinFETs will be first used only in SRAM arrays where low leakage is imperative.

To mitigate the need for ultra-narrow Si fins, gating of additional channel surfaces as in the omega-gate [71, 72] and tri-gate SOI MOSFET [73] structures have been proposed (**Fig. 1.13**). These structures still face the same challenges of  $V_T$  control and design flow adaptation as the FinFET, however.

Figure 1.12. Transmission electron microscopy images of FinFET structures: (a) sub-5 nm gate length SOI FinFET with 3 nm-width fin and 1.4 nm-thick HfO<sub>2</sub> gate dielectric. A blurry boundary delineates the source extension region [65]. (b) Bulk-Si FinFET after gate patterning and contact opening [66].

Figure 1.13. Transmission electron microscopy images of (a) Omega-gate FET with a 60 nm-wide channel/body and TiN/HfO2 gate stack [72], (b) Tri-Gate SOI MOSFET [73].

## 1.2.2.2 Gate-All-Around (GAA) MOSFET

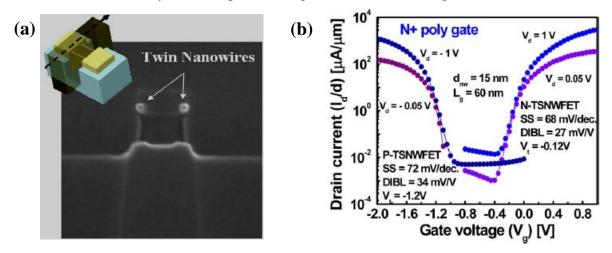

The best possible gate control is achieved by gating all of the channel surfaces, as in a Gate-All-Around (GAA) MOSFET. Thus, the most scalable transistor design is a nanowire MOSFET. As shown in **Fig. 1.14**, Suk et al. [74, 75] fabricated a GAA twin silicon nanowire MOSFET (TSNWFET) with 5-nm-radius, 30-nm-long channels on a bulk silicon wafer. N- and p-channel drive currents are 2.37 mA/ $\mu$ m and 1.30 mA/ $\mu$ m for off-state currents of 6.2 nA/ $\mu$ m and 6.7 pA/ $\mu$ m at  $V_{DD}=1$  V, respectively. (A mid-gap gate work function is needed to achieve symmetric NMOS and PMOS V<sub>T</sub> values.) Excellent gate control is evidenced by low sub-threshold swing (<70 mV/dec) and DIBL < 25 mV/V. The

major disadvantages of the GAA MOSFET are that it is difficult to manufacture with high precision, and that the current flow per nanowire is relatively low. Therefore, GAA MOSFETs are unlikely to be adopted for large-scale manufacturing in the near future.

Figure 1.14. (a) Cross-sectional transmission electron micrograph of twin silicon nanowire MOSFET, (b) measured transfer characteristics of n+ poly gate TSNWFETs [75].

## 1.3 Research Objectives and Thesis Overview

In **Chapter 2** the benefits of thin-BOX FD-SOI technology for 6-T SRAM scaling are investigated. Firstly, three-dimensional atomistic process and device simulations for thin-BOX FD-SOI and planar bulk MOSFET designs for low-operating-power (LOP) applications at the 22 nm node are presented. Then the benefits of transistor performance improvement and  $V_T$  variation reduction offered by FD-SOI technology are assessed via iso-area and iso-yield analysis. Finally, the minimum operating voltage ( $V_{min}$ ) for  $6\sigma$  yield is projected for FD-SOI and planar bulk SRAM cells.

To avoid the need for costly silicon-on-insulator substrates or complex fabrication processes, the quasi-planar (QP) bulk MOSFET design for CMOS scaling to the end of the roadmap was recently proposed [76]. The following four chapters (**Chapters 3 to 6**) theoretically and experimentally investigate the QP bulk device structure, e.g., how best to suppress  $V_T$  variation, to maximize performance, to minimize SRAM  $V_{min}$ , and to enhance SRAM yield.

In **chapter 3**, RDF-induced  $V_T$  variation for the quasi-planar bulk MOSFET vs. the planar bulk MOSFET at the 22 nm node (25 nm gate length) is studied using atomistic three-dimensional device simulation. The impact of body/channel or source/drain doping

profile on  $V_T$  variation is presented. Lastly, a new method of  $V_T$  tuning in the quasi-planar bulk MOSFET is proposed to mitigate the tradeoff between  $V_T$  variation and short-channel effect suppression.

In **chapter 4**, full 3-D 6T-SRAM cell simulations are used to assess the benefits of the quasi-planar bulk MOSFET design for 22 nm SRAM technology. A segmented channel design is proposed to enhance SRAM yield and improve immunity to single-event upsets.

In **chapter 5**, a simple method (*i.e.*, a timed dilute-HF etch for recessing the shallow trench isolation just prior to gate-stack formation) of manufacturing quasi-planar bulk MOSFET structures is experimentally demonstrated in a 28 nm CMOS technology. The benefits of the quasi-planar bulk structure for improving device performance and reducing variation in 6T-SRAM read and write margins are presented. Due to its increased benefits with decreasing channel width, quasi-planar bulk MOSFET technology is a promising solution for future CMOS technology generations (22 nm and beyond).

In **chapter 6**, 3D device simulation with considerations of three main random variation factors (*i.e.*, line-edge-roughness, random dopant fluctuation, and work-function variation) is used to quantitatively show the benefits of the quasi-planar bulk MOSFET (improved performance and reduced  $V_T$  variation) as compared against a planar bulk MOSFET. A compact analytical model is used to quantitatively project the benefits of QP bulk CMOS technology, specifically enhancement of write-ability and write time for comparable read stability, as well as SRAM yield improvement and  $V_{min}$  reduction. Additionally, a notchless quasi-planar bulk SRAM cell design is proposed for improved printability.

In **chapter 7**, the contributions of this dissertation are summarized and suggestions for future research are made.

#### 1.4 References

- [1] G. E. Moore, "Cramming more components onto integrated circuits," *Proc. of the IEEE*, vol. 86, no. 1, pp. 82-85, Jan. 1998.

- [2] International Technology Roadmap for Semiconductors (ITRS). [Online]. Available: <a href="http://public.itrs.net">http://public.itrs.net</a>

- [3] M. J. M. Pelgrom, A. Duinmaijer, and A. Welbers, "Matching properties of MOS transistors," *IEEE J. Solid-State Circuits*, vol. 24, no. 5, pp. 1433–1440, Oct. 1989.

- [4] K. J. Kuhn, "Reducing variation in advanced logic technologies: approaches to process and design for manufacturability of nanoscale CMOS," *IEDM Tech. Dig.*, Dec. 2007, pp. 471–474.

- [5] E. Seevinck, F. J. List, and J. Lohstroh, "Static-noise margin analysis of MOS SRAM cells," *IEEE J. Solid-State Circuits*, vol. 22, no. 5, pp. 748-754, Oct. 1987.

- [6] C. Wann, R. Wong, D. J. Frank, R. Mann, S.-B. Ko, P. Croce, D. Lea, D. Hoyniak, Y.-M. Lee, J. Toomey, M. Weybright, and J. Sudijono, "SRAM cell design for stability methodology," *Proc. IEEE VLSI-TSA*, Apr. 2005, pp. 21–22.

- [7] E. Grossar, M. Stucchi, K. Maex, and W. Dehaene, "Read stability and write-ability analysis of SRAM cells for nanometer technologies," *IEEE J. Solid-State Circuits*, vol. 41, no. 11, pp. 2577–2588, Nov. 2006.

- [8] A. Carlson, Z. Guo, S. Balasubramanian, L.-T. Pang, T.-J. King Liu, and B. Nikolic, "FinFET SRAM with enhanced read/write margins," *IEEE International SOI Conference*, Oct. 2006, pp. 105–106.

- [9] Rashmi, A. Kranti, and G. A. Armstrong, "6-T SRAM cell design with nanoscale double-gate SOI MOSFETs: impact of source/drain engineering and circuit topology," *IOP Semiconductor Science and Technology*, vol. 23, no. 7, pp. 1-13, Jul. 2008.

- [10] R. F. Lyon and R. R. Schediwy, "CMOS static memory with a new four transistor memory cell," *Proc. of Stanford conference on advanced research in VLSI*, pp. 111– 131, 1987.

- [11] K. Noda, K. Matsui, K. Imai, K. Inoue, K. Tokashiki, H. Kawamoto, K. Yoshida, K. Takeda, N. Nakamura, T. Kimura, H. Toyoshima, Y. Koishikawa, S. Maruyama, T. Saitoh, and T. Tanigawa, "A 1.9-μm² loadless CMOS four-transistor SRAM cell in a 0.18-μm logic technology," *IEDM Tech. Dig.*, Dec. 1998, pp. 643–646.

- [12] N. Lindert, Y.-K. Choi, L. Chang, E. Anderson, W. Lee, T.-J. King, J. Bokor, and C. Hu, "Quasi-planar NMOS FinFETs with sub-100 nm gate lengths," *IEEE Device Research Conference*, Jun. 2001, pp. 26–27.

- [13] O. Semenov, A. Pavlov, and M. Sachdev, "Sub-quarter micron SRAM cells stability in low-voltage operation: a comparative analysis," *IEEE International Reliability Workshop*, Oct. 2002, pp. 168–171.

- [14] Z. Guo, S. Balasubramanian, R. Zlatanovici, T.-J. King, and B. Nikolic, "FinFET-based SRAM design," *IEEE International Symposium on Low Power Electronics and Design*, Aug. 2005, pp. 2–7.

- [15] B. Giraud, A. Amara, and A. Vladimirescu, "A comparative study of 6T and 4T SRAM cells in double gate CMOS with statistical variation," *IEEE International Symposium on Circuits and Systems*, May 2007, pp. 3022–3025.

- [16] K. Takeda, Y. Hagihara, Y. Aimoto, M. Nomura, Y. Nakazawa, T. Ishii, and H. Kobatake, "A Read-Static-Noise-Margin-Free SRAM cell for low-V<sub>DD</sub> and high-speed applications," *ISSCC Dig. of Tech. Papers*, Feb. 2005, pp. 478-479.

- [17] K. Takeda, Y. Hagihara, Y. Aimoto, M. Nomura, Y. Nakazawa, T. Ishii, and H. Kobatake, "A Read-Static-Noise-Margin-Free SRAM cell for low-V<sub>DD</sub> and high-speed applications," *IEEE J. Solid-State Circuits*, vol. 41, no. 1, pp. 113–121, Jan. 2006.

- [18] R. Joshi, R. Houle, K. Batson, D. Rodko, P. Patel, W. Huott, R. Franch, Y. Chan, D. Plass, S. Wilson, and P. Wang "6.6+ GHz low Vmin, read and half select disturb-free 1.2 Mb SRAM," *VLSI Symp. Circuit Dig.*, Jun. 2007, pp. 250-251.

- [19] L. Chang, Y. Nakamurat, R. K. Montoye, J. Sawada, A. K. Martin, K. Kinoshitat, F. H. Gebara, K. B. Agarwalt, D. J. Acharyya, W. Haensch, K. Hosokawat, and D. Jamsek, "A 5.3GHz 8-T SRAM with operation down to 0.41V in 65nm CMOS," *VLSI Symp. Circuit Dig.*, Jun. 2007, pp. 252-253.

- [20] S. Ishikura, M. Kurumada, T. Terano, Y. Yamagami, N. Kotani, K. Satomi, K. Nii, M. Yabuuchi, Y. Tsukamoto, S. Ohbayashi, T. Oashi, H. Makino, H. Shinohara, and H. Akamatsu, "A 45nm 2 port 8T-SRAM using hierarchical replica bitline technique with immunity from simultaneous R/W access issues," VLSI Symp. Circuit Dig., Jun. 2007, pp. 254-255.

- [21] Y. Morita, H. Fujiwara, H. Noguchi, Y. Iguchi, K. Nii, H. Kawaguchi, and M. Yoshimoto, "An area-conscious low-voltage-oriented 8T-SRAM design under DVS environment," *VLSI Symp. Circuit Dig.*, Jun. 2007, pp. 256-257.

- [22] I. J. Chang, J.-J. Kim, S. P. Park, K. Roy "A 32kb 10T subthreshold SRAM array with bit-interleaving and differential read scheme in 90nm CMOS," *ISSCC Dig. of Tech. Papers*, Feb. 2008, pp. 388-389.

- [23] A. Asenov, "Simulation of statistical variability in nano MOSFETs," *VLSI Symp. Tech. Dig.*, Jun. 2007, pp. 86-87.

- [24] A. Asenov, "Random dopant induced threshold voltage lowering and fluctuations in sub 50 nm MOSFETs: a statistical 3D 'atomistic' simulation study," *IOP Semiconductor Science and Technology*, vol. 10, no. 2, pp. 153-158, Feb. 1999.

- [25] R. W. Keyes, "Physical limits in digital electronics," *Proc. of the IEEE*, vol. 63, no. 5, pp. 740-767, May 1975.

- [26] T. Mizuno, J.-I. Okamura, and A. Toriumi, "Experimental study of threshold voltage fluctuation due to statistical variation of channel dopant number in MOSFETs," *IEEE Trans. Electron Devices*, vol. 41, no. 11, pp. 2216-2221, Nov. 1994.

- [27] A. Asenov and S. Saini, "Suppression of random dopant-induced threshold voltage fluctuations in sub-0.1-μm MOSFET's with epitaxial and δ-doped channels," *IEEE Trans. Electron Devices*, vol. 46, no. 8, pp. 1718-1724, Aug. 1999.

- [28] A. Cathignol, B. Cheng, D. Chanemougame, A. R. Brown, K. Rochereau, G. Ghibaudo, and A. Asenov, "Quantitative evaluation of statistical variability sources in a 45-nm technological node LP N-MOSFET," *IEEE Electron Device Lett.*, vol. 29, no. 6, pp. 609-611, Jun. 2008.

- [29] D. Reid, C. Millar, G. Roy, S. Roy, and A. Asenov, "Analysis of threshold voltage distribution due to random dopants: A 100 000-sample 3-D simulation study," *IEEE Trans. Electron Devices*, vol. 56, no. 10, pp. 2255-2263, Oct. 2009.

- [30] T. Ohtou, N. Sugii, and T. Hiramoto, "Impact of parameter variations and random dopant fluctuations on short-channel fully depleted SOI MOSFETs with extremely thin BOX," *IEEE Electron Device Lett.*, vol. 28, no. 8, pp. 740–742, Aug. 2007.

- [31] M. Hane, T. Ikezawa, and T. Ezaki, "Coupled atomistic 3D process/device simulation considering both line-edge roughness and random-discrete-dopant effects," *IEEE International conference on simulation of semiconductor processes and devices* (SISPAD), Sep. 2003, pp. 99-102.

- [32] T. Yoshimura, H. Shiraishi, J. Yamamoto, and S. Okazaki, "Nanoedge roughness in polymer resist patterns," Appl. Phys. Lett., vol. 63, no. 6, pp. 764–766, Aug. 1993.

- [33] T. Yamaguchi, K. Yamazaki, M. Nagase, and H. Namatsu, "Line-edge roughness: characterization and material origin," *Jpn. J. Appl. Phys.*, vol. 42, no. 6B, pp. 3755–3762, Jun. 2003.

- [34] X. Sun and T.-J. King Liu, "Spacer gate lithography for reduced variability due to line edge roughness," *IEEE Trans. Semiconductor Manufacturing*, vol. 23, no. 2, pp. 311-315, May 2010.

- [35] Y.-K. Choi, T.-J. King, and C. Hu, "A spacer patterning technology for nanoscale CMOS," *IEEE Trans. Electron Devices*, vol. 49, no. 3, pp. 436–441, Mar. 2002.

- [36] H. F. Dadgour, K. Endo, V. K. De, and K. Banerjee, "Grain-orientation induced work function variation in nanoscale metal-gate transistors—part I: modeling, analysis, and experimental validation," *IEEE Trans. Electron Devices*, vol. 57, no. 10, pp. 2504–2514, Oct. 2010.

- [37] H. F. Dadgour, K. Endo, V. K. De, and K. Banerjee, "Grain-orientation induced work function variation in nanoscale metal-gate transistors—part II: implications for process, device, and circuit design," *IEEE Trans. Electron Devices*, vol. 57, no. 10, pp. 2515–2525, Oct. 2010.

- [38] H. Pilo, J. Barwin, G. Braceras, C. Browning, S. Burns, J. Gabric, S. Lamphier, M. Miller, A. Roberts, and F. Towler, "An SRAM design in 65nm and 45nm technology nodes featuring read and write-assist circuits to expand operating voltage," *VLSI Symp. Circuit Dig.*, Jun. 2006, pp. 15-16.

- [39] K. Zhang, U. Bhattacharya, Z. Chen, F. Hamzaoglu, D. Murray, N. Vallepalli, Y. Wang, B. Zheng, and M. Bohr, "A 3 GHz 70Mb SRAM in 65nm CMOS technology with integrated column-based dynamic power supply," *ISSCC Dig. of Tech. Papers*, Feb. 2005, pp. 474-475.

- [40] K. Mistry, C. Allen, C. Auth, B. Beattie, D. Bergstrom, M. Bost, M. Brazier, M. Buehler, A. Cappellani, R. Chau, C.-H. Choi, G. Ding, K. Fischer, T. Ghani, R. Grover, W. Han, D. Hanken, M. Hattendorf, J. He, J. Hicks, R. Huessner, D. Ingerly, P. Jain, R. James, L. Jong, S. Joshi, C. Kenyon, K. Kuhn, K. Lee, H. Liu, J. Maiz, B. McIntyre, P. Moon, J. Neirynck, S. Pae, C. Parker, D. Parsons, C. Prasad, L. Pipes, M. Prince, P. Ranade, T. Reynolds, J. Sandford, L. Shifren, J. Sebastian, J. Seiple, D. Simon, S. Sivakumar, P. Smith, C. Thomas, T. Troeger, P. Vandervoorn, S. Williams, and K. Zawadzki, "A 45nm logic technology with high-k + metal gate transistors, strained silicon, 9 Cu interconnect layers, 193nm dry patterning, and 100% Pb-free packaging," *IEDM Tech. Dig.*, Dec. 2007, pp. 247–250.

- [41] C. Auth, A. Cappellani, J.-S. Chun, A. Dalis, A. Davis, T. Ghani, G. Glass, T. Glassman, M. Harper, M. Hattendorf, P. Hentges, S. Jaloviar, S. Joshi, J. Klaus, K. Kuhn, D. Lavric, M. Lu, H. Mariappan, K. Mistry, B. Norris, N. Rahhal-orabi, P. Ranade, J. Sandford, L. Shifren, V. Souw, K. Tone, F. Tambwe, A. Thompson, D. Towner, T. Troeger, P. Vandervoorn, C. Wallace, J. Wiedemer, and C. Wiegand, "45nm high-k + metal gate strain-enhanced transistors," *VLSI Symp. Tech. Dig.*, Jun. 2008, pp. 128-129.

- [42] O. Weber, O. Faynot, F. Andrieu, C. Buj-Dufournet, F. Allain, P. Scheiblin, J. Foucher, N. Daval, D. Lafond, L. Tosti, L. Brevard, O. Rozeau, C. Fenouillet-Beranger, M. Marin, F. Boeuf, D. Delprat, K. Bourdelle, B.-Y. Nguyen, and S. Deleonibus, "High immunity to threshold voltage variability in undoped ultra-thin FDSOI MOSFETs and its physical understanding," *IEDM Tech. Dig.*, Dec. 2008, pp. 1–4.

- [43] S. Narasimha, K. Onishi, H. M. Nayfeh, A. Waite, M. Weybright, J. Johnson, C. Fonseca, D. Corliss, C. Robinson, M. Crouse, D. Yang, C-H. J. Wu, A. Gabor, T. Adam, I. Ahsan, M. Belyansky, L. Black, S. Butt, J. Cheng, A. Chou, G. Costrini, C. Dimitrakopoulos, A. Domenicucci, P. Fisher, A. Frye, S. Gates, S. Greco, S. Grunow, M. Hargrove, J. Holt, S-J. Jeng, M. Kelling, B. Kim, W. Landers, G. Larosa, D. Lea, M.H. Lee, X. Liu, N. Lustig, A. McKnight, L. Nicholson, D. Nielsen, K. Nummy, V. Ontalus, C. Ouyang, X. Ouyang, C. Prindle, R. Pal, W. Rausch, D. Restaino, C. Sheraw, J. Sim, A. Simon, T. Standaert, C.Y. Sung, K. Tabakman, C. Tian, R. Van Den Nieuwenhuizen, H. Van Meer, A. Vayshenker, D. Wehella-Gamage, J. Werking, R. C. Wong, J. Yu, S. Wu, R. Augur, D. Brown, X. Chen, D. Edelstein, A. Grill, M. Khare, Y. Li, S. Luning, J. Norum, S. Sankaran, D. Schepis, R. Wachnik, R. Wise, C. Wann, T. Ivers, and P. Agnello, "High performance 45-nm SOI technology with enhanced strain, porous low-k BEOL, and immersion lithography," *IEDM Tech. Dig.*, Dec. 2006, pp. 1–4.

- [44] K. Cheng, A. Khakifirooz, P. Kulkarni, S. Kanakasabapathy, S. Schmitz, A. Reznicek, T. Adam, Y. Zhu, J. Li, J. Faltermeier, T. Furukawa, L. F. Edge, B. Haran, S.-C. Seo, P. Jamison, J. Holt, X. Li, R. Loesing, Z. Zhu, R. Johnson, A. Upham, T. Levin, M. Smalley, J. Herman, M. Di, J.Wang, D. Sadana, P. Kozlowski, H. Bu, B. Doris, and J. O'Neill, "Fully depleted extremely thin SOI technology fabricated by a novel integration scheme featuring implant-free, zero-silicon-loss, and faceted raised source/drain," *VLSI Symp. Tech. Dig.*, Jun. 2009, pp. 212–213.

- [45] M. Chudzik, B. Doris, R. Mo, J. Sleight, E. Cartier, C. Dewan, D. Park, H. Bu, W. Natzle, W. Yan, C. Ouyang, K. Henson, D. Boyd, S. Callegari, R. Carter, D. Casarotto, M. Gribelyuk, M. Hargrove, W. He, Y. Kim, B. Linder, N. Moumen, V.K. Paruchuri, J. Stathis, M. Steen, A. Vayshenker, X. Wang, S. Zafar, T. Ando, R. Iijima, M. Takayanagi, V. Narayanan, R. Wise, Y. Zhang, R. Divakaruni, M.Khare, and T.C. Chen, "High-performance high-k/metal gates for 45nm CMOS and beyond with gate-first processing," VLSI Symp. Tech. Dig., Jun. 2007, pp. 194–195.

- [46] S. Narasimha, K. Onishi, H. M. Nayfeh, A. Waite, M. Weybright, J. Johnson, C. Fonseca, D. Corliss, C. Robinson, M. Crouse, D. Yang, C-H. J. Wu, A. Gabor, T. Adam, I. Ahsan, M. Belyansky, L. Black, S. Butt, J. Cheng, A. Chou, G. Costrini, C. Dimitrakopoulos, A. Domenicucci, P. Fisher, A. Frye, S. Gates, S. Greco, S. Grunow, M. Hargrove, J. Holt, S-J. Jeng, M. Kelling, B. Kim, W. Landers, G. Larosa, D. Lea, M.H. Lee, X. Liu, N. Lustig, A. McKnight, L. Nicholson, D. Nielsen, K. Nummy, V. Ontalus, C. Ouyang, X. Ouyang, C. Prindle, R. Pal, W. Rausch, D. Restaino, C. Sheraw, J. Sim, A. Simon, T. Standaert, C.Y. Sung, K. Tabakman, C. Tian, R. Van Den Nieuwenhuizen, H. Van Meer, A. Vayshenker, D. Wehella-Gamage, J. Werking, R. C. Wong, J. Yu, S. Wu, R. Augur, D. Brown, X. Chen, D. Edelstein, A. Grill, M. Khare, Y. Li, S. Luning, J. Norum, S. Sankaran, D. Schepis, R. Wachnik, R. Wise, C. Wann, T. Ivers, P. Agnello, "High performance 45-nm SOI technology with enhanced strain, porous low-k BEOL, and immersion lithography," *IEDM Tech. Dig.*, Dec. 2006, pp. 1–4.

- [47] D. Suh and J. G. Fossum, "Dynamic floating-body instabilities in partially depleted SOI CMOS circuits," *IEDM Tech. Dig.*, Dec. 1994, pp. 661–664.

- [48] P.-F. Lu, C.-T. Chuang, J. Ji, L. F. Wagner, C.-M. Hsieh, J. B. Kuang, L. L.-C. Hsu, M. M. Pelella, S.-F. S. Chu, and C. J. Anderson, "Floating-body effects in partially depleted SOI CMOS circuits," *IEEE J. Solid-State Circuits*, vol. 32, no. 8, pp. 1241–1253, Aug. 1997.

- [49] C.-T. Chuang, P.-F. LU, and C. J. Anderson, "SOI for digital CMOS VLSI: design considerations and advances," *Proc. of the IEEE*, vol. 86, no. 4, pp. 689-720, Apr. 1998.

- [50] SOI Industry Consortium [Online]. Available: <a href="http://www.soiconsortium.org">http://www.soiconsortium.org</a>

- [51] Y.-K. Choi, K. Asano, N. Lindert, V. Subramanian, T.-J. King, J. Bokor, and C. Hu, "Ultra-thin body SOI MOSFET for deep-sub-tenth micron era," *IEDM Tech. Dig.*, Dec. 1999, pp. 919–921.

- [52] K. Cheng, A. Khakifirooz, P. Kulkarni, S. Ponoth, J. Kuss, D. Shahrjerdi, L. F. Edge, A. Kimball, S. Kanakasabapathy, K. Xiu, S. Schmitz, A. Reznicek, T. Adam, H. He, N. Loubet, S. Holmes, S. Mehta, D. Yang, A. Upham, S.-C. Seo, J. L. Herman, R. Johnson, Y. Zhu, P. Jamison, B. S. Haran, Z. Zhu, L. H. Vanamurth, S. Fan, D. Horak, H. Bu, P. J. Oldiges, D. K. Sadana, P. Kozlowski, D. McHerron, J. O'Neill, B. Doris, "Extremely thin SOI (ETSOI) CMOS with record low variability for low power system-on-chip applications," *IEDM Tech. Dig.*, Dec. 2009, pp. 1-4.

- [53] C. L. Chen, R.T. Chang, P.W. Wyatt, C. K. Chen, D.-R. Yost, J. M. Knecht, and C. L. Keast, "Floating body effects on the RF performance of FDSOI RF amplifiers," *IEEE International SOI Conference*, Oct. 2005, pp. 44-46.