# Thin-Body SOI Capacitorless DRAM Cell Design Optimization and Scaling

MIN CHO

## Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2012-176 http://www.eecs.berkeley.edu/Pubs/TechRpts/2012/EECS-2012-176.html

July 13, 2012

Copyright © 2012, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## Acknowledgement

I would like to offer my deepest thanks to my academic advisor, Professor Tsu-Jae King Liu, whose unflinching intellect guided my research and writing from start to finish. I am equally grateful to Professors Ming C. Wu, Junqiao Wu, Nathan W. Cheung, and Vivek Subramanian. Furthermore, I would like to thank Dr. Siwoo Lee, Professor Changhwan Shin. I would like to thank several former, current students, and all the members of the UC Berkeley who gave me valuable feedback. I owe a great deal of thanks to Samsung Electronics (colleagues and supervisors) for their financial support. Finally I owe my gracious thanks to my family. In particular, I want to acknowledge my lovely spouse, Ji Hye Yi, and our adorable sons HyunSung Cho and HyunSoo Cho.

### Thin-Body SOI Capacitorless DRAM Cell Design Optimization and Scaling

By

Min Hee Cho

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Tsu-Jae King Liu, Chair Professor Ming C. Wu Professor Junqiao Wu

Fall 2012

# Thin-Body SOI Capacitorless DRAM Cell Design Optimization and Scaling

Copyright © 2012

by

Min Hee Cho

#### Abstract

# Thin-Body SOI Capacitorless DRAM Cell Design Optimization and Scaling by

#### Min Hee Cho

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

### University of California, Berkeley

Professor Tsu-Jae King Liu, Chair

Capacitorless dynamic random access memory (DRAM) is a promising solution to cellarea scalability and complex fabrication process issues for conventional DRAM. The thin body SOI transistor, which suppresses the short channel effect and also minimizes variability, is selected for the capacitorless DRAM cell structure. The impact of substrate doping concentration on capacitorless DRAM cell performance is studied and a novel selective well structure is proposed.

A capacitorless DRAM cell design with BJT-based operation (BJT mode) is known to have larger sensing margins and longer retention times. Controlling band-to-band tunneling leakage (BTBT) related to the electric field plays a key role in limiting retention time. In the BJT mode, BTBT in the Hold 0 state limits data retention time (D0 failure). By optimizing the underlap between the front gate and the source/drain regions as well as the operating voltages, retention time exceeding 1 second should be attainable for a cell with 25 nm gate length. The scaling limits of optimized capacitorless DRAM cells are also investigated through the analysis of variations. Signal sense margin analysis indicates that the ultimate scaling limit is 13 nm (gate length) for embedded DRAM applications and 16.5 nm for stand-alone DRAM applications.

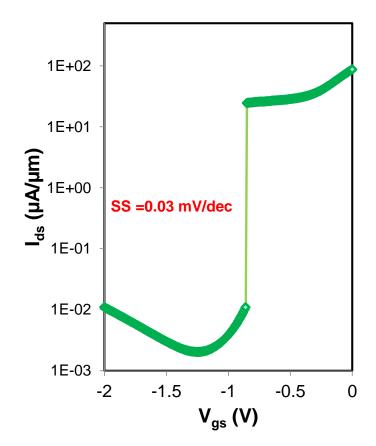

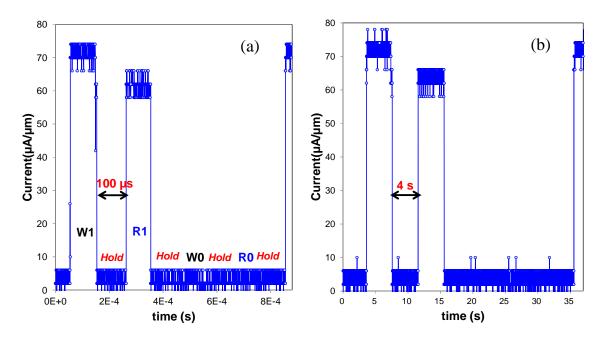

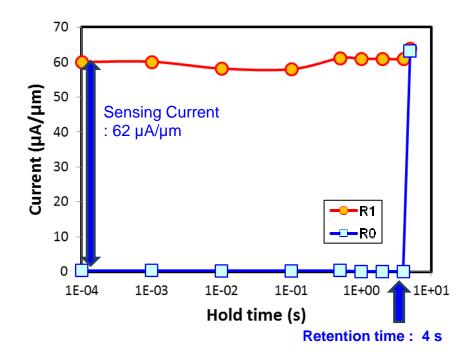

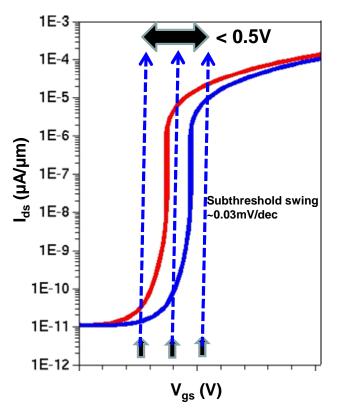

The positive feedback MOSFET (PF-FET) was fabricated on thin body (10 nm) and UTBOX (10 nm) SOI structure. Positive feedback occurs as a result of both the BJT operation and the floating body effect from weak impact ionization. It exhibits very steep subthreshold slope of 0.03 mV/dec. Wide hysteresis enables the PF-FET to be utilized for memory application. The sensing margin is  $62 \,\mu A/\mu m$  and retention time is greater than 4 seconds.

To my family for their unbounded love and encouragement, to my sons for their great pleasure to me, and to my wife, JiHye, for her devoted love and support.

# Contents

| Table of Contents | ii  |

|-------------------|-----|

| List of Figures   | vii |

| List of Tables    | Х   |

| Acknowledgements  | xi  |

# **Table of Contents**

| Chapter 1: Introduction1                         |

|--------------------------------------------------|

| 1.1 Dynamic Random Access Memory (DRAM)1         |

| 1.1.1 Conventional DRAM and Limitation1          |

| 1.1.2 Operating Principles of Capacitorless DRAM |

| 1.2 Structure Design and Simulation Models7      |

| 1.2.1 Thin Film SOI with UTBOX7                  |

| 1.2.2 Simulation Methodology10                   |

| 1.2.3 Random Dopant Fluctuations (RDF)12         |

| 1.3 Dissertation Outline                         |

| 1.4 | References |  | 1 | 4 |

|-----|------------|--|---|---|

|-----|------------|--|---|---|

#

| 2.1 Introduction                         |

|------------------------------------------|

| 2.2 Device Structure and Operation       |

| 2.3 Optimization of Substrate Doping     |

| 2.3.1 Simulation Approach18              |

| 2.3.2 Substrate Doping Effect            |

| 2.3.3 Random Dopant Fluctuations (RDF)20 |

| 2.4 Selective Well Design                |

| 2.5 Summary24                            |

| 2.6 References                           |

| Chapter 3: Design Optimization of BJT-based Thin-Body Capacitorless |    |  |

|---------------------------------------------------------------------|----|--|

| DRAM Cell                                                           |    |  |

| 3.1 Introduction                                                    |    |  |

| 3.2 Cell Design and TCAD Simulation                                 | 27 |  |

| 3.3 Mechanism of Data Retention Failure  |    |

|------------------------------------------|----|

| 3.4 Methods for Improving Retention Time |    |

| 3.5 Impact of Random Dopant Fluctuations |    |

| 3.6 Summary                              | 40 |

| 3.7 References                           | 41 |

| Chapter 4: Implications of Variation | 43 |

|--------------------------------------|----|

| 4.1 Introduction                     | 43 |

| 4.2 Device Structure and Operation   | 43 |

| 4.3 Sources of Variation             | 44 |

| 4.4 RDF effect                       | 45 |

| 4.5 Dimension Variation Effects      | 46 |

| 4.6 Summary                          | 49 |

| 4.7 References                       | 50 |

| Chapter 5: Variation-Awar   | e Study with Scaling Limit | 52 |

|-----------------------------|----------------------------|----|

| 5.1 Introduction            |                            |    |

| 5.2 Body Thickness Limitati | on                         | 54 |

| 5.2.1 Reference Cell (25 nm Gate length) Design54    |

|------------------------------------------------------|

| 5.2.2 Body Thickness Scaling54                       |

| 5.3 Design Optimization of Scaled Cells              |

| 5.3.1 Scaling Constraints                            |

| 5.3.2 Optimization of Cell Operating Voltages        |

| 5.4 Scaling Limitation in Terms of Variation Factors |

| 5.4.1 Variation Factors                              |

| 5.4.2 Dimension Variation Effects with Scaling       |

| 5.5 Summary70                                        |

| 5.6 References                                       |

| Chapter 6: Positive Feedback SOI Transistor and Its Capacitorless<br>DRAM Application | 74 |

|---------------------------------------------------------------------------------------|----|

| 6.1 Introduction                                                                      | 74 |

| 6.2 Principles                                                                        | 75 |

| 6.3 Positive Feedback Modeling & Properties                                           | 76 |

| 6.3.1 Simulation Modeling                                                             | 76 |

| 6.3.2 Simulated Structure                                                             | 77 |

| 6.3.3 Positive Feedback Characteristics       |

|-----------------------------------------------|

| 6.4 Device Structure and Fabrication          |

| 6.5 Measurement Configuration                 |

| 6.6 Experimental I-V Characteristics          |

| 6.7 Capacitorless DRAM Application91          |

| 6.8 Summary94                                 |

| 6.9 References                                |

|                                               |

| Chapter 7: Conclusion                         |

| Chapter 7: Conclusion                         |

|                                               |

| 7.1 Summary and Conclusion                    |

| <ul> <li>7.1 Summary and Conclusion</li></ul> |

| <ul> <li>7.1 Summary and Conclusion</li></ul> |

| <ul> <li>7.1 Summary and Conclusion</li></ul> |

# **List of Figures**

| 1.1 DRAM in semiconductor industry                                                  | 2  |

|-------------------------------------------------------------------------------------|----|

| 1.2 Conventional 1T1C DRAM structure                                                | 2  |

| 1.3 A/R of storage node                                                             | 3  |

| 1.4 Typical capacitorless DRAM                                                      | 4  |

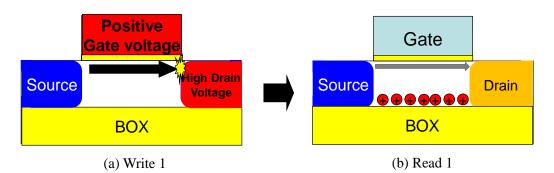

| 1.5 Capacitorless DRAM operation (MOSFET mode)                                      | 4  |

| 1.6 Ids-Vgs curve of Capacitorless DRAM (MOSFET mode)                               | 5  |

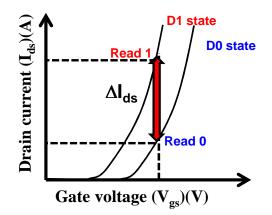

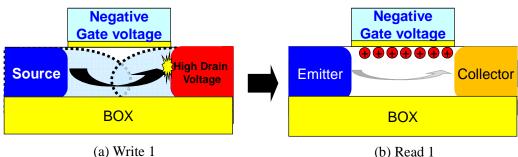

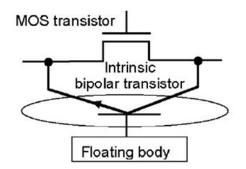

| 1.7 Capacitorless DRAM operation (BJT mode)                                         | 6  |

| 1.8 BJT mode schematic                                                              | 6  |

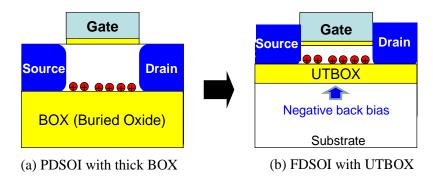

| 1.9 Cross section view of PDSOI transistor and FDSOI transistor                     | 8  |

| 1.10 Characteristics of PDSOI and FDSOI                                             | 8  |

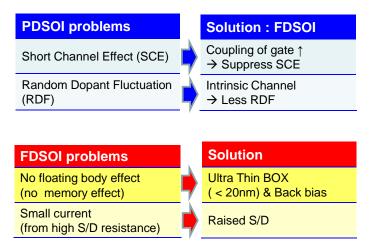

| 1.11 Thin film SOI (TEM and Cross-sectional view)                                   | 9  |

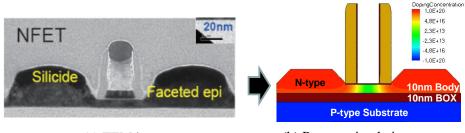

| 1.12 Thin film SOI transistor process flow                                          | 9  |

| 1.13 Randomly distributed dopants in an N-MOSFET                                    | 12 |

| 2.1 Simulated Read 1 and Read 0 currents for a FDSOI capacitorless DRAM cell        | 18 |

| 2.2 Hole density profile                                                            | 19 |

| 2.3 Maximum band-to-band tunneling rate vs. peak electric field                     | 20 |

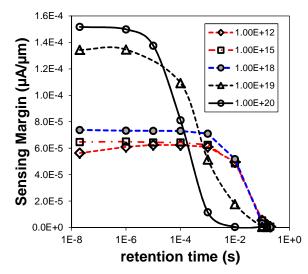

| 2.4 Retention characteristics for a FDSOI capacitorless DRAM cell                   | 20 |

| 2.5 Kinetic Monte Carlo (KMC) simulation                                            | 21 |

| 2.6 Standard deviation of threshold voltage distribution                            | 21 |

| 2.7 Selective well cross section view                                               | 22 |

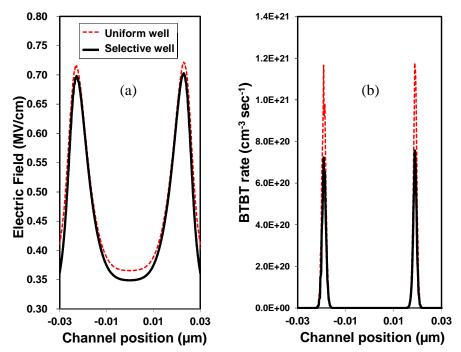

| 2.8a Electric field profile within the SOI film                                     | 23 |

| 2.8b BTBT rate within the SOI film                                                  | 23 |

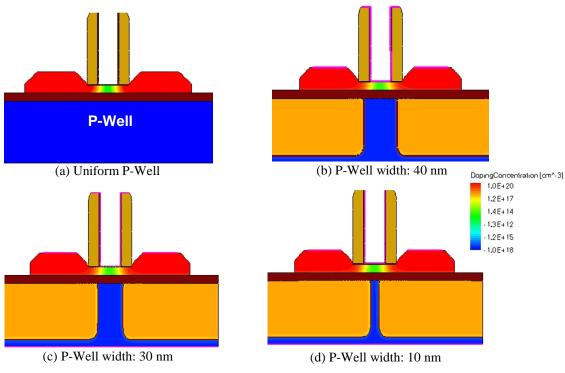

| 2.9 Various p-well widths for selective wells                                       | 23 |

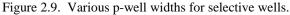

| 2.10 Comparison of retention time for various widths of the p-well                  | 24 |

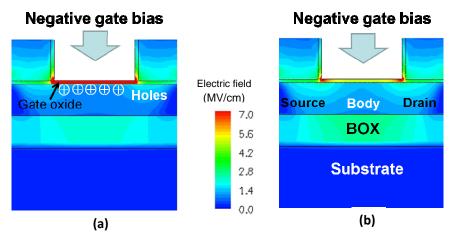

| 3.1 Electric field contour maps for a BJT mode cell in the Hold state               | 29 |

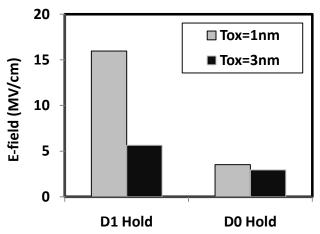

| 3.2 Maximum electric field in the gate oxide during a Hold operation                | 29 |

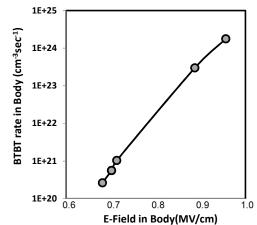

| 3.3 Relationship between electric field and BTBT                                    | 30 |

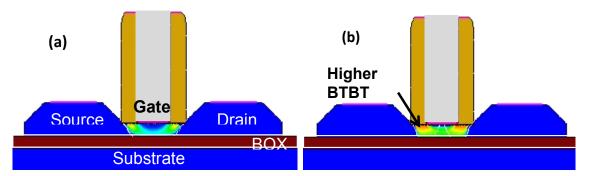

| 3.4 Band-to-band tunneling rate contour maps                                        | 30 |

| 3.5 Energy band diagrams of D1 Hold state and D0 Hold state                         | 31 |

| 3.6 Read current vs. hold duration                                                  | 31 |

| 3.7 Electric field profile within the body                                          | 32 |

| 3.8 Read current vs. hold duration for various values of gate-sidewall spacer width | 33 |

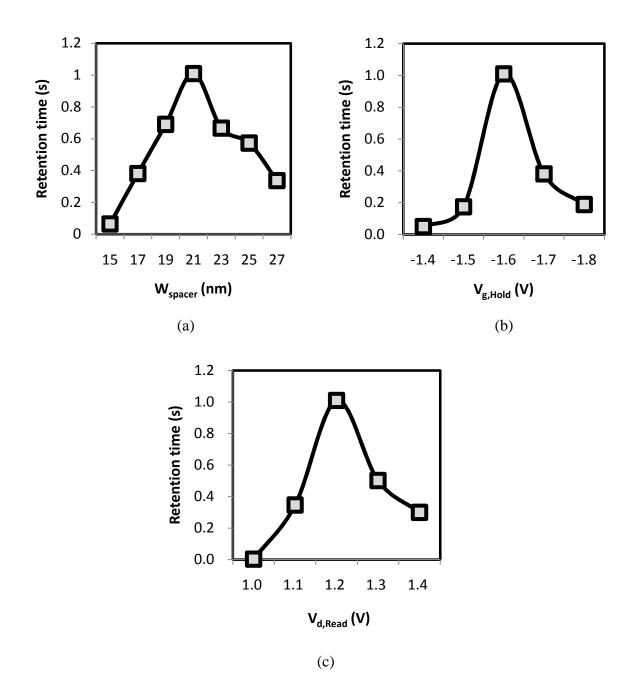

| 3.9a Retention time vs. spacer width                                              | 34    |

|-----------------------------------------------------------------------------------|-------|

| 3.9b Retention time vs. front-gate bias during Hold operation                     | 34    |

| 3.9c Retention time vs. drain bias during Read operation                          | 34    |

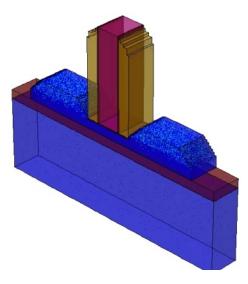

| 3.10 3-dimensional view of a capacitorless DRAM cell                              | 35    |

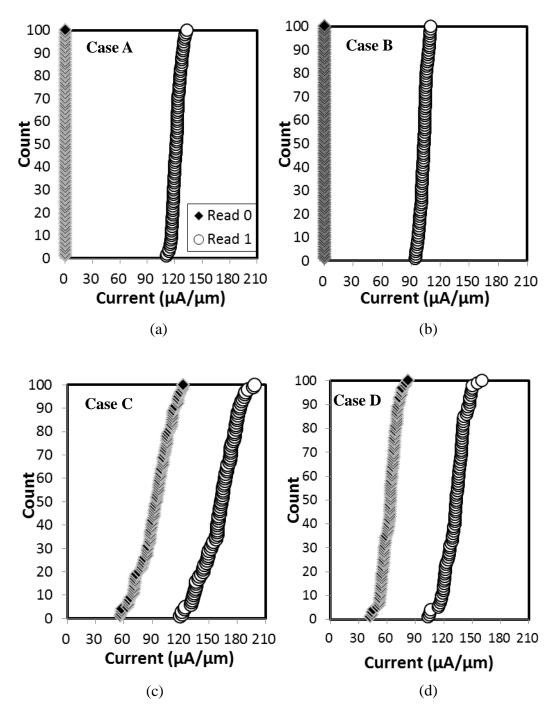

| 3.11 Capacitorless DRAM cell designs used for KMC simulations                     | 36    |

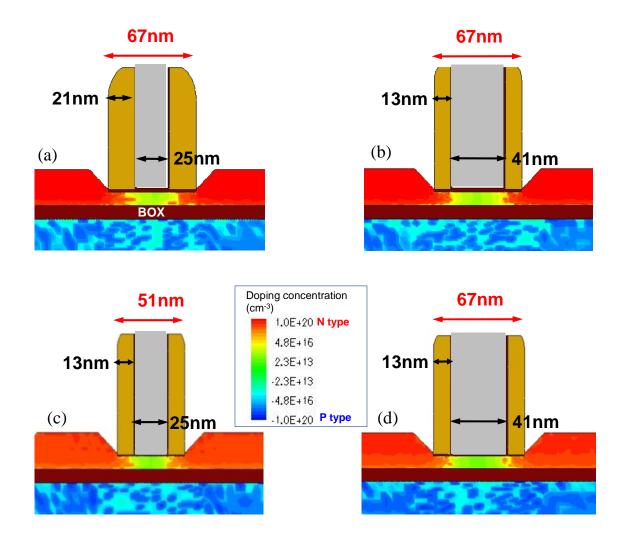

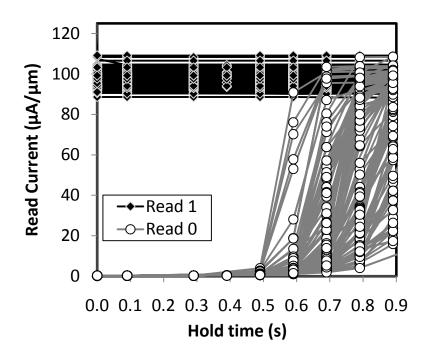

| 3.12 Read 1 and Read 0 current distributions at 1µs Hold duration                 | 37    |

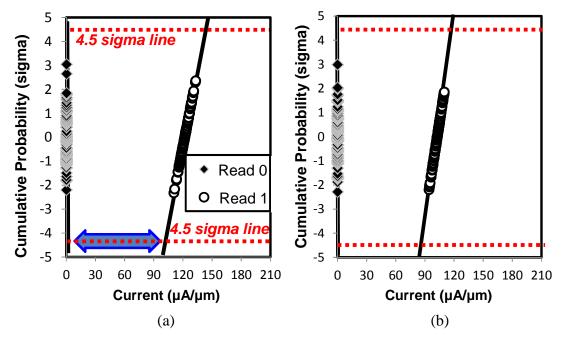

| 3.13 Normal probability plots for Read 1 and Read 0 currents                      | 38-39 |

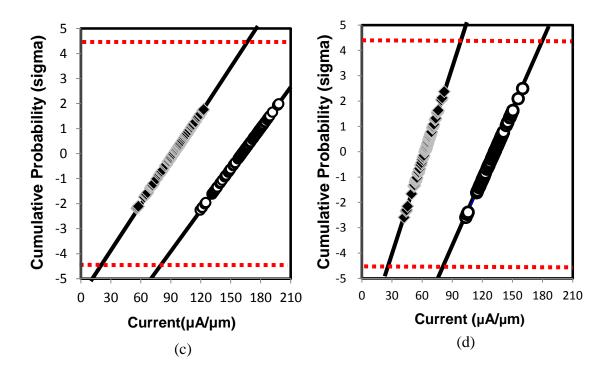

| 3.14 Comparison of retention characteristics                                      | 39    |

| 4.1 Doping contour map showing variation Factors                                  | 44    |

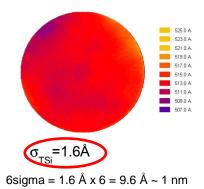

| 4.2 Measured SOI film thickness across a wafer                                    | 45    |

| 4.3 Simulated retention characteristics showing the impact of RDF                 | 46    |

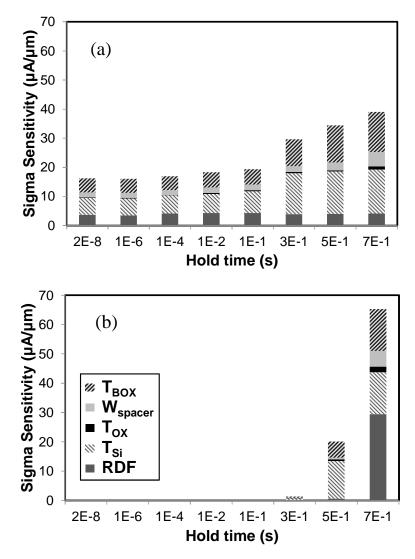

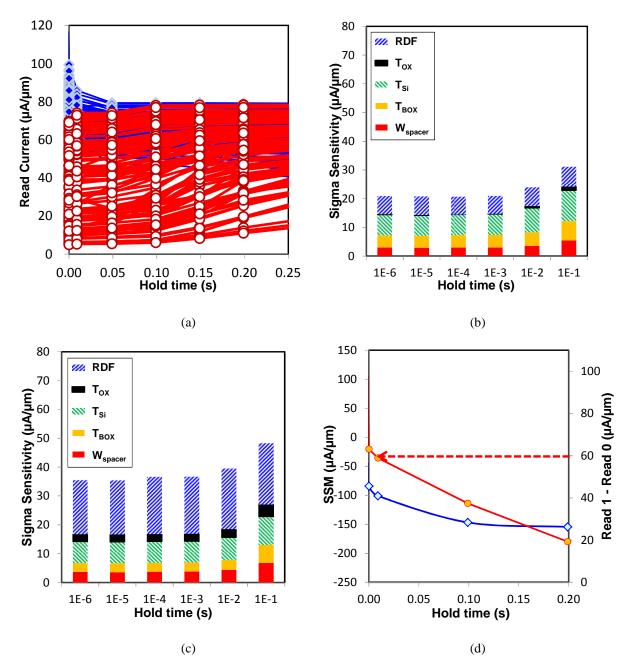

| 4.4 Sigma sensitivity plots for capacitorless DRAM read current                   | 47    |

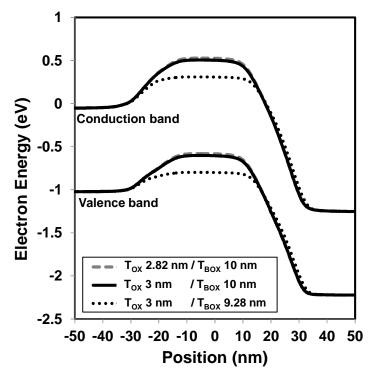

| 4.5 Band diagrams 1nm below gate oxide at the Read 0 state                        | 48    |

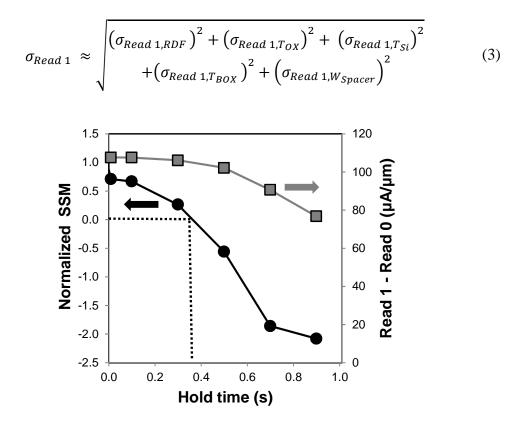

| 4.6 Signal sense margin (SSM) and median sensing current                          | 49    |

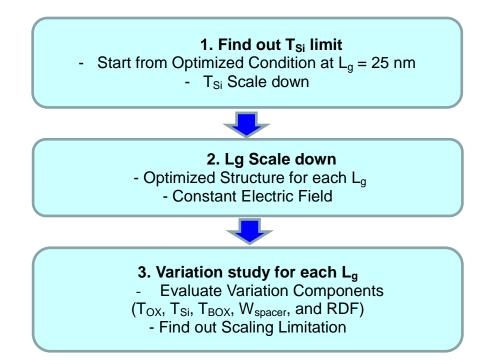

| 5.1 Process for determining scaling limit of the BJT mode capacitorless DRAM cell | 53    |

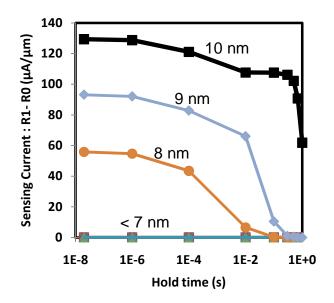

| 5.2 Retention characteristics for each body thickness                             | 55    |

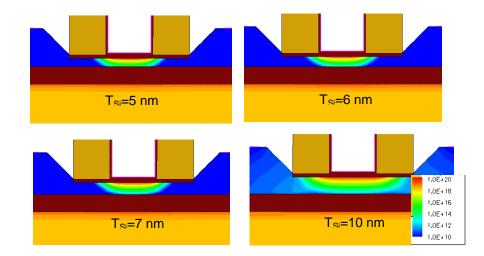

| 5.3 Cross sectional view of contour plots for hole density                        | 55    |

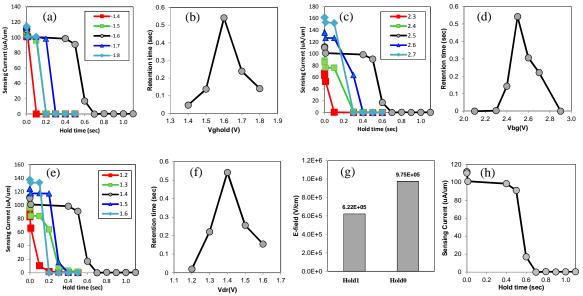

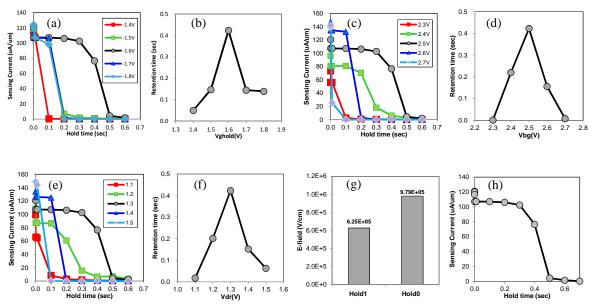

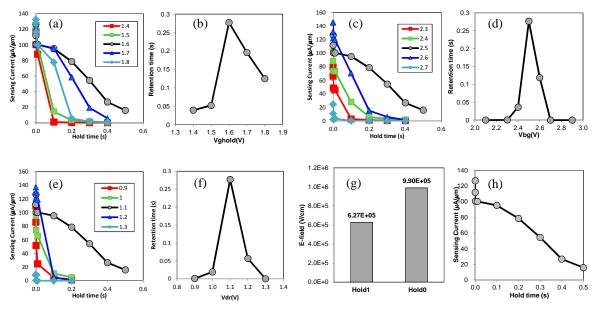

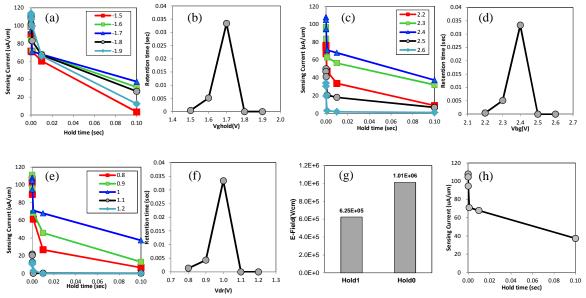

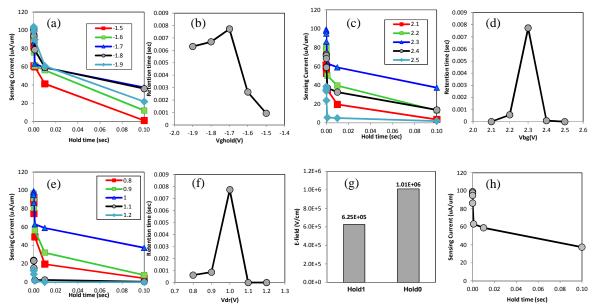

| 5.4 Optimization for $L_g=25$ nm                                                  | 57    |

| 5.5 Optimization for $L_g=20$ nm                                                  | 57    |

| 5.6 Optimization for $L_g=15$ nm                                                  | 58    |

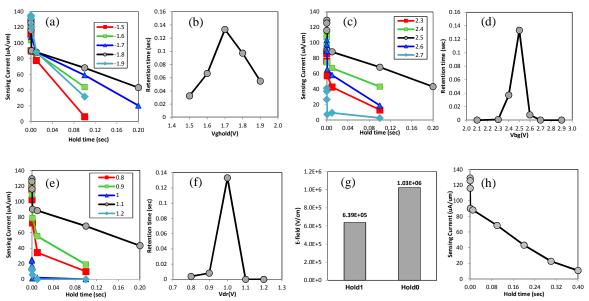

| 5.7 Optimization for $L_g=12$ nm                                                  | 58    |

| 5.8 Optimization for $L_g=10$ nm                                                  | 59    |

| 5.9 Optimization for $L_g=9$ nm                                                   | 59    |

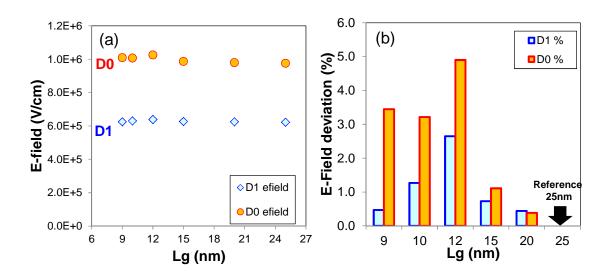

| 5.10 Electric field for optimized operating voltages for each gate length         | 60    |

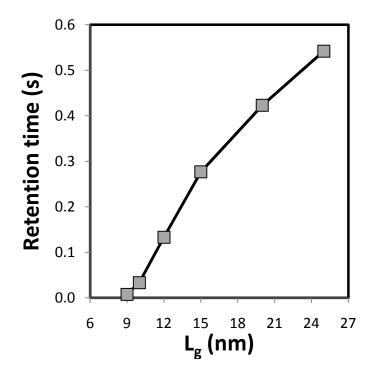

| 5.11 Median retention time with gate length                                       | 61    |

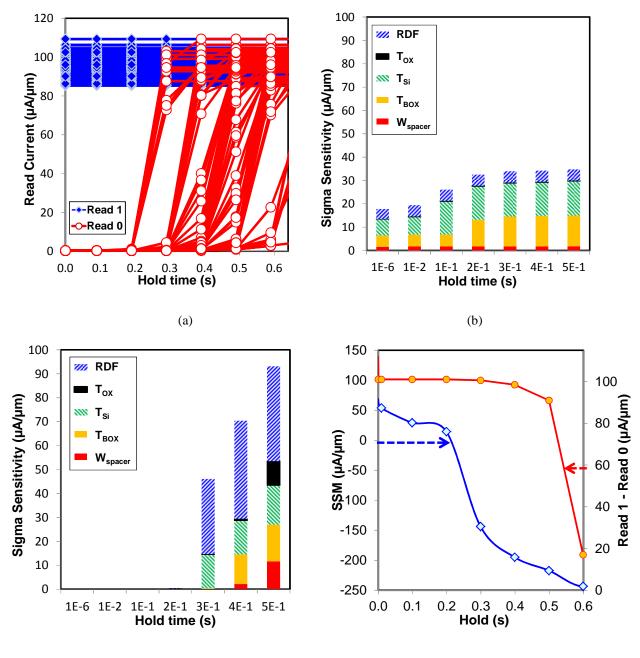

| 5.12 Gate length= 25 nm for sigma sensitivities, and signal sense margin          | 64    |

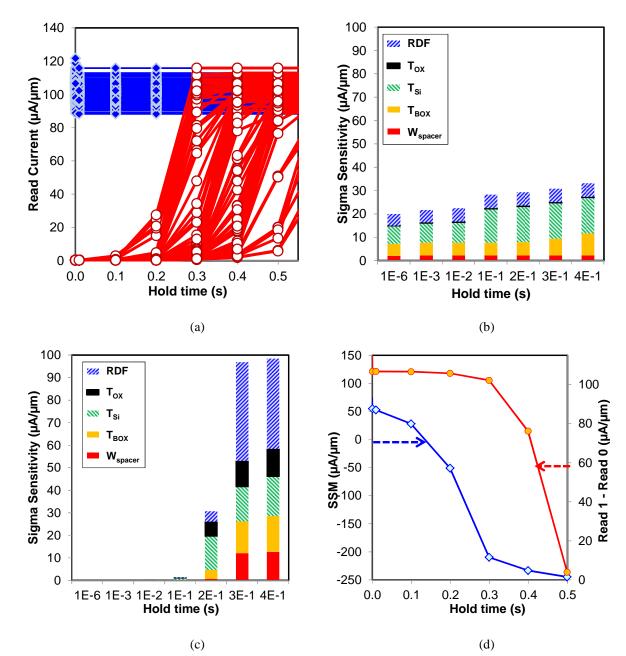

| 5.13 Gate length= 20 nm for sigma sensitivities, and signal sense margin          | 65    |

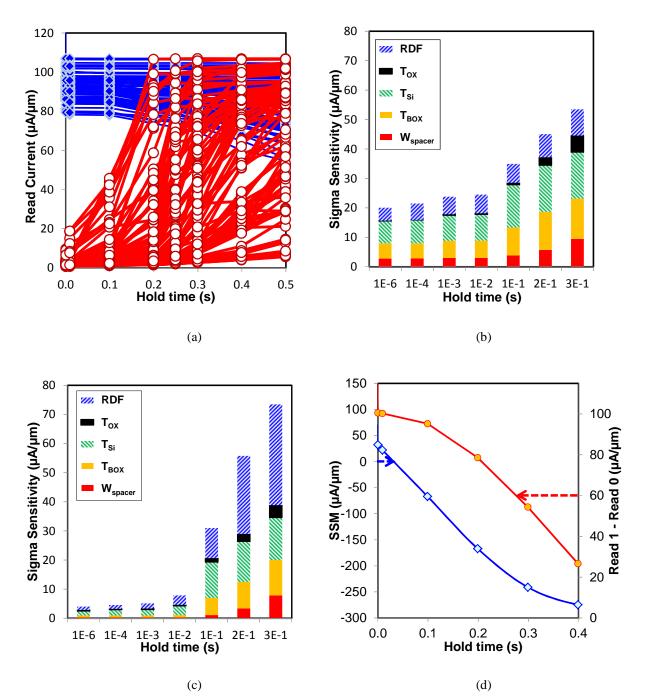

| 5.14 Gate length= 15 nm for sigma sensitivities, and signal sense margin          | 66    |

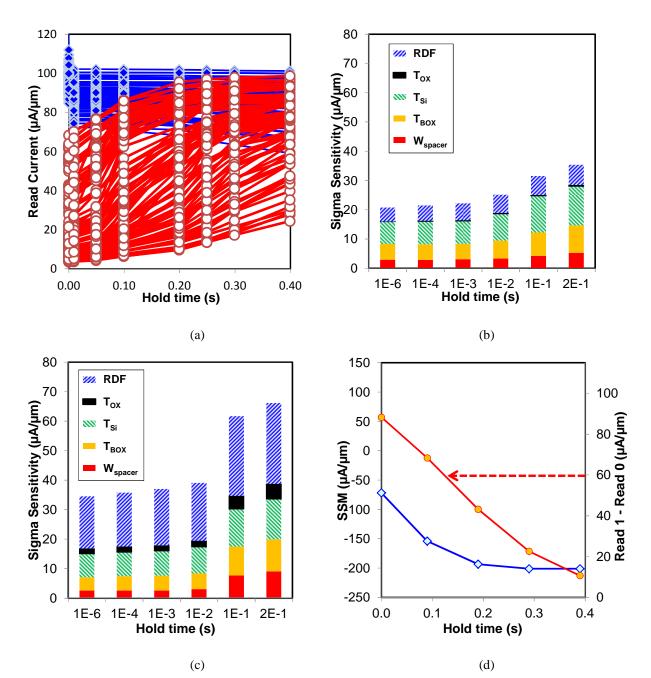

| 5.15 Gate length= 12 nm for sigma sensitivities, and signal sense margin          | 67    |

| 5.16 Gate length= 9 nm for sigma sensitivities, and signal sense margin           | 68    |

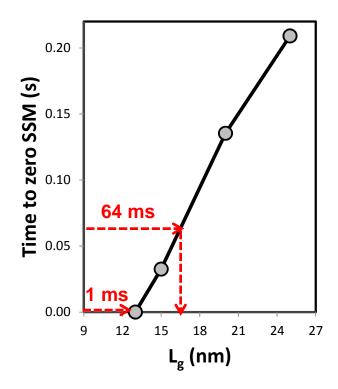

| 5.17 Time to Zero SSM (TZS) vs. gate length                                       | 69    |

| 6.1 Positive feedback flow                                                        | 76    |

| 6.2 Cross-sectional doping contour map                                            | 78    |

viii

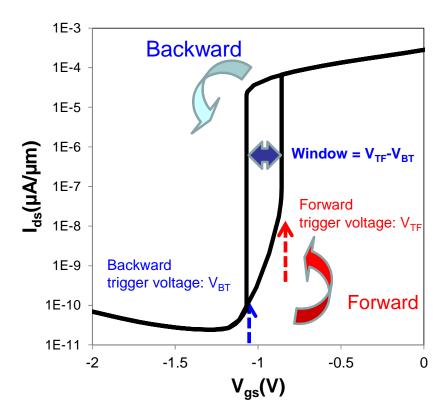

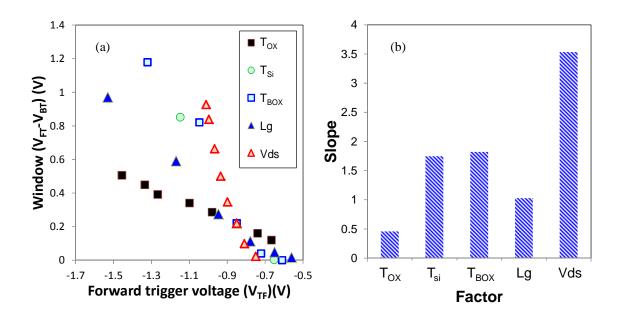

| 6.3 $I_{ds}$ -V <sub>gs</sub> curve with double sweep                                    | 79  |

|------------------------------------------------------------------------------------------|-----|

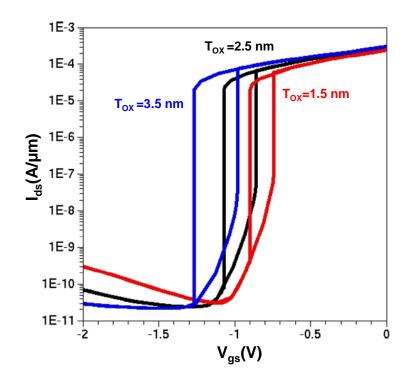

| 6.4 $I_{ds}$ -V <sub>gs</sub> curve with different gate oxide thicknesses (double sweep) | 81  |

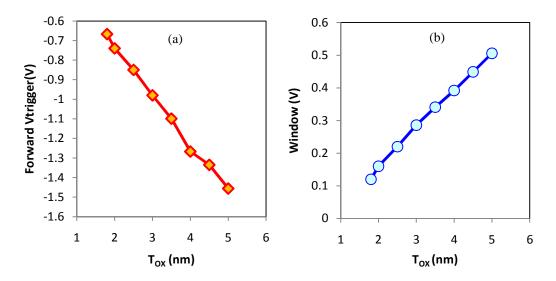

| 6.5 Gate oxide thickness effect on forward trigger voltage and Window                    | 81  |

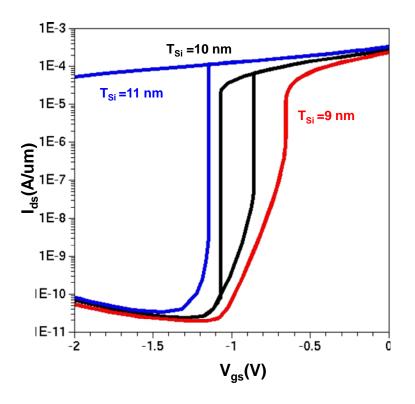

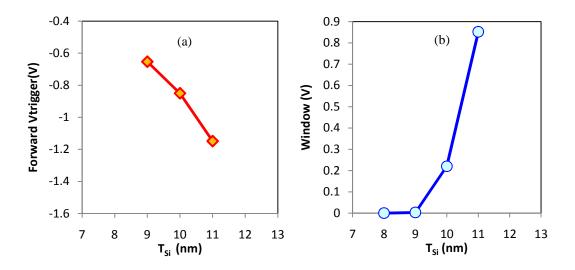

| 6.6 $I_{ds}$ -V <sub>gs</sub> curve with different body thicknesses (double sweep)       | 82  |

| 6.7 Body thickness effect on forward trigger voltage and Window                          | 82  |

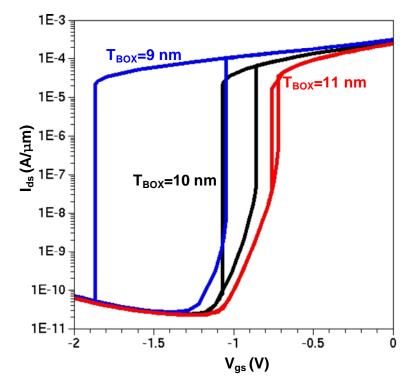

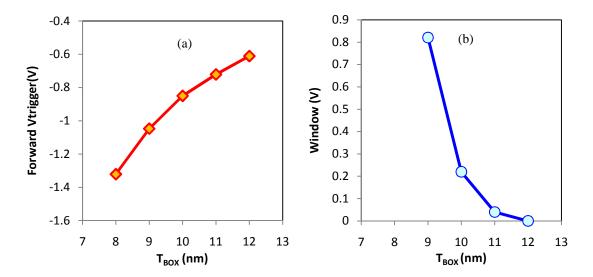

| 6.8 $I_{ds}$ -V <sub>gs</sub> curve with different BOX thicknesses (double sweep)        | 83  |

| 6.9 BOX thickness effect on forward trigger voltage and Window                           | 83  |

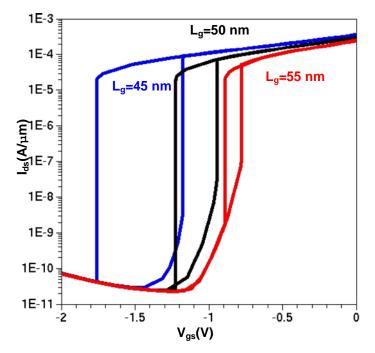

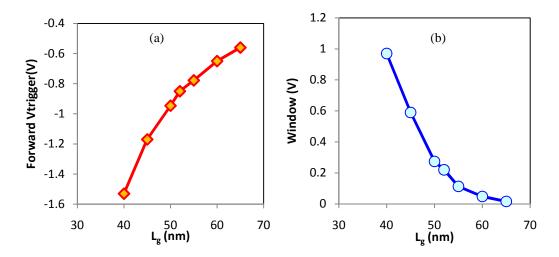

| 6.10 $I_{ds}$ -V <sub>gs</sub> curve with different gate lengths (double sweep)          | 84  |

| 6.11 Gate length effect on forward trigger voltage and Window                            | 84  |

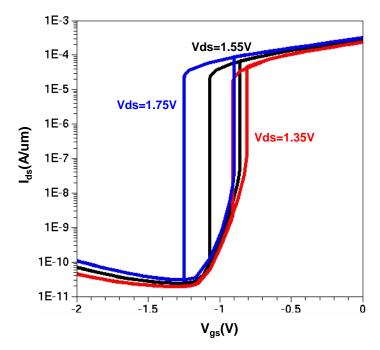

| 6.12 $I_{ds}$ -V <sub>gs</sub> curve with different drain voltages (double sweep)        | 85  |

| 6.13 Drain voltage effect on forward trigger voltage and Window                          | 85  |

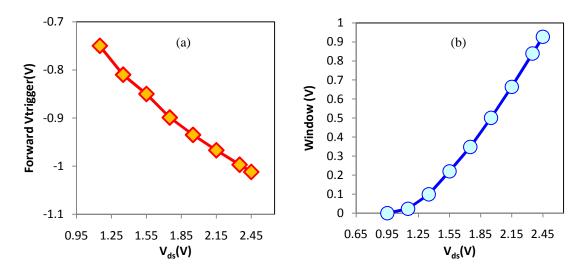

| 6.14a The relation between V <sub>TF</sub> and Window                                    | 86  |

| 6.14b Slopes for each factor                                                             | 86  |

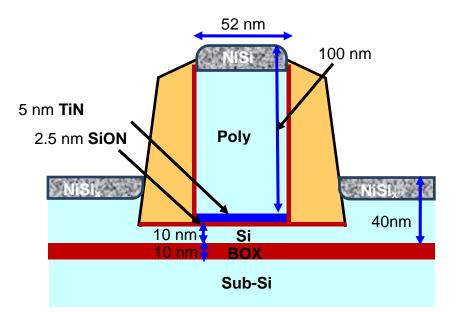

| 6.15 Cross-section view of a thin body SOI with UTBOX device                             | 87  |

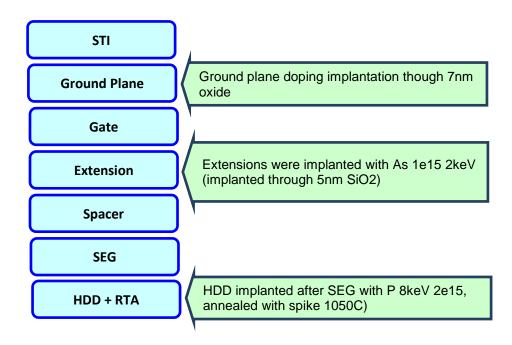

| 6.16 Process flow of device fabrication                                                  | 87  |

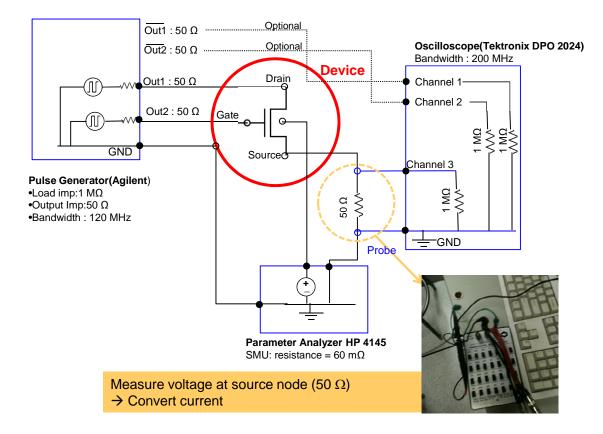

| 6.17 The measurement setup                                                               | 88  |

| 6.18 $I_{ds}$ -V <sub>gs</sub> curve for positive feedback transistor                    | 89  |

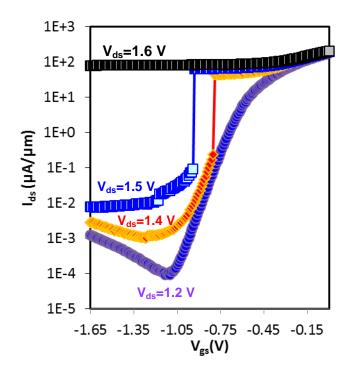

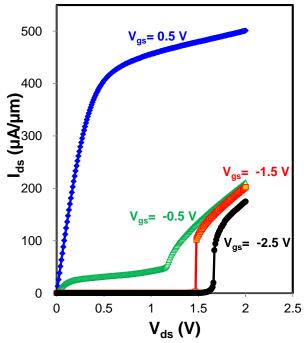

| 6.19 $I_{ds}$ - $V_{gs}$ curve with various $V_{ds}$                                     | 90  |

| 6.20 $I_{ds}$ -V <sub>ds</sub> curve with various V <sub>gs</sub>                        | 90  |

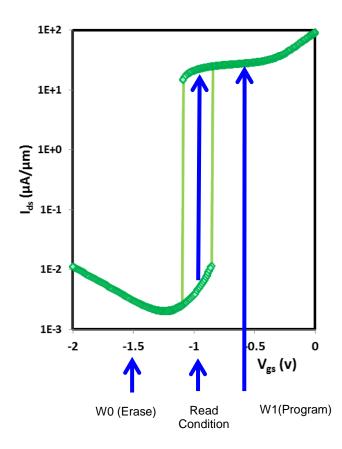

| 6.21 Capacitorless DRAM operating conditions                                             | 92  |

| 6.22 Sensing current vs. Hold time plots for capacitorless DRAM operation                | 93  |

| 6.23 Retention characteristics of PF-FET capacitorless DRAM                              | 93  |

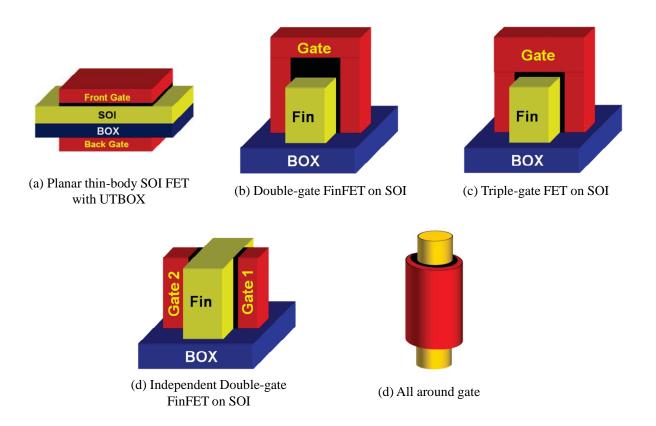

| 7.1 Illustration of multi-gate MOSFET structures                                         | 100 |

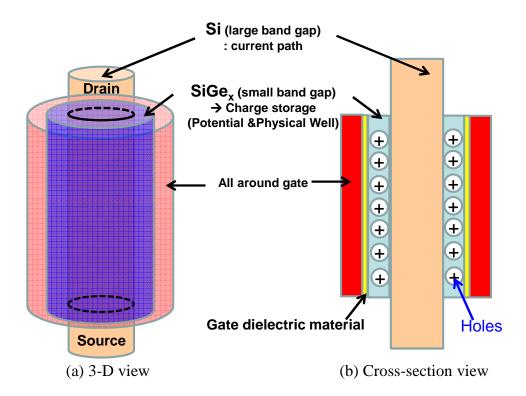

| 7.2 Vertical capacitorless DRAM structure using band gap engineering                     | 101 |

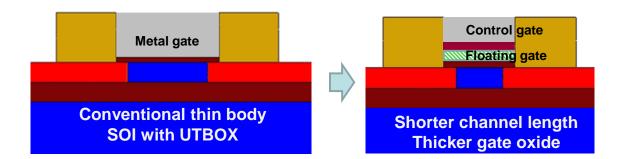

| 7.3 The tentative concept for NVM application using PF-FET                               | 102 |

| 7.4 Ids-Vgs curves for NVM using PF-FET                                                  | 102 |

# **List of Tables**

| 1.1 DRAM technologies                                                      | 3  |

|----------------------------------------------------------------------------|----|

| 1.2 Optimized dimension parameters for thin film SOI transistor with UTBOX | 9  |

| 2.1 FD-SOI capacitorless DRAM cell design parameters                       | 17 |

| 2.2 FD-SOI capacitorless DRAM cell biasing conditions                      | 17 |

| 3.1 Capacitorless DRAM cell design parameters                              | 28 |

| 3.2 Operating voltages for BJT mode                                        | 28 |

| 3.3 Operating voltages for MOSFET mode                                     | 28 |

| 3.4 Optimized operating conditions for BJT mode                            | 35 |

| 3.5 Summary of RDF simulation results                                      | 40 |

| 4.1 Capacitorless DRAM cell operating voltages                             | 44 |

| 4.2 Parameter variations are considered                                    | 45 |

| 5.1 Capacitorless DRAM cell operating voltages                             | 54 |

| 5.2 Optimized operating voltages for each gate length                      | 60 |

| 5.3 Retention time and electric field for each gate length                 | 61 |

| 5.4 Variation factors used for device simulations                          | 62 |

| 6.1 The summary of selected parameters for positive feedback simulation    | 77 |

| 6.2 Positive feedback transistor cell design parameters                    | 78 |

| 6.3 PF-FET capacitorless DRAM cell biasing conditions                      | 92 |

# Acknowledgements

I have been profoundly lucky to have been surrounded by a supportive, stimulating and highly collaborative intellectual environment during my time at UC Berkeley.

I would like to offer my deepest thanks to my academic advisor, Professor Tsu-Jae King Liu, whose unflinching intellect guided my research and writing from start to finish. I owe every word of this project to her advice, support, friendship, and generosity. She has provided constant and detailed feedback, suggestions, and an inspiring perspective, conjoined with engineering-intuition to pursue the project in whichever ways it required.

I am equally grateful to Professor Ming C. Wu and Professor Junqiao Wu as members of both my dissertation and qualifying examination committees. I also thank Professor Nathan W. Cheung for serving on my qualifying examination committee. They all nurtured and challenged my ideas and gave me valuable feedback. All of their lectures were greatly helpful to my research. I owe a tremendous debt to the support, encouragement, and intellectual contributions of the faculty, staff and graduate students in the Department of EECS as a whole for the encouragement and support I have received.

I would also like to thank Professor Vivek Subramanian for serving on my master degree committee. Furthermore, I would like to thank Dr. Siwoo Lee, a former visiting scholar, for our interesting discussions about my research. I was influenced tremendously in the formative stages of my project by his suggestions. Professor Changhwan Shin was a great research companion who worked tirelessly with me to develop ideas. I appreciate the help and advice from Emeritus Professor Jai-Young Lee who has been my advisor at KAIST in Korea.

I would like to thank several former and current students who gave me valuable feedback. Wookhyun Kwon, Dr. Nuo Xu, Nattapol Damrongplasit, Dr. Sunghwan Kim, and Dr. Donovan Lee. They provided kind assistance and several helpful discussions. I would like to thank all the members of the UC Berkeley (especially device group) for always readily imparting their wisdom - Dr. Louis Hutin, Dr. Jemin Park, Jaewon Jang , Dr. Kanghoon Jeon, Dr. Xin Sun, Dr. Joanna Lai, Dr. Yasumasa Tsukamoto, Dr. Andrew Carlson, Dr. Seng Oon Toh, Prof. Hyuck Choo, Dr. Alvaro Padilla, Dr. Reinaldo Vega, Dr. Hei Kam, Dr. Jaein Jeong, Dr. Rhesa Nathanael, Dr. Zachery Jacobson, Professor Jaeseok Jeon, Byron Ho, Dr. Peter Matheu, I-Ru (Tim) Chen, Yenhao (Philip) Chen, Jack Yaung, Dr. Darsen D. Lu, Kangwook Lee, Sangyoon Han, Dr. Youngki Yoon, Shinwon Kang, Hongki Kang, Hyun Oh Song, Claire Baek, Dr. Sangyong Kim, Dr. Yongsik Park, Kyunghoon Kim (Ken), Daeyoung Kong, Jaehwa Kwak, Namseog Kim, Dr. Jung-Dong Park, Kwangmo Jung, Dr. Tae Joon Seok, Se Yong Park, Dr. Changho Suh, Kyoohyun Noh, Sunyoung Lee, Eungseok Park, SunYoung Kim, Chen Dan Dong, Yi-Bo Liao, Professor

Moonsuk Yi, Jodie Jang, Katerina Papadopoulou, Chun Wing Yeung, Dr. SungJin Choi, Professor Ali Javey, and Professor Chenming Hu, *etc*.

I wish to thank my colleagues and supervisors at Samsung Electronics for their help. I owe a great deal of thanks to Samsung Electronics for their financial support. I'd like also to thank Dr. Cyndi Lowe. She gave me a lot of help and is a good friend. Mrs. Hilda and her family and the people in Richmond Korean Church have been positively mentors in my life.

Finally I owe my gracious thanks to my family. None of this would have been possible without the love and support. In particular, I want to acknowledge my lovely spouse, Ji Hye Yi, and our adorable sons HyunSung Cho and HyunSoo Cho. Without their encouragement and understanding, it would have been impossible for me to finish this work. My Love.

# Chapter 1

# Introduction

## 1.1 Dynamic Random Access Memory (DRAM)

### **1.1.1 Conventional DRAM and Limitation**

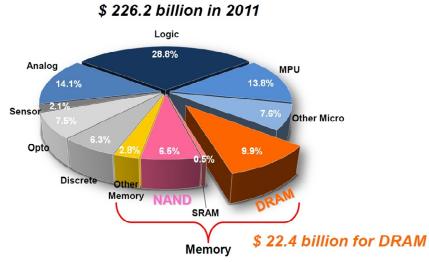

Dynamic random access memory (DRAM) is the most common kind of random access memory for mobile/personal computers and workstations. Memory is defined as a device (as a chip) or a component of a device in which information especially for a computer can be inserted and stored and from which it may be extracted when wanted. Random access allows stored data to be accessed in any order. A conventional DRAM cell has simple structure, which is composed of one transistor and one capacitor (1T1C) per bit [1]. The transistor acts as a switch for input and output. Different from static RAM (SRAM), DRAM is dynamic in operation; it needs to have its storage cells refreshed every few milliseconds. Since real capacitors and transistors leak charge, the information eventually fades unless the capacitor charge is refreshed periodically. DRAM is also volatile, since it loses its data when the power supply is removed. Because of the DRAM cell structure (1T1C) its size is smaller than a SRAM cell which has six transistors. This allows DRAM to reach very high density. The DRAM market in the semiconductor industry occupies a large portion, as shown in **Fig. 1.1** [2, 3], which means that more innovative research is needed to in order to maintain a competitive edge.

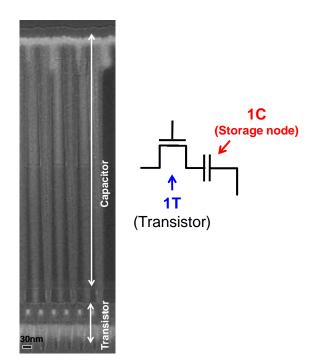

**Fig. 1.2** shows the conventional DRAM structure (capacitor over bit line (COB) type) [4]. At the sub-30nm half pitch, conventional DRAM cells might suffer from technological scaling issues, as shown in **Table 1.1** and **Fig. 1.3** [5]. It is harder to build a capacitor in a small cell-area with sufficient capacitance, usually 20~25 fF [5] to provide enough signal-to-noise ratio, as compared with transistor scaling. Novel high dielectric-constant (high  $\kappa$ )

materials or capacitor structures have been proposed to overcome scaling issues and have become the main focus for current DRAM technologies [6]. DRAM designers have pioneered the use of high-k dielectrics (*e.g.*,  $ZrO_2$ ,  $HfO_2$ , or  $SrTiO_3$  *etc.*), and extreme capacitor geometry (*e.g.*, trench, fin, and stack). Despite this comprehensive approach, however, the scaling of 1T1C DRAM cells has significant obstacles due to the capacitor.

Figure 1.1. DRAM in semiconductor industry [2, 3].

Figure 1.2. Conventional 1T1C DRAM structure. Each cell has one transistor (switch) and one capacitor (storage node) [4].

Besides the fact that the fabrication process for DRAM of several gigabits and beyond is becoming more and more difficult, the development and manufacturing costs are increasing drastically. A significant portion of the technology developed for DRAM is not extendible to other products. In order to overcome cell-area scalability and the process complexity issues of traditional DRAM technology, the concept of capacitorless DRAM was introduced in the early 1990s [7].

| Year | Half Pitch (nm) | Cell Size (µm²) | A/R of SN | A/R of SN (out) for cell plate deposition |

|------|-----------------|-----------------|-----------|-------------------------------------------|

| 2010 | 45              | 0.0122          | 47.3      | 74.5                                      |

| 2011 | 40              | 0.0096          | 57.5      | 97.5                                      |

| 2012 | 36              | 0.0078          | 44.4      | 77.5                                      |

| 2013 | 32              | 0.0061          | 56.2      | 108.3                                     |

| 2014 | 28              | 0.0047          | 73.5      | 163.2                                     |

| 2015 | 25              | 0.0038          | 76.9      | 199.9                                     |

| 2016 | 22              | 0.0029          | 99.4      | 330.5                                     |

| 2017 | 20              | 0.0024          | 108.3     | 351.9                                     |

Manufacturable solutions exist Manufacturable solutions are known Manufacturable solutions are NOT known

Table 1.1. DRAM technologies. Half pitch, aspect ratio (A/R) of capacitor (storage node: SN), and A/R of SN (out) for cell plate (upper electrode) deposition are shown in table. Source; International Technology Roadmap for Semiconductors (ITRS) 2011 [5]. White = Manufacturable solutions exist, yellow = Manufacturable solutions are known, and red = Manufacturable solutions are NOT known.

Figure 1.3. A/R of storage node is calculated as (SN height) / F, and A/R of SN (out) is calculated as (SN height) / (F  $- 2 \times t$ ). F = minimum feature size, t = physical high k dielectric layer thickness [5].

### 1.1.2 Operating Principles of Capacitorless DRAM

**Fig. 1.4** shows a cross section view of a typical capacitorless DRAM [8]. Its structure is very simple – one transistor on a silicon-on-insulator (SOI) wafer. Capacitorless DRAM can provide important advantages to chip manufacturers, who are reluctant to add any new material to their already complex and delicate processes [9]. Extra processing steps are highly undesirable for memory chip producers, because they increase manufacturing costs, often greatly. Thus this is a major advantage of capacitorless DRAM. Each memory cell is just a single transistor. For comparison, conventional on-chip memories (SRAM) typically use six transistors per memory cell, so we can fit more cells into the space occupied by conventional embedded memory. This increases the amount of memory on the chip and thereby improves its performance, making the chip a lot smaller and less expensive [9].

Figure 1.4. Typical capacitorless DRAM [8]. Only one transistor on SOI wafer.

Figure 1.5. Capacitorless DRAM operation (MOSFET mode). (a) Write 1 (*i.e.* programming). N-MOSFET turns on and high drain voltage (usually > 2V) is applied in order to induce impact ionization. (b) Read 1 (Read programmed cell state). Due to floating body effect, threshold voltage ( $V_T$ ) is lowered. Higher current flow compared to Read 0 state (No charge stored state:  $V_T$  is high).

The original concept of capacitorless DRAM utilizes the floating-body effect of a SOI transistor [7]. In capacitorless DRAM, the conventional storage capacitor can be replaced by the body capacitance of the transistor. Figs. 1.5 (a) and (b) show Write 1 (*i.e.* programming) and Read 1 (i.e. reading programmed cell state) processes. When the transistor turns on and high drain voltage is applied, impact ionization occurs and electronhole pairs are generated due to the high electric field. When excess holes exist in the floating body, the cell state can be defined as "1" (Data 1 state). On the other hand, when excess holes are swept out of the floating body through the forward bias on the body - drain junction, the cell state can be defined as "0" (Date 0 state). By measuring the drain current difference between the Read 1 and Read 0 states of the cell, we can sense whether the holes are accumulated in the floating body as shown in Fig. 1.6. In other words, a logic state is defined by creating an excess or a shortage of the majority carriers ( $\Delta Q$ ) inside the body of the transistor. When a number of majority carriers are stored in the SOI, the body effect changes the transistor threshold voltage (V<sub>T</sub>) and hence its on-state drive-current. This is the basic method that the capacitorless DRAM uses to distinguish two states. Okhonin et al. referred to this MOSFET operation mode with floating body effect (MOSFET mode) Generation 1 mode (Gen1) [10]. In the last 20 years, several research groups and companies have published researches about MOSFET mode [8, 11, 12], and it is investigated here, in chapter 2. This mode provides stable operations in partially depleted SOI (PDSOI), and operating voltage conditions (front gate, back gate bias) are very similar to the normal MOSFET operation.

Figure 1.6.  $I_{ds}$ - $V_{gs}$  curve of Capacitorless DRAM (MOSFET mode). In data 1 state (D1), high current flows due to floating body effect.  $V_T$  is high in data 0 state (D0).

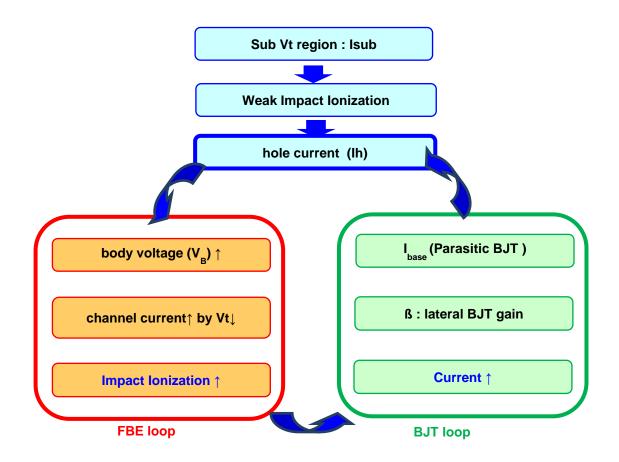

More recently, Okhonin *et al.* introduced the bipolar junction transistor (BJT) based operation mode (BJT mode) of capacitorless DRAM [10]. While the MOSFET mode uses the triode operation of MOSFET in the Read state, the BJT mode is largely based on the parasitic BJT which is present in the MOS structure (**Fig. 1.7**). The basic Write operation uses the punch-through effect in Write 1 (**Fig. 1.7**(a)). Negative gate and high positive drain biases are applied. Impact ionization occurs as a result of the punch-through current

(not the inversion current in the channel) and majority charges are accumulated near the front gate rather than the buried oxide (BOX) interface, as shown in Fig. 1.7(b). In the case of an N-channel device, the N+ source, the P-type body, and the N+ drain form the emitter, the base, and the collector of an NPN bipolar transistor, respectively. In a floating body SOI device, the body (*i.e.* the base of the bipolar transistor) is used as a storage node (Fig. 1.8) [10]. The Read operation is performed by sensing the bipolar current in contrast to the MOSFET mode capacitorless DRAM, where the channel current is used. During the Read operation, the bipolar transistor is in a state of turn-on when the cell state is Data 1. It is in a state of turn-off when there are very few holes left, which means that the potential barrier from the source (emitter) to the drain (collector) is high enough to prevent on-current.

The BJT mode improves sensing margin [10] (i.e. the difference between Read 1 and Read 0 current) due to the higher current gain of the BJT [11]. Data retention time is expected to increase [10]. Because the capacitive coupling to the body of the front gate is higher than that of the back gate, it is much more effective to retain holes in the body using the front gate. The higher margin provides much shorter data read times and better device scalability. This improvement also broadens the range of applications that can take advantage of the high density of a capacitorless DRAM chip.

(a) Write 1

Figure 1.7. Capacitorless DRAM operation (BJT mode). (a) Write 1. High drain voltage (usually > 2V) is applied and punch-through occurs, which induces impact ionization. (b) Read 1. Negative gate bias retains holes below gate oxide. Under the BJT operation mode, BJT current flow through emitter (source) to collector (drain).

Figure 1.8. BJT mode schematic [10].

## **1.2 Structure Design and Simulation Models**

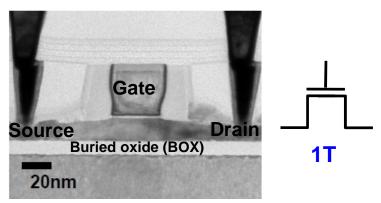

### **1.2.1** Thin Film SOI with UTBOX

Planar bulk and/or PDSOI technology face many obstacles to widespread adoption. They suffer from the short channel effect (V<sub>T</sub> reduction with decreasing gate length) with sub-surface leakage paths and drain induced barrier lowering (DIBL). Increasing variability in transistor and circuit performance for these structures require more complex chip design. In order to suppress off-state leakage, heavy channel doping can be used [11]. As the channel doping and/or halo doping in conventional planar bulk/PDSOI MOSFETs is increased with scaling to suppress short-channel effects, random-dopant-fluctuation (RDF)induced variation also increases. Rather than doping the channel heavily to suppress offstate leakage, body thickness can be reduced substantially [12]. As a result, the channel/body region is so thin (with a thickness less than 1/3 of the gate length) that it is fully depleted of mobile charge carriers when the transistor is in the off state. Due to high coupling of the gate, the short channel effect of the transistor can be suppressed effectively with fully depleted SOI (FDSOI) structure. The use of a lightly doped SOI MOSFET structure with an ultra-thin (~10 nm-thick) buried oxide (UTBOX) and a heavily doped substrate has been reported to be effective for suppressing this variation [13, 14]. RDFinduced V<sub>T</sub> variation can be dramatically lower in a FDSOI MOSFET since light channel/body doping can be used. Simple structure and fabrication processes of FDSOI are also advantages. With a thin film SOI substrate, FDSOI is easily implemented [15].

For memory applications, the floating body effect is essential for  $V_T$  shift. The floating body effect, however, is negligible in an FDSOI MOSFET because there is no quasi-neutral body region which serves as a potential well to hold majority carriers [16, 17]. UTBOX is essentially back-gated MOSFET. With the control of the back bias (Vbg), it is possible to retain excess hole in the body. This pseudo-floating body effect enables the utilization of FDSOI in capacitorless DRAM.

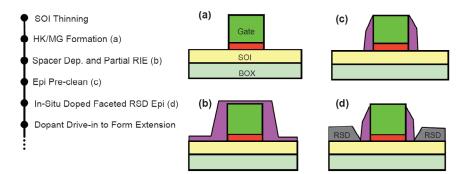

The thin body may induce higher source/drain resistance, which reduces the on-current. The raised-source/drain structure provides a good solution for minimizing source/drain series resistance [18]. The problems of PDSOI MOSFET and the characteristics of FDSOI MOSFET as a solution are explained in **Figs. 1.9** and **1.10**. The thin film SOI using UTBOX technology can meet requirements for capacitorless DRAM applications with regard to scalability, memory effect (floating body effect), low variability, and manufacturability.

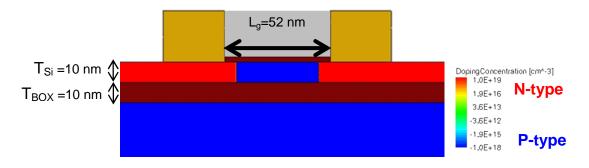

**Fig. 1.11 (a)** shows a cross-sectional view of the reference structure (transmission electron microscope (TEM) image [18]), and a simulated N-channel MOSFET structure, based on fabricated MOSFET (**Fig. 1.11 (a)**) is shown in **Fig. 1.11(b**). An implantation-free process is used in order to avoid dopant-atom straggle as well as defects in the body region, and to minimize RDF-induced variations, as follows [18]: in order to decrease series resistance with reducing gate-sidewall capacitance, faceted raised source/drain (RSD) processes are selectively grown. This structure can be formed with a low-temperature, zero-

silicon-loss epitaxial growth process, with in-situ doping (around  $10^{20}$  cm<sup>-3</sup>). Dopant atoms from the raised-source/drain regions diffuse into the channel and form the lightly doped source/drain extension regions.

Figure 1.9. Cross section view of (a) partially depleted SOI (PDSOI) transistor and (b) fully depleted SOI (FDSOI) transistor with raised source/drain and ultra-thin BOX (UTBOX).

Figure 1.10. Characteristics of PDSOI and FDSOI. Raised source/drain with UTBOX FDSOI is proposed as a solution.

Physical and operating parameters (gate length, gate oxide thickness, supply voltage, *etc.*) are taken from the International Technology Roadmap for Semiconductors for low operating power (LOP) technology at the 22 nm node [5]. The initial width of the gate-sidewall spacers ( $W_{spacer}$ ) is selected to be 13 nm, based on the gate-to-contact spacing design rule for recent study (6-T SRAM cell) [14]. The gate work function values were then selected to adjust the nominal  $V_T$  values in order to meet the off-state leakage current ( $I_{OFF}$ ) specification, 3 nA/µm. The fabrication processes are shown in **Fig. 1.12** and the optimized dimension parameters for the device are summarized in **Table 1.2**.

(a) TEM image

(b) Process simulation structure

Figure 1.11. (a) TEM (transmission electron microscope) image of thin film SOI with UTBOX (reference structure [15]). (b) Cross-sectional view of simulated n-channel MOSFET structure based on (a).

Figure 1.12. Thin film SOI transistor process flow: no Si loss is achieved by an optimized partial spacer dry etch; The remaining nitride is removed during epiprecleaning. An in-situ doped *faceted* RSD is formed to minimize parasitic capacitance. Extensions are formed by dopant drive-in from in-situ doped RSD to avoid implant damage to transistor [18].

|                                     | Dimension                         |

|-------------------------------------|-----------------------------------|

| Physical gate length (Lg)           | 25nm                              |

| Physical gate width                 | 50nm                              |

| Spacer width (W <sub>spacer</sub> ) | 13nm                              |

| Gate oxide (T <sub>OX</sub> )       | 1nm                               |

| Body thickness (T <sub>Si</sub> )   | 10nm                              |

| BOX thickness (T <sub>BOX</sub> )   | 10nm                              |

| Channel doping                      | Intrinsic                         |

| Source/Drain doping                 | 10 <sup>20</sup> cm <sup>-3</sup> |

| Substrate doping                    | 10 <sup>18</sup> cm <sup>-3</sup> |

| Gate work function                  | 4.6eV                             |

Table 1.2. Optimized dimension parameters for thin film SOI transistor with UTBOX

In this simulated structure, the *Sentaurus Process* is used and it provides a complete and highly flexible, multidimensional, process modeling environment [19]. Calibrated to a wide range of the latest experimental data using proven calibration methodology, this computer-aided design (TCAD) tool offers unique predictive capabilities for modern silicon and non-silicon technologies.

### 1.2.2 Simulation Methodology [20]

In this study, the Sentaurus Device is chosen as the TCAD simulation tool [20]. Proper physical models are selected to embody capacitorless DRAM, which allows for the possibility to simulate real phenomena. This section describes the selected physical models and the reasons why they are chosen.

#### 1) Electrostatic Potential

Ionized dopants or traps (immobile charges) and electrons/holes (mobile charges) play key roles in all semiconductor devices. These charges and the electrostatic potential determine the electrostatic potential, and vice versa. Physical phenomena in semiconductor devices can be complicated and depends on charge distribution, microscopic physics, the applied bias, and the structure of the device. All charges in the device interact with each other and should be calculated with the electrostatic potential. These are calculated based on Poisson's equation, which is:

$$\nabla \cdot \left( \varepsilon \nabla \phi + \overline{P} \right) = -q(p - n + N_D - N_A) - \rho_{\text{trap}}$$

(1)

Where:

$\varepsilon$ : the electrical permittivity

$\overline{P}$ : the ferroelectric polarization

q: the elementary electronic charge.

n and p: the electron and hole densities.

$N_D$  and  $N_A$ : the concentration of ionized donors and acceptors

$\rho_{\rm trap}$  : the charge density contributed by traps and fixed charges

#### 2) Hydrodynamic Transport Model: Hydrodynamic (eTemperature)

Characteristics of state-of-the-art scaled semiconductor devices cannot be described properly using the conventional drift-diffusion transport model. In particular, the driftdiffusion approach cannot reproduce velocity overshoot and often overestimates the impact ionization generation rates. The hydrodynamic (or energy balance) model provides a very adequate compromise. It takes into account an average of the carrier temperature as well as the lattice temperature, which can be useful in devices where the carrier diffusion is important. This model can also reduce possible convergence errors and simulation times.

### 3) Semiconductor Band Structure

The most fundamental property of a semiconductor is its band structure. Realistic band structures are complex and can only be fully accounted for in Monte Carlo simulations. The band structure is simplified to several quantities: the energies of the conduction and valence band edges, and the density-of-states masses for electrons and holes. The silicon band-gap narrowing model determines the intrinsic carrier concentration. In this simulation, *OldSlotboom* model is selected, which is based on measurements of in n-p-n transistors, because the BJT mode is used in capacitorless DRAM.

### 4) Mobility

The Sentaurus Device uses a modular approach for the description of the carrier mobility. The mobility is a function of both phonon scattering and coulombic scattering. The lattice temperature mobility model is called the constant mobility model and it should only be used for undoped materials. For doped materials, the carriers scatter with impurities. This leads to a degradation of the mobility. The mobility degradation at interfaces, (*e.g.* the silicon/oxide interface in the channel region of a MOSFET) is also considered. These models account for the scattering of surface phonons and surface roughness. Additionally, this simulation includes the effects of carrier–carrier scattering and electric fields.

### 5) Recombination:

Generation and recombination processes are very important in device physics, and in particular, for capacitorless DRAM devices. These processes exchange carriers between the conduction and valence bands. For each individual generation or recombination process, the electrons and holes involved appear or vanish at the same location. The only exception is the band-to-band tunneling (BTBT) model.

**Shockley–Read–Hall (SRH) recombination**: Recombination through deep defect levels in the gap is usually labeled as SRH recombination. SRH lifetimes depend on doping, temperature, electric field, *etc*.

**Surface SRH Recombination:** The surface SRH recombination model can be activated at the interface between two different materials or two different regions.

Auger Recombination: At high carrier densities the Auger recombination is very important. Because high current are induced in the Write 1 state in capacitorless DRAM, it should be considered when conducting simulations.

**Avalanche Generation:** The floating body effect comes from a generated electron-hole pair. It is one of key models for Write 1. Electron–hole pair production due to avalanche generation (impact ionization) requires certain threshold field strength and the possibility of acceleration, that is, wide space charge regions. If the width of a space charge region is greater than the mean free path between two ionizing impacts, charge multiplication occurs, which can cause electrical breakdown. The reciprocal of the mean free path is called the ionization coefficient.

**Band-to-Band Tunneling Models:** Band-to-Band Tunneling (BTBT) leakage is a main reason for the degradation of retention time in capacitorless DRAM. Because capacitorless

DRAM has little junction leakage (due to the SOI structure) and no dielectric leakage of capacitor, there are fewer leakage path in the structure compared to conventional DRAM. However, holes should be retained in the body, which is acutely affected by BTBT leakage. Phonon-assisted band-to-band tunneling cannot be neglected in steep p-n junctions or in high electric fields of MOS structures. Due to this factor, defect-assisted tunneling (SRH) is also considered for the device simulations.

#### 6) Quantum Well

With scaling, quantum confinement effect is another factor that should be considered. The Quantum Well (QW) sub-band model, the QW transport model, and the scattering model are all activated in this simulation.

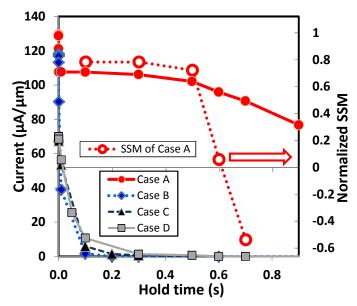

### **1.2.3** Random Dopant Fluctuations (RDF)

**Fig. 1.13** shows randomly distributed dopant atoms in an n-channel MOSFET [21]. Previous experiments and simulation have confirmed RDF as one of the obstacles to continued transistor scaling [14, 21-25]. It is well known that RDF-induced V<sub>T</sub> variation is inversely proportional to  $(W \times L)^{0.5}$ , where W and L are the transistor channel width and length, respectively [26]. Recently, in a 100,000-sample 3-dimensional simulation study [23], the complete V<sub>T</sub> distribution caused by RDF was constructed through the discrete convolution of a Poisson distribution with the mean (N) of the number of dopants in channel region, and a Gaussian distribution of V<sub>T</sub> for a fixed N. Because the channel doping is intrinsic in FDSOI, there are fewer issues for random dopant fluctuations (RDF) compared to PDSOI or bulk transistor. RDF is still one of main variation factors in ultrascaled devices though RDF is suppressed effectively in FDSOI [22]. Randomly distributed dopants affect not only V<sub>T</sub> variation but also the impact ionization rate and the local BTBT rate, which can influence retention time and sensing current.

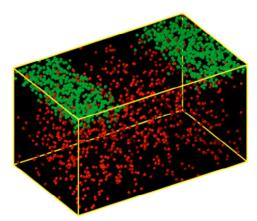

Figure 1.13. Randomly distributed dopants in an N-MOSFET with channel length of 30 nm and channel width of 50 nm [23]. Green atoms are donors and red colored atoms are acceptors.

## **1.3 Dissertation Outline**

Thin body SOI with UTBOX structure is very a promising design for scaled technologies. It suppresses the short channel effect and minimizes variability. The application of thin body SOI with UTBOX MOSFET to capacitorless DRAM is important because this device has many advantages such as simple processes, high scalability, and reduced variability. This research focuses on the optimization, analysis, and scalability of capacitorless DRAM with highly scaled (22nm-node) technologies.

In chapter 2, the impact of substrate doping on back-gated FDSOI capacitorless DRAM cell performance is investigated to provide guidance for design optimization. In this chapter, the basic capacitorless operating mode (MOSFET mode) is focused upon. In order to optimize the tradeoff between increasing sensing margin and degraded retention time, the peak doping concentration is investigated

In chapter 3, a capacitorless DRAM cell design using BJT mode is studied. The impact of gate-sidewall spacer width and operating voltages is investigated to reduce BTBT leakage. Kinetic Monte Carlo (KMC) simulations are used to compare the effects of RDF on the read current distributions of cells designed for BJT-mode *vs.* MOSFET-mode operation. It is found that BJT-based operation is more robust to RDF effects than metal-oxide-semiconductor field-effect transistor (MOSFET)-based operation.

In chapter 4, variability in back-gated thin-body capacitorless DRAM cell performance is investigated. Sources of variability considered include variations in front gate oxide thickness, body thickness, buried oxide thickness, and gate-sidewall spacer width, as well as RDF. The BJT mode is most sensitive to variations in body thickness and buried oxide thickness. Reduced retention time, taking into account process-induced variations, is predicted in this chapter.

In chapter 5, the scaling limitation of capacitorless DRAM is investigated. Based on the analysis method in chapter 4, dimension variations are simulated. After body thickness limit is investigated, optimized conditions for each scaled device are achieved using the constant electric field rule. Design parameters ( $W_{spacer}$ ,  $T_{Si}$ ,  $T_{BOX}$ , and  $T_{OX}$ ) and RDF are considered as variation factors. In this study, the scaling limit of capacitorless DRAM is predicted.

In chapter 6, positive feedback MOSFET is tested experimentally with SOI transistor. The device was fabricated on thin body (10 nm) and thin BOX (10 nm) SOI structure. Positive feedback occurs as a result of both the BJT operation and the floating body effect from weak impact ionization. Steep sub-threshold slope is achieved with positive feedback. Positive feedback properties are investigated utilizing TCAD simulation. Positive feedback and wide hysteresis window are measured, which enables the PF-FET to potentially serve as a memory device. The PF-FET capacitorless DRAM characteristics (retention time and sensing current) are measured experimentally.

Chapter 7 summarizes the key results and contributions of this dissertation; future research directions are also suggested.

## **1.4 References**

- [1] R.H. Dennard, "Field-Effect Transistor Memory", U.S. patent 3,387,286, 1968.

- [2] S. Y. Cha "DRAM Technology History & Challenges," IEDM short course, 2011.

- [3] World Semiconductor Trade Statics (WSTS). [Online]. Avalable: 2011 http://www.wsts.org/

- [4] T. Schloesser, F. Jakubowski, J. v. Kluge, A. Graham, S. Slesazeck, M. Popp, P. Baars, K. Muemmler, P. Moll, K. Wilson, A. Buerke, D. Koehler, J. Radecker, E. Erben, U. Zimmermann, T. Vorrath, B. Fischer, G. Aichmayr, R. Agaiby, W. Pamler, T. Schuster, W. Bergner, and W. Mueller, "A 6F<sup>2</sup> Buried Wordline DRAM Cell for 40nm and Beyond," *IEDM Tech. Dig.*, Dec. 2008, pp. 1 4.

- [5] International Technology Roadmap for Semiconductors (ITRS). [Online]. Available: <u>http://public.itrs.net</u>

- [6] S. Hong, "Memory technology trend and future challenges," *IEDM Tech. Dig.*, Dec. 2010, pp. 12.4.1 12.4.4.

- [7] H.-J. Wann and C. Hu, "Capacitorless DRAM Cell on SOI Substrate," *IEDM Tech. Dig.*, Dec. 1993, pp. 635 638.

- [8] S. Kim, R. J. Tseng, W. Rachmady, B. Jin, U. Shah, I. Ban, U. E. Avci, and P. L..D. Chang, "Silicon on Replacement Insulator (SRI) Floating Body Cell (FBC) Memory," *VLSI Symp. Circuit Dig.*, Jun. 2010, pp. 165-166.

- [9] S. K. Moore, "Master of memory", IEEE Spectrum, Jan. 2007, pp. 45-49.

- [10] S. Okhonin, M. Nagoga, E. Carman, R. Beffa, E. Faraoni, "New Generation of Z-RAM," *IEDM Tech. Dig.*, Dec. 2007, pp. 925-928.

- [11] Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices. Cambridge, U.K.: Cambridge Univ. Press, 2006.

- [12] Y.-K. Choi, K. Asano, N. Lindert, V. Subramanian, T.-J. King, J. Bokor, and C. Hu, "Ultra-thin body SOI MOSFET for deep-sub-tenth micron era," *IEDM Tech. Dig.*, Dec. 1999, pp. 919–921.

- [13] T. Ohtou, N. Sugii, and T. Hiramoto, "Impact of parameter variations and random dopant fluctuations on short-channel fully depleted SOI MOSFETs with extremely thin BOX," *IEEE Electron Device Lett.*, vol. 28, no. 8, pp. 740–742, Aug. 2007.

- [14] C. Shin, M. H. Cho, Y. Tsukamoto, B.-Y. Nguyen, B. Nikolić, and T.-J. K. Liu, "SRAM yield enhancement with thin-BOX FD-SOI," *Proc. IEEE Int. SOI Conf.*, Oct. 2009, pp. 1–2.

- [15] K. Cheng, A. Khakifirooz, P. Kulkarni, S. Ponoth, J. Kuss, D. Shahrjerdi, L. F. Edge, A. Kimball, S. Kanakasabapathy, K. Xiu, S. Schmitz, A. Reznicek, T. Adam, H. He, N. Loubet, S. Holmes, S. Mehta, D. Yang, A. Upham, S.-C. Seo, J. L. Herman, R. Johnson, Y. Zhu, P. Jamison, B. S. Haran, Z. Zhu, L. H. Vanamurth, S. Fan, D. Horak, H. Bu, P. J. Oldiges, D. K. Sadana, P. Kozlowski, D. McHerron, J. O'Neill, B. Doris, "Extremely thin SOI (ETSOI) CMOS with record low variability for low power system-on-chip applications," *IEDM Tech. Dig.*, Dec. 2009, pp. 1-4.

- [16] C. L. Chen, R.T. Chang, P.W. Wyatt, C. K. Chen, D.-R. Yost, J. M. Knecht, and C. L. Keast, "Floating body effects on the RF performance of FDSOI RF amplifiers," *IEEE International SOI Conference*, Oct. 2005, pp. 44-46.

- [17] J. B. Kuo and K.-W. Su, CMOS VLSI Engineering Silicon-on-Insulator (SOI), Kluwer Academic Publishers, 1998.

- [18] K. Cheng, A. Khakifirooz, P. Kulkarni, S. Kanakasabapathy, S. Schmitz, A. Reznicek, T. Adam, Y. Zhu, J. Li, J. Faltermeier, T. Furukawa, L. F. Edge, B. Haran, S.-C. Seo, P. Jamison, J. Holt, X. Li, R. Loesing, Z. Zhu, R. Johnson, A. Upham, T. Levin, M. Smalley, J. Herman, M. Di, J.Wang, D. Sadana, P. Kozlowski, H. Bu, B. Doris, and J. O'Neill, "Fully depleted extremely thin SOI technology fabricated by a novel integration scheme featuring implant-free, zero-silicon-loss, and faceted raised source/drain," *VLSI Symp. Tech. Dig.*, Jun. 2009, pp. 212–213.

- [19] Sentaurus Process User Guide, Synopsys, Inc., Mountain View, CA, version E-2010.12, Dec. 2010.

- [20] Sentaurus Device User Guide, Synopsys, Inc., Mountain View, CA, version D-2010.03, Mar. 2010.

- [21] A. Asenov, "Random dopant induced threshold voltage lowering and fluctuations in sub 50 nm MOSFETs: a statistical 3D 'atomistic' simulation study," *IOP Semiconductor Science and Technology*, vol. 10, no. 2, pp. 153-158, Feb. 1999.

- [22] A. Asenov, "Simulation of statistical variability in nano MOSFETs," VLSI Symp. *Tech. Dig.*, Jun. 2007, pp. 86-87.

- [23] D. Reid, C. Millar, G. Roy, S. Roy, and A. Asenov, "Analysis of threshold voltage distribution due to random dopants: A 100 000-sample 3-D simulation study," *IEEE Trans. Electron Devices*, vol. 56, no. 10, pp. 2255-2263, Oct. 2009.

- [24] T. Mizuno, J.-I. Okamura, and A. Toriumi, "Experimental study of threshold voltage fluctuation due to statistical variation of channel dopant number in MOSFETs," *IEEE Trans. Electron Devices*, vol. 41, no. 11, pp. 2216-2221, Nov. 1994.

- [25] R. W. Keyes, "Physical limits in digital electronics," *Proc. of the IEEE*, vol. 63, no. 5, pp. 740-767, May 1975.

- [26] C. Shin, "Advanced MOSFET Designs and Implications for SRAM Scaling," Ph.D. dissertation, Dept. Elect. Eng. and Comput. Sci., University of California, Berkeley, CA, 2011.

# Chapter 2 The Characteristics of MOSFET-based Capacitorless DRAM with UTBOX FDSOI Structure

## 2.1 Introduction

Variability in transistor threshold voltage ( $V_T$ ) is now widely recognized as a critical challenge for continued CMOS technology scaling and memory yield [1, 2]. The fully depleted silicon-on-insulator (FDSOI) MOSFET design with a very thin (~10 nm-thick) buried oxide (BOX) layer has been shown to be effective for reducing the impact of transistor parameter variations and random dopant fluctuations (RDF), due to its excellent electrostatic integrity and light body doping [1, 3]. The capacitorless DRAM cell design is a candidate for future high-density embedded memories because of its relatively small layout area (as compared to a conventional SRAM cell) and simple fabrication process [4-6]. Back-gated FDSOI capacitorless DRAM devices have recently been demonstrated with sub-50 nm gate length ( $L_g$ ) [7], and heavy sub-BOX substrate (back gate) doping has been shown to be beneficial for enhanced read margin [8]. In this chapter, the effects of substrate doping concentration and profile on back-gated FDSOI capacitorless DRAM cell performance are investigated via a three-dimensional (3-D) Technology Computer-Aided Design (TCAD) process and device simulation [9, 10] to provide guidance for design optimization.

## 2.2 Device Structure and Operation

The capacitorless DRAM cell structure in this study is essentially a back-gated FDSOI MOSFET. Based on recent publications (*e.g.*, [3]), cell dimensions at the 22 nm

technology node are selected for this study: the Si body thickness and BOX thickness are each set to be 10 nm, the physical gate length is 25 nm, and the equivalent gate oxide thickness (Tox) is 1 nm. The body is undoped, and the sub-BOX substrate underneath the body is doped p-type. The device parameters are summarized in **Table 2.1**.

Four operations are simulated herein for the capacitorless DRAM cell: Write 1, Write 0, Hold, and Read. To form a potential well within the body for hole storage, a negative back bias of -2.5 V is applied. Holes are generated and stored during a Write 1 operation, or removed during a Write 0 operation, by appropriately biasing the other three terminals of the cell (**Table 2.2**). The state of the cell is read-out via the MOSFET current: if holes are stored in the body, then the source potential barrier (hence  $V_T$ ) is lowered so that the Read 1 current is high; if holes are not stored in the body, then the Read 0 current is low. The durations of the program/erase and read operations are each 20 nano seconds (ns).

| Parameter                                 | Value                                                        |

|-------------------------------------------|--------------------------------------------------------------|

| Gate length (Lg)                          | 25 nm                                                        |

| Effective gate length (L <sub>eff</sub> ) | 35.6 nm                                                      |

| Gate oxide thickness (Tox)                | 1 nm                                                         |

| Body thickness (T <sub>Si</sub> )         | 10 nm                                                        |

| BOX thickness (T <sub>BOX</sub> )         | 10 nm                                                        |

| Channel width (W)                         | 32 nm                                                        |

| Spacer width (W <sub>SPACER</sub> )       | 15 nm                                                        |

| Gate work function( $\Phi_M$ )            | 4.45 eV                                                      |

| Channel dopant concentration              | Intrinsic                                                    |

| Source/Drain doping concentration         | 10 <sup>20</sup> cm <sup>-3</sup>                            |

| Substrate dopant concentration            | p-type :10 <sup>12</sup> ~ 10 <sup>20</sup> cm <sup>-3</sup> |

Table 2.1. FD-SOI capacitorless DRAM cell design parameters. Extensions are formed by dopant drive-in from in-situ doped raised source/drain to avoid implant damage to transistor [3].

|                     | W1 (program) | W0 (Erase) | Hold | Read |

|---------------------|--------------|------------|------|------|

| V <sub>gs</sub> (V) | 1.0          | 0.9        | -0.5 | 0.8  |

| V <sub>bg</sub> (V) | -2.5         | -2.5       | -2.5 | -2.5 |

| V <sub>ds</sub> (V) | 2.0          | -0.5       | 0    | 0.6  |

| V <sub>s</sub> (V)  | 0            | 0          | 0    | 0    |

Table 2.2. FD-SOI capacitorless DRAM cell biasing conditions.

## 2.3 Optimization of Substrate Doping

### 2.3.1 Simulation Approach

In capacitorless DRAM, the conventional storage capacitor can be replaced by the body capacitance of a SOI. In this chapter, the basic capacitorless operating mode (MOSFET mode) is focused [11-13]. The concept of MOSFET mode utilizes the floating-body effect of a SOI transistor. In these simulated structures, *Sentaurus Process* is used in order to provide a complete and highly flexible, and process modeling environment [10]. The process parameters follow the 22 nm-technology node with faceted source/drain FDSOI fabrication [14, 15]. The channel and source/drain doping concentrations are the same as each other. Only substrate doping concentrations change.

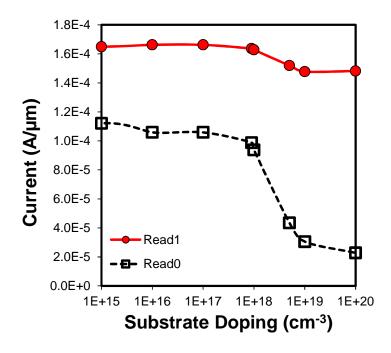

Figure 2.1. Simulated Read 1 and Read 0 currents for a FDSOI capacitorless DRAM cell, as a function of sub-BOX substrate dopant concentration. Read currents are measured at  $1\mu$ s Hold time.

### **2.3.2 Substrate Doping Effect**

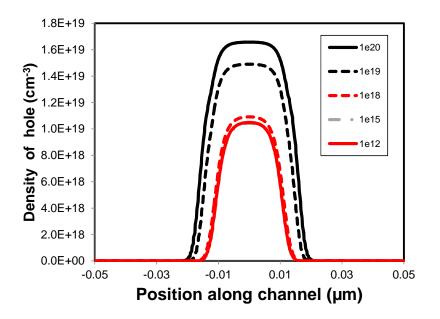

**Fig. 2.1** shows the impact of substrate dopant concentration on the Read 0 and the Read 1 current levels. As p-type concentration is increased in the substrate,  $V_T$  increases due to increased depletion charge [16] and hence the Read 0 current decreases. The Read 1 current is a much weaker function of substrate doping, due to a compensating effect: as the dopant concentration in the substrate increases, the potential well for holes in the body region becomes deeper so that it can store more holes upon a Write 1 operation (**Fig. 2.2**) – but this results in greater lowering of the source potential barrier so that the net difference in 1-state source potential barrier is relatively small. The sensing margin is defined as the difference between Read 1 and Read 0 currents, and it can be seen to increase with substrate doping, consistent with experimental observations [8].

Figure 2.2. Hole density profile within a programmed FDSOI capacitorless DRAM cell in the hold state, for various substrate dopant concentrations (cm<sup>-3</sup>).

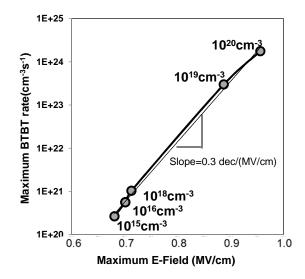

In the hold state, electrons can leak away from the body due to band-to-band tunneling (BTBT), to degrade the cell retention time. This problem is more severe for higher substrate doping due to higher peak electric field at the source/drain junctions (**Fig. 2.3**). **Fig. 2.4** compares the retention characteristics of cells with different substrate doping levels. Negative gate bias and substrate (back gate) bias are applied to hold positive charges in the Hold state as shown in **Table 2.1**. For high substrate doping ( $\geq 10^{19}$  cm<sup>-3</sup>), the sensing margin degrades more rapidly with Hold time even though it is initially higher due to higher BTBT leakage.

Figure 2.3. Maximum band-to-band tunneling (BTBT) rate *vs.* peak electric field within a programmed FDSOI capacitorless cell in the hold state. The corresponding substrate doping concentrations for various peak electric field strengths are indicated.

Figure 2.4. Retention characteristics for a FDSOI capacitorless DRAM cell, using various substrate dopant concentrations (cm<sup>-3</sup>). Although higher substrate doping results in larger current sense margins at short retention times, the retention time is degraded due to increased BTBT.

#### 2.3.3 Random Dopant Fluctuations (RDF)

Another issue for high substrate doping is the  $V_T$  variation induced by random dopant fluctuations (RDF), since the substrate doping affects  $V_T$  when the BOX is thin [2]. 3-dimension (3-D) Kinetic Monte Carlo (KMC) process simulations [9] were used to

examine the impact of RDF in this work. The simulated process uses low-temperature, zero-silicon-loss epitaxial growth to form faceted *in-situ*-doped  $(10^{20} \text{ cm}^{-3})$  raised-source/drain regions. Dopants are diffused to form the lightly doped source/drain extensions to reduce series resistance with minimal increase in sidewall gate capacitance [3]. **Fig. 2.5** shows one instance of a simulated structure. In order to distinguish the effect of substrate RDF, all of the simulated structures have the same source and drain atomistic dopant profiles (to eliminate the effects of source/drain RDF).

Figure 2.5. Kinetic Monte Carlo (KMC) simulation: (a) FDSOI capacitorless DRAM cell (W = 32 nm) structure showing dopant particle distribution, and (b) cross-sectional doping contour map.

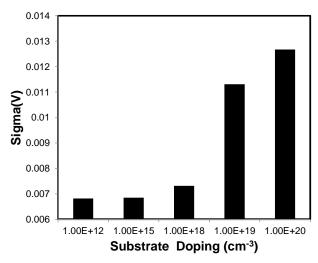

Figure 2.6. Standard deviation of threshold voltage distribution due to RDF-induced variation, for various substrate dopant concentrations.

The standard deviation of the V<sub>T</sub> distribution ( $\sigma_{VT}$ ) extracted from these simulations ( $I_{ds}$ -V<sub>gs</sub> curves for Read 0 bias conditions), is plotted in **Fig. 2.6**, using various nominal substrate dopant concentrations. Clearly,  $\sigma_{VT}$  becomes significant for substrate doping  $\geq 10^{19}$  cm<sup>-3</sup>. Given the tradeoff between sensing margin and retention time, and RDF-induced V<sub>T</sub> variation, the optimal substrate doping appears to be ~10<sup>18</sup> cm<sup>-3</sup>.

#### 2.4 Selective Well Design

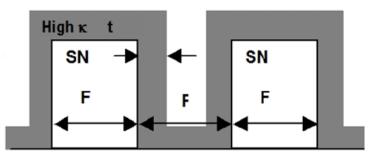

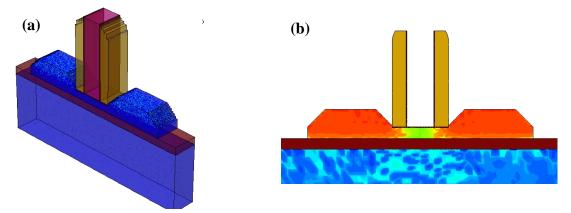

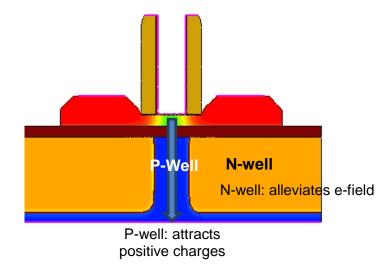

As noted above, high peak electric fields at the source/drain junctions result in degraded retention time due to BTBT leakage. If the p-type substrate doping is lowered - or even made of the opposite type (n-type) - in the regions directly beneath the source/drain junctions, then this problem can be somewhat mitigated. Therefore, a selective well design is proposed herein to improve the retention behavior of the FDSOI capacitorless DRAM cell: p-type doping is used in the substrate beneath the channel region, while n-type doping  $(10^{18} \text{ cm}^{-3})$  is used beneath the source and drain regions as shown in **Fig. 2.7**. Such a structure can be formed in a straightforward manner by self-aligned deep ion implantation of n-type dopants. In **Fig. 2.8** the electric field distribution within the SOI film in the Hold 0 state is compared for uniform p-type substrate doping *vs*. selective p-well doping. The peak electric field is reduced for the selective well structure and BTBT leakage is reduced as shown in **Fig. 2.8(b)**.

The effect of the width of the selective well is studied via simulation (**Fig. 2.9**). Although a wider p-well is more effective for retaining holes (positive charges), it can result in larger peak electric field, which degrades retention time. An excessively narrow p-well also results in short retention time due to an insufficient well for retaining holes. As is evident in **Fig. 2.10**, the optimal width of the p-well is comparable to the gate length, for which the retention time exceeds 100 ms. This represents a ~9% improvement over the uniform substrate doping case.

Figure 2.7. Selective well cross section view. The p-well has a role in attracting positive charges. The n-well alleviates the peak electric field at the source/drain junction, which improves retention time.

Figure 2.8. (a) Electric field profile and (b) BTBT rate within the SOI film, 1nm above the BOX, in the Hold 0 state. The n-wells are electrically floating within the p-type substrate. The p-type substrate (p-well) is biased at -2.5 V, the source and drain regions are biased at 0V, and the gate is biased at -0.5 V.

Figure 2.10. Comparison of retention time (for 10  $\mu$ A/ $\mu$ m minimum sensing margin) for various widths of the p-well centered beneath the channel region.

### 2.5 Summary

The peak doping concentration and lateral doping profile within the substrate of a FDSOI capacitorless DRAM cell can greatly affect the cell retention time. As the peak doping concentration increases, the sensing current increases but at the cost of reduced retention time due to BTBT and increased  $V_T$  variability due to RDF. The optimal peak doping concentration is found to be ~10<sup>18</sup> cm<sup>-3</sup>. A selective well structure (the p-well only underneath the channel region) can be used to reduce the peak electric field at the source/drain junctions in order to improve retention time by ~9% for 25 nm gate length.

## 2.6 References

- Weber, O. Faynot, F. Andrieu, C. Buj-Dufournet, F. Allain, P. Scheiblin, J. Foucher, N. Daval, D. Lafond, L. Tosti, L. Brevard, O. Rozeau, C. Fenouillet-Beranger, M. Marin, F. Boeuf, D. Delprat, K. Bourdelle, B.-Y. Nguyen, and S. Deleonibus, "High immunity to threshold voltage variability in undoped ultra-thin FDSOI MOSFETs and its physical understanding," *IEDM Tech. Dig.*, Dec. 2008, pp. 1-4.

- [2] S. Borkar, T. Karnik, S. Narendra, J. Tschanz, A. Keshavarzi, and V. De, "Parameter variations and impact on circuits and microarchitecture," *Proc. Design Autom. Conf.*, 2003, pp. 338–342.

- [3] C. Shin, M. H. Cho, Y. Tsukamoto, B.-Y. Nguyen, B. Nikolić, and T.-J. K. Liu, "SRAM yield enhancement with thin-BOX FD-SOI," *Proc. IEEE Int. SOI Conf.*, Oct. 2009, pp. 1–2.

- [4] S. Okhonin, M. Nagoga, J. M. Sallese, and P. Fazan, "A SOI capacitor-less 1T-DRAM concept," *Proc. IEEE Int'l SOI Conf.*, Oct. 2001, pp. 153-154.

- [5] R. Ranica, A. Villaret, C.Fenouillet-Beranger, P. Malinge, P. Mazoyer, P. Masson, D. Delille, C. Charbuillet, P. Candelier and T. Skotnicki, "A capacitor-less DRAM cell on 75nm gate length, 16nm thin Fully Depleted SOI device for high density embedded memories," *IEDM Tech. Dig.*, Dec. 2004, pp. 277–280.

- [6] D. Fisch, "Innovative Approach to drive Floating Body Z-RAM<sup>®</sup> Embedded Memory to 32 nm and beyond, "*Proc. IEEE Int'l SOI Conf.*, Oct. 2007, pp. 101-102.

- [7] I. Ban, U. E. Avci, D. L. Kencke, P. Tolchinsky, and P.L.D. Chang, "Integration of Back-Gate Doping for 15-nm Node Floating Body Cell (FBC) Memory," *IEEE Symp. VLSI Tech. Dig.*, Jun. 2010, pp. 159 – 160.

- [8] S. Kim, R. J. Tseng, W. Rachmady, B. Jin, U. Shah, I. Ban, U. E. Avci, and P.L.D. Chang, "Silicon on Replacement Insulator (SRI) Floating Body Cell (FBC) Memory," *IEEE Symp. VLSI Tech. Dig.*, Jun. 2010, pp. 165 – 166.

- [9] Sentaurus Device User Guide, Synopsys, Inc., Mountain View, CA, version D-2010.03, Mar. 2010.

- [10] Sentaurus Process User Guide, Synopsys, Inc., Mountain View, CA, version E-2010.12, Dec. 2010.

- [11] H.-J. Wann and C. Hu, "Capacitorless DRAM Cell on SOI Substrate," *IEDM Tech. Dig.*, Dec. 1993, pp. 635 638.

- [12] S. Okhonin, M. Nagoga, E. Carman, R. Beffa, and E. Faraoni, "New Generation of Z-RAM," *IEDM Tech. Dig.*, Dec. 2007, pp. 925-928.

- [13] I. Ban, U. E. Avci, D. I. Kencke, P. L. D. Chang, "Scaled Floating Body Cell (FBC) Memory with High-k+Metal Gate on Thin-Silicon and Thin-BOX for 16-nm Technology Node and Beyond," *VLSI Symp. Circuit Dig.*, Jun. 2008, pp. 92-93.

- [14] K. Cheng, A. Khakifirooz, P. Kulkarni, S. Kanakasabapathy, S. Schmitz, A. Reznicek, T. Adam, Y. Zhu, J. Li, J. Faltermeier, T. Furukawa, L. F. Edge, B. Haran, S.-C. Seo, P. Jamison, J. Holt, X. Li, R. Loesing, Z. Zhu, R. Johnson, A. Upham, T. Levin, M. Smalley, J. Herman, M. Di, J.Wang, D. Sadana, P. Kozlowski, H. Bu, B. Doris, and J. O'Neill, "Fully depleted extremely thin SOI technology fabricated by a

novel integration scheme featuring implant-free, zero-silicon-loss, and faceted raised source/drain," VLSI Symp. Tech. Dig., Jun. 2009, pp. 212–213.

- [15] K. Cheng, A. Khakifirooz, P. Kulkarni, S. Ponoth, J. Kuss, D. Shahrjerdi, L. F. Edge, A. Kimball, S. Kanakasabapathy, K. Xiu, S. Schmitz, A. Reznicek, T. Adam, H. He, N. Loubet, S. Holmes, S. Mehta, D. Yang, A. Upham, S.-C. Seo, J. L. Herman, R. Johnson, Y. Zhu, P. Jamison, B. S. Haran, Z. Zhu, L. H. Vanamurth, S. Fan, D. Horak, H. Bu, P. J. Oldiges, D. K. Sadana, P. Kozlowski, D. McHerron, J. O'Neill, B. Doris, "Extremely thin SOI (ETSOI) CMOS with record low variability for low power system-on-chip applications," *IEDM Tech. Dig.*, Dec. 2009, pp. 1-4.

- [16] J. B. Kuo and K.-W.Su, CMOS VLSI Engineering Silicon-on-Insulator, Kluwer Academic Publishers, 1998.

# Chapter 3 Design Optimization of BJT-based Thin-Body Capacitorless DRAM Cell

#### **3.1 Introduction**

The concept of a single-transistor dynamic random access memory (DRAM) cell was proposed to address the challenge of reducing memory cell area with reduction in minimum feature size [1]. The bipolar junction transistor (BJT)-based operation (BJT mode) of a thin-body capacitorless DRAM cell is advantageous compared to the metal-oxide-semiconductor field-effect transistor (MOSFET)-based operation (MOSFET mode) because it provides for higher current sensing margin and longer data retention times [2]. However, band-to-band tunneling (BTBT) leakage due to high internal electric field can degrade the retention time in scaled BJT-based cells [3]. Thus, in this chapter, methods for improving the retention time of a scaled BJT mode capacitorless DRAM cell are investigated via technology computer-aided design (TCAD) simulation [4, 5]. Kinetic Monte Carlo (KMC) simulations then are used to compare the effects of random dopant fluctuations (RDF) on the read current distributions of cells designed for the BJT mode *vs*. the MOSFET mode.

## 3.2 Cell Design and TCAD Simulation

The capacitorless DRAM cell in this study comprises a back-gated thin-body MOSFET. The initial values of various cell design parameters (**Table 3.1**) are selected as appropriate for the 22 nm complementary metal–oxide–semiconductor (CMOS) technology node [6]. The simulated fabrication method uses a low-temperature, zero-silicon-loss epitaxial growth process to form faceted in-situ-doped ( $10^{20}$  cm<sup>-3</sup>) raised-source/drain regions – from which dopants are diffused (at 1473 K for 0.08 s) to form lightly doped source/drain extensions – in order to reduce series resistance with minimal increase in sidewall gate

capacitance. [7]. The Sentaurus software package [4, 5] is used to simulate the various cell operations (*i.e.*, Write, Hold, and Read) at room temperature (300 K), assuming 3  $\mu$ s minority-carrier lifetime within the body. The operating voltages for BJT mode and MOSFET mode are summarized in **Table 3.2** and **Table 3.3** respectively: W1 denotes the program operation (*i.e.*, writing data 1 into a cell); W0 indicates the erase operation (*i.e.*, writing data 0 into a cell); *Hold* refers to data retention, and *Read* signifies the sensing of stored data. The durations of the Write and Read operations are each 20 ns.

| Gate length (nm)                                         | 25 or 41         |

|----------------------------------------------------------|------------------|

| Gate-sidewall spacer width (nm)                          | 13-25            |

| Gate-oxide thickness (nm)                                | 1 or 3           |

| Body thickness (nm)                                      | 10               |

| Buried oxide thickness (nm)                              | 10               |

| Body dopant concentration: intrinsic (cm <sup>-3</sup> ) | 0                |

| Substrate dopant concentration (cm <sup>-3</sup> )       | 10 <sup>18</sup> |

| Gate work function (eV)                                  | 4.6              |

Table 3.1. Capacitorless DRAM cell design parameters

|                 | W1  | W0   | Hold | Read |

|-----------------|-----|------|------|------|

| $V_{gs}$        | -1  | 0    | -1.7 | -1   |

| V <sub>bg</sub> | 2.5 | 2.5  | 2.5  | 2.5  |

| V <sub>ds</sub> | 1.7 | -0.5 | 0    | 1.2  |

| Vs              | 0   | 0    | 0    | 0    |

Table 3.2. Operating voltages for BJT mode (unit: Volts).

|                            | W1   | W0   | Hold | Read |

|----------------------------|------|------|------|------|

| $\mathbf{V}_{\mathbf{gs}}$ | 1    | 0.9  | -0.5 | 0.8  |

| $\mathbf{V}_{bg}$          | -2.5 | -2.5 | -2.5 | -2.5 |

| V <sub>ds</sub>            | 2    | -0.5 | 0    | 0.6  |

| $\mathbf{V}_{\mathbf{s}}$  | 0    | 0    | 0    | 0    |

Table 3.3. Operating voltages for MOSFET mode (unit: Volts).

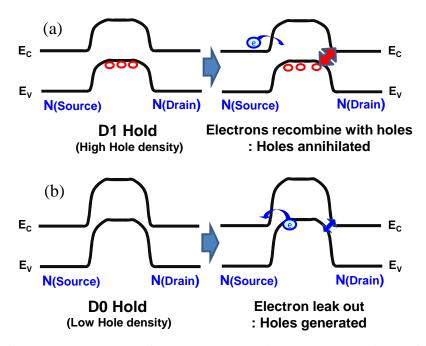

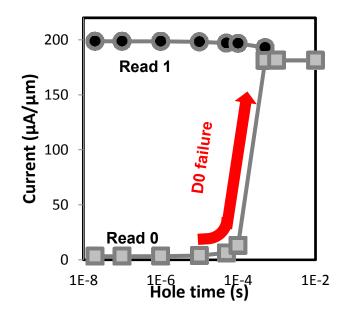

#### **3.3** Mechanism of Data Retention Failure

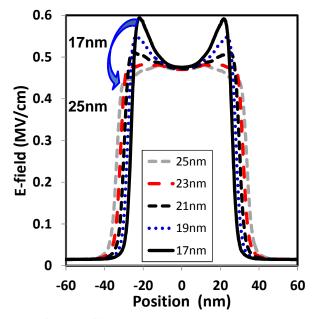

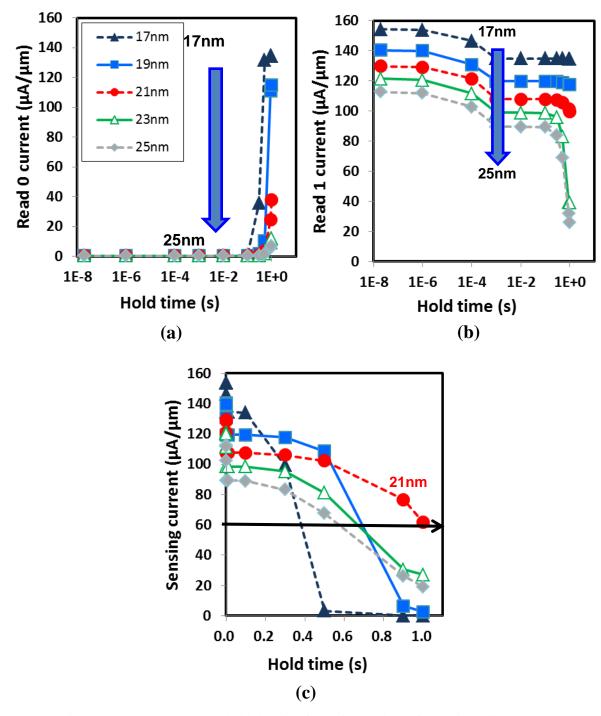

When a BJT mode cell is in the Hold 1 state, holes are stored below the gate oxide. This increases the vertical electric field (e-field), which is a concern for gate-oxide reliability. **Fig. 3.1** shows Hold state electric field contour maps for a cell with 1 nm gate-oxide thickness ( $T_{OX}$ ) and 13 nm gate-sidewall spacer width ( $W_{spacer}$ ). The peak electric field at the gate oxide is almost 16 MV/cm in the Hold 1 state (**Fig. 3.2**). A thicker oxide (3 nm) should be used to guarantee a gate-oxide lifetime of more than 10 years [8]. This is possible because the BJT mode does not require a very thin gate oxide [9].