# **Chapter 1: Introduction**

# 1.1 Benefits of MOSFET Scaling

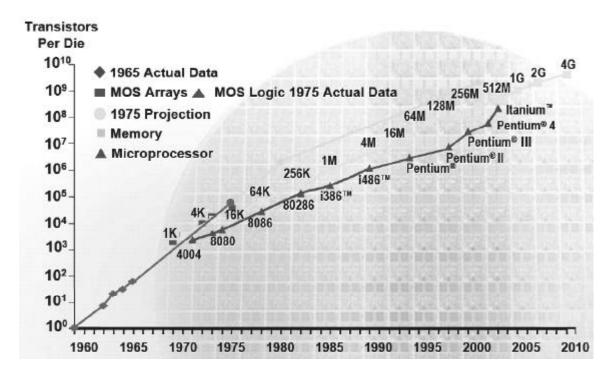

Computing power has increased dramatically over the decades, enabled by significant advances in silicon integrated circuit (IC) technology led by the continued miniaturization of the MOS transistor. The rapid progress in the semiconductor industry has been driven by improved circuit performance and functionality together with reduced manufacturing costs. Since the 1960s, MOS transistor dimensions have been shrinking 30% every 3 years, as predicted by Moore's law [1] depicted in Figure 1.1 [2] and scaling has in fact accelerated recently [3].

While Moore's Law only describes the rate of increase in transistor density, reduction of the physical MOS device dimensions has improved both circuit speed and density in the following ways: a) Circuit operational frequency increases with a reduction in gate length,  $L_G$ , as ~  $1/L_G$ ; allowing for faster circuits, b) Chip area decreases ~  $L_G^2$ ; enabling higher transistor density and cheaper ICs. c) Switching power density ~ constant; allows lower power per function or more circuits at the same power.

Device scaling has been a relatively straightforward affair thus far, but physical limits are fast being approached, and new materials and device structures are needed to continue scaling trends.

Figure 1.1: Moore's law of scaling. The number of transistors on a chip has been increasing exponentially [1, 2]

## 1.2 Issues in Planar Bulk-Si MOSFET Scaling

The planar bulk-silicon MOSFET has been the workhorse of the semiconductor industry over the last 40 years. However, the scaling of bulk MOSFETs becomes increasingly difficult for gate lengths below  $\sim$ 20nm (sub-45 nm half-pitch technology node) expected by the year 2009. As the gate length is reduced, the capacitive coupling of the channel potential to the source and drain increases relative to the gate, leading to significantly degraded short-channel effects (SCE). This manifests itself as a) increased off-state leakage, b) threshold voltage ( $V_{TH}$ ) roll-off, i.e. smaller  $V_{TH}$  at shorter gate lengths, and c) reduction of  $V_{TH}$  with increasing drain bias due to a modulation of the source-channel potential barrier by the drain voltage, also called drain-induced barrier lowering (DIBL). In order to maintain the relatively strong gate control of the channel

potential in bulk devices, various technological improvements such as ultra-thin gate dielectrics, ultra-shallow source/drain junctions, halo implants and advance channel dopant profile engineering techniques such as super-steep retrograde wells have been necessary. Each of these technologies is now approaching fundamental physical limitations which may, in turn, limit further scaling of device dimensions.

In MOS devices, the gate dielectric thickness is single most important device dimension to enable device scaling and has also been the most aggressively scaled one. A thin gate dielectric increases capacitive coupling from the gate to the channel, thereby reducing the source/drain influence on the channel. A larger gate capacitance also leads to a larger inversion charge density, or increased ON-state drive current. However, gate dielectrics are already so thin that quantum mechanical direct tunneling through them results in significant gate leakage currents below  $\sim 20 \, \text{Å}$ . The use of alternative high-  $\kappa$  gate dielectric materials can provide a small effective oxide thickness to maintain adequate gate control needed for  $L_G$  scaling while providing a large physical barrier to gate-oxide tunneling, thereby reducing gate leakage.

Reduction of the source/drain extension junction depth directly decreases capacitive coupling of the drain to the channel, thus also reduces drain-induced short-channel effects. Shallow source/drain junction formation requires that low-energy ion implantation together with low thermal budget dopant activation to minimize dopant diffusion. The downside to this is the increase in the parasitic series resistance of the source and drain extension regions. Raised source/drain technologies can alleviate the extrinsic resistance problem while maintaining shallow junctions. The contact resistance associated with the metallic contacts to the source/drain regions is another source for

parasitic series resistance and is expected to dominate the total parasitic resistance of the device.

In order to scale bulk-Si transistors, heavy body doping is also necessary to eliminate leakage paths far from the gate dielectric interface and to increase back-gate (substrate) control of the body. For sub-100nm gate length devices, a strong halo implant is generally used to suppress sub-surface leakage, but this tends to increase the average channel doping in small L<sub>G</sub> devices. However, high channel doping concentration, however, reduces carrier mobility due to impurity scattering and increased transverse electric field, increases subthreshold slope, enhances band-to-band tunneling leakage, and increases depletion and junction capacitances. These factors may combine to significantly degrade device performance.

In summary, from a device design point of view, in order to achieve good electrostatic integrity or good control of short-channel effects (SCE), the gate dielectric thickness,  $T_{OX}$ , the source/drain junction depth,  $X_J$ , and the channel depletion depth  $X_{DEP}$ , need to be scaled down. The scale length for a bulk device,  $I_{BULK}$ , is an indication of how short L<sub>G</sub> can be made before the SCE are excessive, and is quantitatively expressed in Eq. 1-1. For good electrostatic control, the minimum  $L_G$  should be no less than ~  $5\boldsymbol{I}_{BULK}$ . [4]  $I_{BULK} = 0.1 (T_{OX} X_J X_{DEP}^2)^{1/3}$

For a bulk MOSFET, gate leakage limits

$$T_{OX}$$

scaling,  $X_{DEP}$  scaling is limited to about 10 nm due to substrate-to-drain band-to-band tunneling current limitations on body doping, and  $X_J$  is limited by process limits for forming ultra shallow junctions with abrupt doping profiles. Experimental bulk MOSFETs have been demonstrated down to 5nm  $L_G$

Eq. 1-1

especially for low power applications. Continued device scaling will require new materials and/or alternative MOSFET structures. Therefore bulk MOSFET scaling is becoming increasingly harder and new transistor designs offering better scalability are needed. These are introduced in the next section.

The IC industry has started to deploy circuit design and architectural techniques such as multiple cores and multiple threads that exploit parallelism to improve the overall chip performance, enhance the chip functionality while maintaining chip power density and total chip power dissipation at a manageable level. With more than one central processing unit (CPU) core on chip, the cores can each be clocked at a lower frequency while still providing for better overall chip performance. In addition, ever more cache memory is being added onto the processor chip in order to minimize the system performance penalty associated with finite-cache effects. With the shift to multi-core processing becoming increasingly important, the performance of each core can be correspondingly lower, meaning that lower leakage (vs. high performance) MOSFET designs will become increasingly important because the desired overall chip performance can be achieved through parallelism.

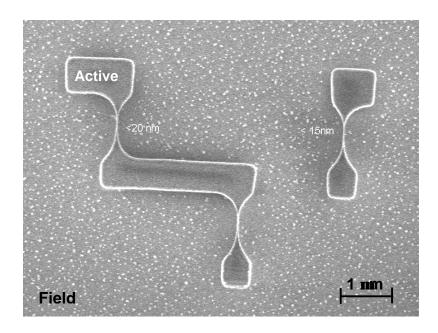

#### 1.3 Process-induced Variations

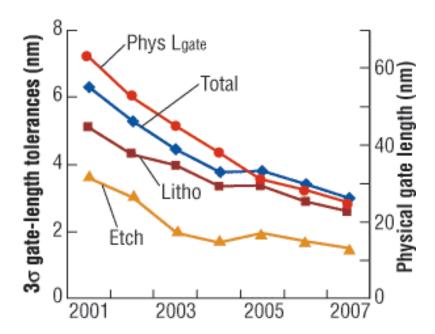

Control of critical dimensions (CDs) such as  $L_G$  continues to be a difficult challenge, as the physical gate length is considerably smaller than the lithography printed linewidth. Controlling the lithography and etch processes to achieve critical dimension control to within 10% (3s), as prescribed in the 2003 International Roadmap for Semiconductors (ITRS) [7] is almost universally unachievable, so the CD tolerance has

been increased to 12% (3s) in 2005[6]; there might be a need to relax this requirement further in the future.

In order to limit the impact of variations, the semiconductor is industry is actually using slightly larger physical gate lengths than those specified in the *ITRS*, especially for memory applications [8]. The slowing down of L<sub>G</sub> scaling may be unavoidable in the future since the control of process variables does not track the scaling of minimum feature sizes. This is of particular importance for memory arrays, because if the desired degree of dimensional control were not achievable, design margins would need to be relaxed to achieve large functional memory arrays. This slowdown in technology scaling will probably be application specific, and is unavoidable if process-control is not robust enough.

Figure 1.2: Changes in physical gate length, lithography tolerance, and etch tolerance over the years. The physical gate length tolerance has been relaxed to 12%, and this trend is expected to continue. [9]

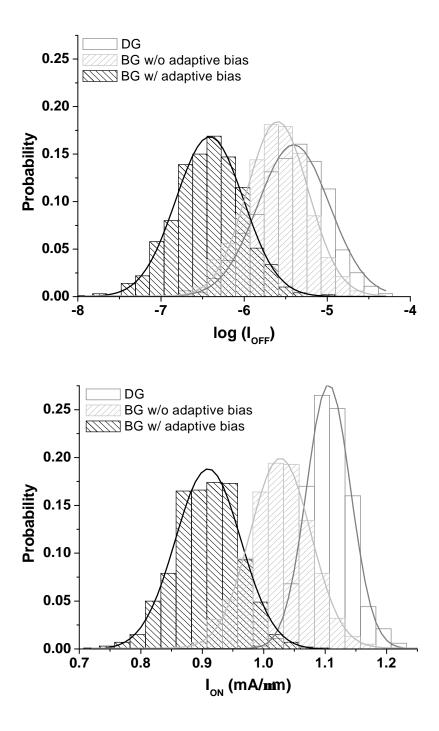

While advanced process control can minimize systematic shifts in the CD, the role of random variations arising from statistical dopant fluctuations and line edge roughness is expected to increase, so that variations will impact the overall power dissipation and performance [10]. Therefore, statistical treatment of random variation of circuits (statistical design) is becoming increasingly important. New transistor structures should have better immunity to process variations, and devices with tunable  $V_{TH}$  are beneficial to counter any systematic shifts in transistor characteristics.

## 1.4 Thin-body MOSFETs

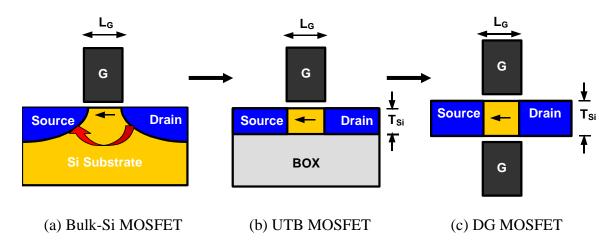

Figure 1.3: Advanced transistor structures such as the UTB and the DG-MOSFET eliminate sub-surface leakage paths and extend the scalability of Si CMOS technology.

As the bulk MOSFET is scaled down, the control of short channel effects becomes increasingly difficult leading to increased subthreshold leakage current. This is because the source/drain influence over the channel potential becomes significant relative to the gate control.

From Eq. 1-1, it is clear that if  $X_J$  and  $X_{DEP}$  can be reduced aggressively, it is possible to scale the MOSFET down to very small  $L_G$ . This is precisely what is done in

the case of ultra-thin body (UTB) silicon-on-insulator (SOI) devices, where  $X_J$  and  $X_{DEP}$ are physically limited to the thickness of an ultra-thin silicon film. Eq. 1-1 only qualitatively describes the scaling behavior of UTB, and better models are introduced later. Thus, the scalability of MOS devices can be improved by using an ultra thin silicon body such that all points in the silicon channel are close enough to the gate and well controlled by it, thereby eliminating sub-surface leakage currents. The conventional fully depleted SOI MOSFET (with a thick body) is known to have worse short-channel effects than bulk MOSFETs and partially depleted SOI MOSFETs [11]. To achieve good short channel control, T<sub>Si</sub> must be smaller than the depletion width or junction depth of a comparable bulk device with high channel doping. The leakage path in a UTB device is along the buried-oxide interface, furthest away from the gate. The thinner the silicon body is made, the larger is the leakage reduction from eliminating sub-surface leakage paths far away from the gate, and the better the device scalability. Also, UTB devices do not have the floating body effects seen in thick (partially-depleted) SOI devices (PDSOI), because there is no floating quasi-neutral region in the body.

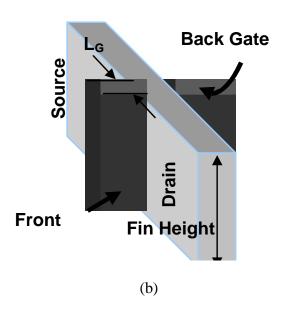

The body thinness requirement can be relaxed by adopting the double-gate (DG) MOSFET structure shown in Figure 1.3c, in which two gates control the channel potential. The DG-FET achieves better gate control and thereby has improved SCE for a given body thickness [12]. The body thickness can be twice that of a single-gated UTB device, in order to achieve the same degree of SCE. The DG MOSFET does not suffer from electric field penetration from the source/drain to the channel through the buried oxide and is therefore more scalable. The relaxed thinness requirement for the body is highly desirable from a manufacturability point of view, since the formation of a uniform

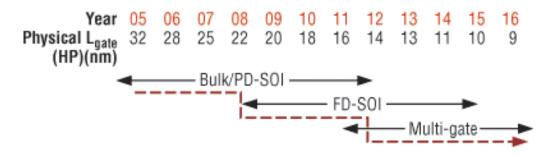

ultra-thin film can pose major technological challenges. Simulation results show that a DG MOSFET has the best scalability, down to sub-10nm  $L_G$  devices [13]. The improved scalability of thin-body devices makes them attractive for future generations of CMOS technology and so they have been included in the International technology roadmap for semiconductors (ITRS) (see Figure 1.4) [6].

Figure 1.4: Advanced transistor designs may be necessary to meet performance requirements. Potential timetable for the adoption of advanced device structures to meet performance requirements. [6, 9]

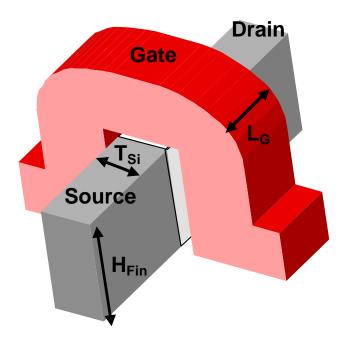

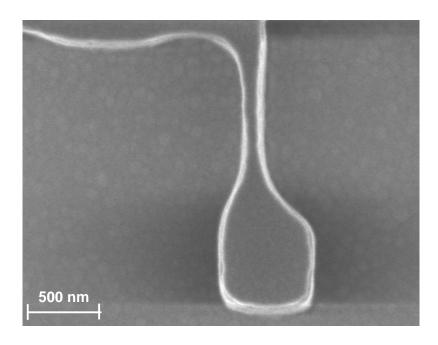

UTB devices can be implemented in a straightforward manner as planar single gate fully depleted silicon-on-insulator (FDSOI) devices [14-19]. While the planar double-gate device has been demonstrated [20], the fabrication of a planar double-gate FET with a bottom gate that is aligned to the top gate and source/drain regions imposes numerous process challenges. Among all DG structures proposed so far, the FinFET (Figure 1.5) is the most manufacturable because it eliminates the need for the bottom gate by rotating the channel by 90 and placing the gate electrodes on the two sidewalls of the silicon fin [21-23]. Independent gate FinFETs, in which the front and back-gate electrodes can be independently biased have been demonstrated as well [24, 25]. The front gate can be used to switch the device, whereas the back-gate can be used to set the

correct  $V_{TH}$ . The back-gate is as strong as the front gate, and therefore the device has degraded sub-threshold slope and transconductance due to a capacitive division of the channel potential between the two gates, however.

Figure 1.5: The FinFET consists of a thin Si fin, with the gate running over the fin in a self-aligned fashion. The gate controls the channel along the sidewalls of the fin and the width of the channel is defined by twice the height of the fin,  $H_{FIN}$ .

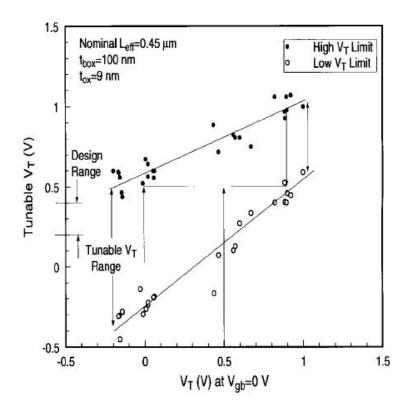

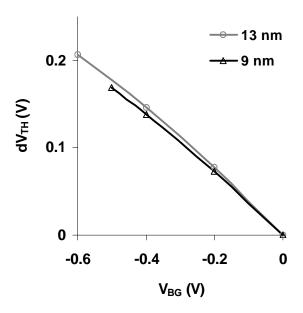

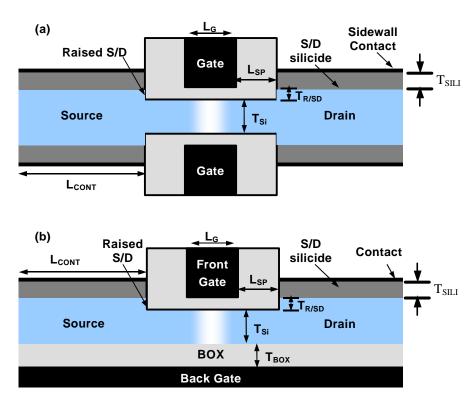

The planar FDSOI MOSFET can been extended to include a conducting electrode underneath the buried oxide (BOX) layer to form a second gate to control the channel from below [26]. This ground plane or the back-gate acts as a second gate to shield the field penetration from the drain into the channel, and improves SCE. In a way, it serves the role of the retrograde doping in a bulk MOSFET, by raising the body backside potential and by terminating drain electric fields [12]. In addition, the BOX eliminates source/drain-to-substrate depletion capacitance. In order to prevent electric field penetration through the BOX, the BOX layer should be thin. Another benefit of a thin

BOX is the "back-gate effect," similar to the "body effect" in bulk-Si devices, wherein the  $V_{TH}$  can be tuned by the back-gate voltage (Figure 1.6). However, the subthreshold slope and the transconductance are degraded due to the capacitive division of the channel potential between the front- and the back-gate potentials.

Figure 1.6: Back-gate effect in BG-FDSOI device showing  $V_{TH}$  tunability. The upper and lower limits of the tunable  $V_{TH}$  range are set by the back interface entering either inversion or accumulation.

While the early FinFET devices were fabricated on SOI wafers, FinFETs on bulk-Si wafers have been demonstrated as well [27, 28]. Bulk-FinFETs have the advantages of being potentially cheaper and can be easily integrated with conventional bulk-Si CMOS technology. Bulk FinFETs combine the benefits of good leakage and short-channel control together with a cheaper manufacturing process, making them attractive for high-density memory applications.

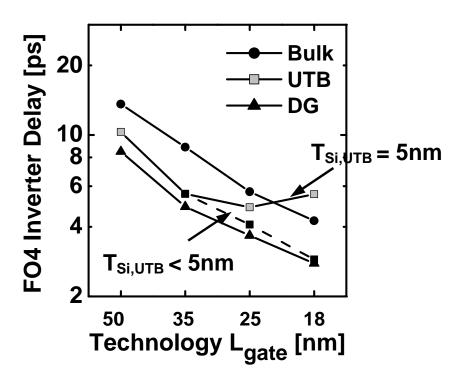

Figure 1.7: DG and UTB devices show better delay than planar bulk devices. The improved performance is due to a combination of improved subthreshold swing, higher carrier mobility, and reduced inversion capacitance and parasitic capacitances.

The main benefits of thin body devices are improved transistor subthreshold swing due to greatly improved gate control, improved channel mobility due to reduced transverse electric field, reduced parasitic capacitances from the absence of depletion capacitances, leading to improved speed, and reduced power consumption. While the FinFET shows the largest performance benefits, the UTB device shows slightly degraded subthreshold swing and degraded ON-currents resulting in larger gate delays (Figure 1.7). [29]. The BG-FDSOI device, with its large back-gate effect and nonideal subthreshold swing, is expected to be slower than FinFET. However, it has the benefit of adaptive V<sub>TH</sub> control, which is a promising way to limit the effect of variations.

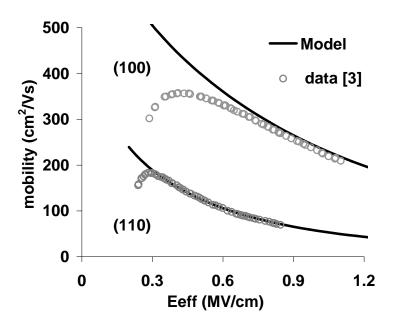

Strained Si technology has been very successful in boosting the performance of both NMOS and PMOS devices, through enhancement in carrier mobilities. Popular

approaches consist of local channel stressing from uniaxial stress induced by Si<sub>1-x</sub>Ge<sub>x</sub> source/drain regions for PMOS devices and from global stress induced by capping layers formed after gate patterning. While NMOS devices primarily benefit from tensile stress, compressive stress is beneficial in PMOS devices. The effect of biaxial and uniaxial stresses on transistor performance is now starting to be well understood [30]. UTB and FinFET devices can each benefit from a combination of local and global stresses. While it is harder to implement uniaxial stress from source/drain regions using Si<sub>1-x</sub>Ge<sub>x</sub> regions, stressed capping layers and gate electrode induced stress can be beneficial for boosting performance in FinFET devices [31, 32].

The main challenge with bringing UTB and FinFETs into manufacturing is the ability to form thin silicon channels with very good thickness uniformity. Fluctuations in the body thickness can cause spread in the  $V_{TH}$  and other device characteristics. Series resistance is a big source of performance degradation in FDSOI devices and FinFETs, and so technologies such as raised source/drain achieved through selective epitaxy or deposition are needed to make low resistance contacts [12]. These technologies have been investigated and process solutions have been identified. [17, 23]

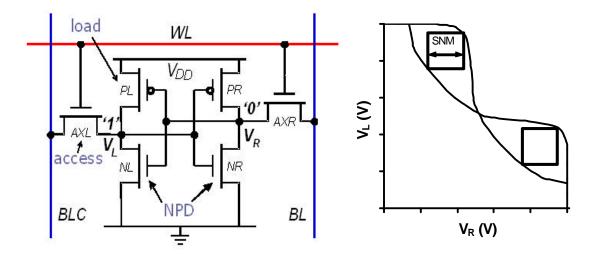

## 1.5 SRAM Scaling Issues

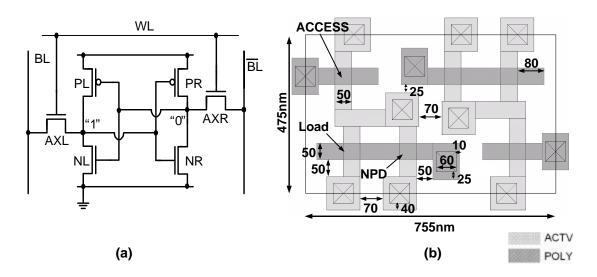

Static random access memory (SRAM) is by far the dominant form of embedded memory found in today's integrated circuits (ICs) occupying as much as 60-70% of the total chip area and about 75%-85% of the transistor count in some IC products. The most commonly used memory cell design uses six transistors (6-T) to store a bit, so all of the issues associated with MOSFET scaling apply to scaling of SRAM. As memory will continue to consume a large fraction of the area in many future IC chips, scaling of

memory density must continue to track the scaling trends of logic. [33]. Statistical dopant fluctuations, variations in oxide thickness, and line-edge roughness increase the spread in transistor threshold voltage and thus the on- and off- currents as the MOSFET is scaled down in the nanoscale regime [34]. Increased transistor leakage and parameter variations present the biggest challenges for the scaling of 6-T SRAM memory arrays.

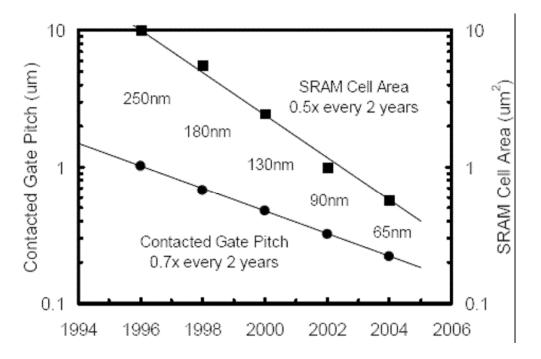

Figure 1.8: SRAM cell size has been scaling at ~0.5 x per generation [35], but it might slow down due to lack of cell robustness caused by process induced variations.

The functionality and density of a memory array are its most important properties. Functionality is guaranteed for large memory arrays by providing sufficiently large design margins (to be able to be read without changing the state, to hold the state, to be writable and to function within a specified timeframe), which are determined by device sizing (channel widths and lengths), the supply voltage and, marginally, by the selection of transistor threshold voltages. Increase in process-induced variations results in a decrease in SRAM read and write margins, which prevents the stable operation of the

memory cell, and is perceived as the biggest limiter to SRAM scaling. The 6-T SRAM cell size, thus far, has been scaled aggressively by ~0.5X every generation (Figure 1.8), however it remains to be seen if that trend will continue. Since the control of process variables does not track the scaling of minimum features, design margins will need to be increased to achieve large functional memory arrays. Moving to more lithography friendly regular layouts with gate lines running in one direction, has helped in gate line printability [8], and could be the beginning of more layout regularization in the future. Also, it might become necessary to slow down the scaling of transistor dimensions to increase noise margins and ensure functionality of large arrays, i.e. tradeoff cell area for SRAM robustness. [33].

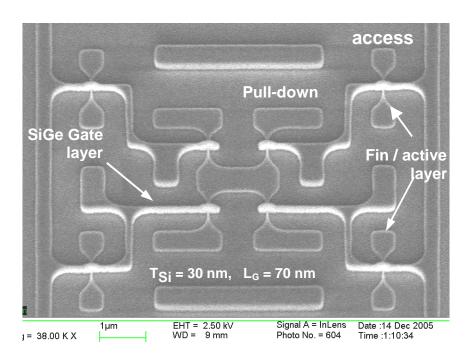

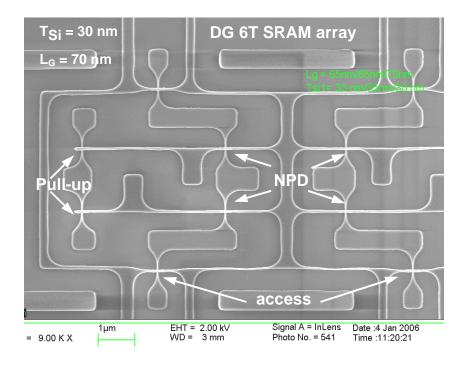

SRAM cells based on advances transistor structures such as the planar UTB FETs and FinFETs have been demonstrated [36-40] to have excellent stability and leakage control. Some techniques to boost the SRAM cell stability, such as dynamic feedback [33], are best implemented using FinFET technology, because there is no associated layout area or leakage penalty. FinFET-based SRAMs are attractive for low-power, low-voltage applications.

## 1.6 Summary

MOS technology has followed Moore's law for over four decades with the continual shrinking of transistor dimensions to increase the number of transistors on an integrated chip at an exponential rate. Transistors typically become faster and consume less power with each new process technology generation, leading to overall performance improvements. Unfortunately, due to fundamental physical limits to scaling, the era of conventional linear scaling of transistor dimensions has ended. Power dissipation and

process-induced variations are big issues for continued scaling of bulk-Si MOSFETs in future generations. Improvements in transistor density, performance and power consumption together with high yield will become harder to achieve. Advanced device structures such as the UTB-FET and the FinFET offer improved performance and low leakage. The back-gated FDSOI offers tunable performance and could be an attractive solution for counteracting process-induced variations. These new transistor structures can be seamlessly integrated into the CMOS design stream, making them attractive to extend Si CMOS scaling. With power-aware design in the presence of variations (statistical design) taking on a bigger role, extensive collaboration between circuit design, system architects and semiconductor device and process engineers will be crucial to translate the promises of these new device technologies into actual chip performance.

## 1.7 Research Objectives and Dissertation Outline

In this dissertation, the key benefits of thin-body MOSFETs over the conventional planar bulk MOSFET are studied for future CMOS technologies. Through modeling and device simulation, scaling issues and performance of nanoscale thin-body transistor designs and their applications for improved circuit performance are evaluated.

In Chapter 2, transistor design optimization for the double-gate MOSFET is outlined in order to maximize the drive current and minimize circuit delay while taking into account parasitic resistance and capacitance effects. Based on this optimization, it is shown that a double-gate MOSFET needs to have an effective channel length larger than the physical gate length for scaling into the sub-10nm regime.

The gate delay versus energy consumption tradeoffs in double-gate versus backgated device designs are studied in Chapter 3. Adaptive  $V_{TH}$  control in back-gated

devices make them span a larger range in energy-delay space, making them attractive single technology solutions for variable throughput applications ranging from high performance to low power.

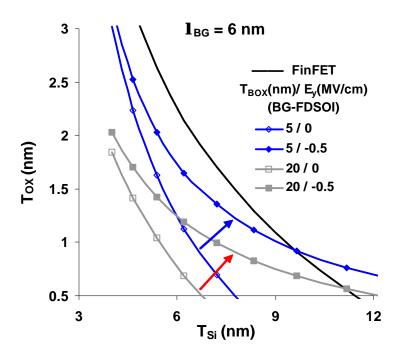

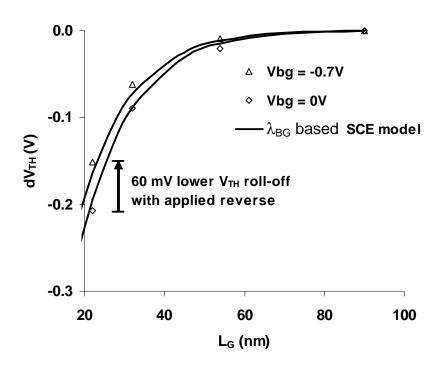

Chapter 4 quantifies the performance benefits of back-gated fully-depleted SOI devices (BG-FDSOI). The scale length for the BG-FDSOI is derived as a function of back-gate bias to account for the observed dependence of short channel effects on back-gate bias. The scale length is used to guide device design so as to make the BG-FDSOI close to FinFET in terms of performance while relaxing the body-thickness scaling requirement through the use of back-gate bias. It is shown that back-gate biasing can be used to partially reduce the impact of process variations.

Design considerations for FinFET based SRAM memory are discussed in Chapter 5. The tradeoffs in read margin, write margin, and cell area for various FinFET based designs are presented. In addition, a new FinFET-cased SRAM cell with dynamic feedback is shown to provide significant improvement in SRAM noise margin, without area or leakage penalty. Also, a 4-T FinFET SRAM cell using dynamic feedback is shown to be an attractive low cost, high-density memory solution.

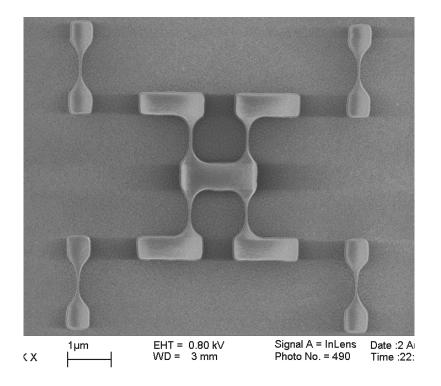

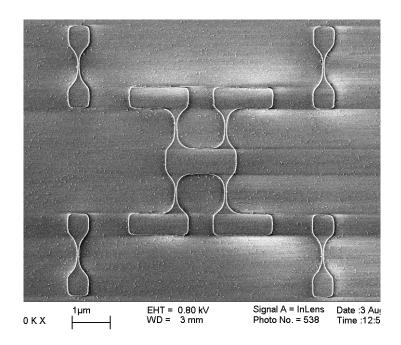

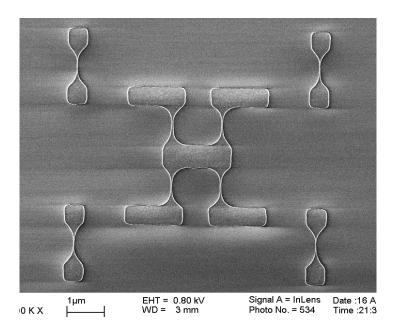

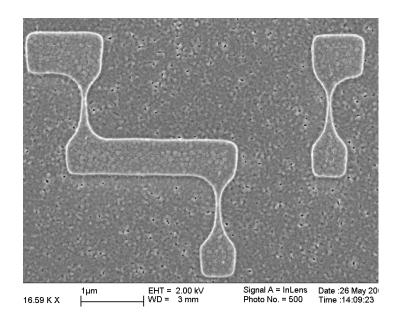

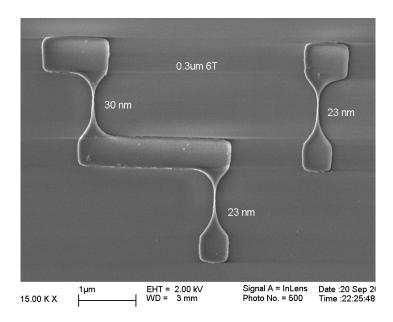

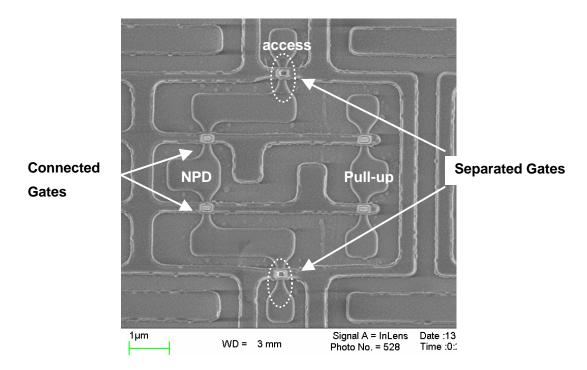

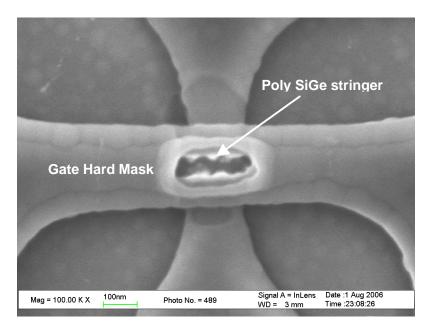

Chapter 6 presents the process development involved in the fabrication of FinFET-based SRAM with dynamic feedback. This involves the fabrication of double-gate FinFETs and independent-gate FinFETs simultaneously and is achieved using selective gate separation. The FinFET SRAM process has been transferred to other industrial fabrication facilities, because dynamic feedback is a promising manufacturable solution to extend SRAM scaling.

An overall summary of this dissertation is presented in Chapter 7. Key research contributions and suggestions for future research directions are highlighted.

#### 1.8 References

- [1] G. E. Moore, "Cramming more components onto integrated circuits," *Electronics*, vol. 38, pp. 114 -- 117, 1965.

- [2] G. E. Moore, "No exponential is forever: but "Forever" can be delayed!," presented at Proceedings of IEEE International Solid-State Circuits Conference. San Francisco, CA, 2003.

- [3] E. J. Nowak, "Maintaining the benefits of CMOS scaling when scaling bogs down," *IBM Journal of Research and Development*, vol. 46, pp. 169-80, 2002.

- [4] Z. H. Liu, C. Hu, J. H. Huang, T. Y. Chan, M. C. Jeng, P. K. Ko, and Y. C. Cheng, "Threshold voltage model for deep-submicrometer MOSFETs," *IEEE Transactions on Electron Devices*, vol. 40, pp. 86-95, 1993.

- [5] H. Wakabayashi, S. Yamagami, N. Ikezawa, A. Ogura, M. Narihiro, K. Arai, Y. Ochiai, K. Takeuchi, T. Yamamoto, and T. Mogami, "Sub-10-nm planar-bulk-CMOS devices using lateral junction control," presented at IEEE International Electron Devices Meeting 2003. Washington, DC, 2003.

- [6] "International Technology Roadmap for Semiconductors, 2005 ed," http://www.itrs.net/Links/2005ITRS/Home2005.htm.

- [7] "International Technology Roadmap for Semiconductors, 2003 ed," http://www.itrs.net/Links/2003ITRS/Home2003.htm.

- [8] P. Bai, C. Auth, S. Balakrishnan, M. Bost, R. Brain, V. Chikarmane, R. Heussner,M. Hussein, J. Hwang, D. Ingerly, R. James, J. Jeong, C. Kenyon, E. Lee, S. H.

- Lee, N. Lindert, M. Liu, Z. Ma, T. Marieb, A. Murthy, R. Nagisetty, S. Natarajan, J. Neirynck, A. Ott, C. Parker, J. Sebastian, R. Shaheed, S. Sivakumar, J. Steigerwald, S. Tyagi, C. Weber, B. Woolery, A. Yeoh, K. Zhang, and M. Bohr, "A 65nm logic technology featuring 35nm gate lengths, enhanced channel strain, 8 Cu interconnect layers, low-k ILD and 0.57 μm<sup>2</sup> SRAM cell," presented at 2004 International Electron Devices Meeting. San Francisco, CA, 2005.

- [9] J. Butterbaugh and C. M. Osburn, "Frontend processes required for continued CMOS scaling," *Solid State Technology*, 2006.

- [10] A. Asenov, "Random dopant induced threshold voltage lowering and fluctuations in sub-0.1 mm MOSFET's: A 3-D "Atomistic" simulation study," *IEEE Transactions* on Electron Devices, vol. 45, pp. 2505-13, 1998.

- [11] L. T. Su, J. B. Jacobs, J. E. Chung, and D. A. Antoniadis, "Short-channel effects in deep-submicrometer SOI MOSFETS," presented at Proceedings of 1993 IEEE International SOI Conference. Palm Springs, CA, 1993.

- [12] H.-S. P. Wong, D. J. Frank, P. M. Solomon, C. H. J. Wann, and J. J. Welser, "Nanoscale CMOS," *Proceedings of the IEEE*, vol. 87, pp. 537-70, 1999.

- [13] L. Chang, Y. K. Choi, D. W. Ha, P. Ranade, S. Y. Xiong, J. Bokor, C. M. Hu, and T. J. King, "Extremely scaled silicon nano-CMOS devices," *Proceedings of the IEEE*, vol. 91, pp. 1860-1873, 2003.

- [14] V. Subramanian, J. Kedzierski, N. Lindert, H. Tam, Y. Su, J. McHale, K. Cao, T. J. King, J. Bokor, and C. Hu, "A bulk-Si-compatible ultrathin-body SOI technology for sub-100 nm MOSFETs," presented at 1999 57th Annual Device Research Conference Digest. Santa Barbara, CA, 1999.

- [15] Y.-K. Choi, K. Asano, N. Lindert, V. Subramanian, T.-J. King, J. Bokor, and C. Hu, "Ultrathin-body SOI MOSFET for deep-sub-tenth micron era," *IEEE Electron Device Letters*, vol. 21, pp. 254-5, 2000.

- [16] J. Kedzierski, P. Xuan, V. Subramanian, J. Bokor, T.-J. King, C. Hu, and E. Anderson, "A 20 nm gate-length ultra-thin body p-MOSFET with silicide source/drain," presented at 5th Silicon Nanoelectronics Workshop. Honolulu, HI, 2000.

- [17] Y. K. Choi, D. W. Ha, T. J. King, and C. M. Hu, "Nanoscale ultrathin body PMOSFETs with raised selective germanium source/drain," *IEEE Electron Device Letters*, vol. 22, pp. 447-448, 2001.

- [18] Z. Krivokapic, W. Maszara, K. Achutan, P. King, J. Gray, M. Sidorow, E. Zhao, J. Zhang, J. Chan, A. Marathe, and M. R. Lin, "Nickel silicide metal gate FDSOI devices with improved gate oxide leakage," presented at IEEE International Electron Devices Meeting. San Francisco, CA, 2002.

- [19] J. Kedzierski, E. Nowak, T. Kanarsky, Y. Zhang, D. Boyd, R. Carruthers, C. Cabral, R. Amos, C. Lavoie, R. Roy, J. Newbury, E. Sullivan, J. Benedict, P. Saunders, K. Wong, D. Canaperi, M. Krishnan, K. L. Lee, B. A. Rainey, D. Fried, P. Cottrell, H. S. Wong, M. Ieong, and W. Haensch, "Metal-gate FinFET and fully-depleted SOI devices using total gate silicidation," presented at IEEE International Electron Devices Meeting. San Francisco, CA, 2002.

- [20] H.-S. P. Wong, K. K. Chan, and Y. Taur, "Self-aligned (top and bottom) double-gate MOSFET with a 25 nm thick silicon channel," presented at International Electron Devices Meeting. IEDM Technical Digest. Washington, DC, 1997.

- [21] D. Hisamoto, W.-C. Lee, J. Kedzierski, H. Takeuchi, K. Asano, C. Kuo, E. Anderson, T.-J. King, J. Bokor, and C. Hu, "FinFET-a self-aligned double-gate MOSFET scalable to 20 nm," *IEEE Transactions on Electron Devices*, vol. 47, pp. 2320-5, 2000.

- [22] X. Huang, W.-C. Lee, C. Kuo, D. Hisamoto, L. Chang, J. Kedzierski, E. Anderson,

H. Takeuchi, Y.-K. Choi, K. Asano, V. Subramanian, T.-J. King, J. Bokor, and C.

Hu, "Sub 50-nm FinFET: PMOS," presented at International Electron Devices

Meeting 1999. Technical Digest. Washington, DC, 1999.

- [23] N. Lindert, Y. K. Choi, L. Chang, E. Anderson, W. C. Lee, T. J. King, J. Bokor, and C. Hu, "Quasi-planar FinFETs with selectively grown germanium raised source/drain," presented at 2001 IEEE International SOI Conference. Proceedings. Durango, CO, 2001.

- [24] D. M. Fried, E. J. Nowak, J. Kedzierski, J. S. Duster, and K. T. Komegay, "A Fintype independent-double-gate NFET," presented at 61st Device Research Conference. Salt Lake City, UT, 2003.

- [25] L. Mathew, Y. Du, A.-Y. Thean, M. Sadd, A. Vandooren, C. Parker, T. Stephens, R. Mora, R. Rai, M. Zavala, D. Sing, S. Kalpat, J. Hughes, R. Shimer, S. Jallepalli, G. Workman, W. Zhang, J. G. Fossum, B. E. White, B. Y. Nguyen, and J. Mogab, "CMOS Vertical Multiple Independent Gate Field Effect Transistor (MIGFET)," presented at 2004 IEEE International SOI Conference. Charleston, SC, 2004.

- [26] I. Y. Yang, C. Vieri, A. Chandrakasan, and D. A. Antoniadis, "Back gated CMOS on SOIAS for dynamic threshold voltage control," presented at Proceedings of International Electron Devices Meeting. Washington, DC, 1995.

- [27] T. Park, S. Choi, D. H. Lee, J. R. Yoo, B. C. Lee, J. Y. Kim, C. G. Lee, K. K. Chi, S. H. Hong, S. J. Hynn, Y. G. Shin, J. N. Han, I. S. Park, U. I. Chung, J. T. Moon, E. Yoon, and J. H. Lee, "Fabrication of body-tied FinFETs (Omega MOSFETs) using bulk Si wafers," presented at 2003 Symposium on VLSI Technology. Digest of Technical Papers. Kyoto, Japan. 10-12 June 2003, 2003.

- [28] K. Okano, T. Izumida, H. Kawasaki, A. Kaneko, A. Yagishita, T. Kanemura, M. Kondo, S. Ito, N. Aoki, K. Miyano, T. Ono, K. Yahashi, K. Iwade, T. Kubota, T. Matsushita, I. Mizushima, S. Inaba, K. Ishimaru, K. Suguro, K. Eguchi, Y. Tsunashima, and H. Ishiuchi, "Process Integration Technology and Device Characteristics of CMOS FinFET on Bulk Silicon Substrate with sub-10 nm Fin Width and 20 nm Gate Length," presented at IEEE International Electron Devices Meeting, 2005. IEDM Technical Digest, Washington D.C., 2005.

- [29] L. Chang, Y.-K. Choi, K. J., N. Lindert, P. Xuan, J. Bokor, C. Hu, and T.-J. King, "Moore's law lives on," *IEEE Circuits & Devices Magazine*, vol. 19, pp. 35-42, 2003.

- [30] S. Thompson, G. Sun, K. Wu, J. Lim, and T. Nishida, "Key differences for process-induced uniaxial vs. substrate-induced biaxial stressed Si and Ge channel MOSFETs," presented at 2004 International Electron Devices Meeting. San Francisco, CA, 2005.

- [31] K. Shin, T. Lauderdale, and T.-J. King, "Effect of tensile capping layer on 3-D stress profiles in FinFET channels," presented at 63rd Device Research Conference Digest, DRC '05., 2005.

- [32] K. Shin, C. O. Chui, and T.-J. King, "Dual Stress Capping Layer Enhancement Study for Hybrid Orientation FinFET CMOS Technology," presented at IEEE International Electron Devices Meeting (Washington D.C., USA), 2005.

- [33] Z. Guo, S. Balasubramanian, R. Zlatanovici, T.-J. King, and B. Nikolic', "FinFET-based SRAM design," presented at ISLPED '05. Proceedings of the 2005 International Symposium on Low Power Electronics and Design. San Diego, CA, 2005.

- [34] A. Bhavnagarwala, S. Kosonocky, C. Radens, K. Stawiasz, R. Mann, and Q. Ye, "Fluctuation Limits & Scaling Opportunities for CMOS SRAM Cells," presented at International Electron Devices Meeting, Technical Digest, Washington DC, 2005.

- [35] S.-M. Jung, H. Lim, W. Cho, H. Cho, C. Yeo, Y. Kang, D. Bae, J. Na, K. Kwak, B. Choi, S. Kim, J. Jeong, Y. Chang, J. Jang, J. Kim, K. Kim, and B.-I. Ryu, "Highly area efficient and cost effective double stacked S<sup>3</sup> (stacked single-crystal Si) peripheral CMOS SSTFT and SRAM cell technology for 512M bit density SRAM," presented at 2004 International Electron Devices Meeting. San Francisco, CA, 2005.

- [36] E. J. Nowak, T. Ludwig, I. Aller, J. Kedzierski, M. Leong, B. Rainey, M. Breitwisch, V. Gemhoefer, J. Keinert, and D. M. Fried, "Scaling beyond the 65 nm node with FinFET-DGCMOS," presented at CICC Custom Integrated Circuits Conference. San Jose, CA, 2003.

- [37] T. Park, H. J. Cho, J. D. Choe, S. Y. Han, S. M. Jung, J. H. Jeong, B. Y. Nam, O. I. Kwon, J. N. Han, H. S. Kang, M. C. Chae, G. S. Yeo, S. W. Lee, D. Y. Lee, D. Park, K. Kim, E. Yoon, and J. H. Lee, "Static noise margin of the full DG-CMOS

- SRAM cell using bulk FinFETs (Omega MOSFETs)," presented at IEEE International Electron Devices Meeting 2003. Washington, DC, 2003.

- [38] R. V. Joshi, R. Q. Williams, E. Nowak, K. Kim, J. Beintner, T. Ludwig, I. Aller, and C. Chuang, "FinFET SRAM for high-performance low-power applications," presented at Proceedings of the 34th European Solid-State Device Research Conference. Leuven, Belgium. 21-23 Sept. 2004, 2004.

- [39] P. Tai-Su, C. Hye Jin, C. Jeong Dong, H. Sang Yeon, P. Donggun, K. Kinam, E. Yoon, and L. Jong-Ho, "Characteristics of the full CMOS SRAM cell using bodytied TG MOSFETs (bulk FinFETs)," *IEEE Transactions on Electron Devices*, vol. 53, pp. 481-7, 2006.

- [40] B. Doris, Y. H. Kim, B. P. Linder, M. Steen, V. Narayanan, D. Boyd, J. Rubino, L. Chang, J. Sleight, A. Topol, E. Sikorski, L. Shi, L. Wong, K. Babich, Y. Zhang, P. Kirsch, J. Newbury, J. F. Walker, R. Carruthers, C. D'Emic, P. Kozlowski, R. Jammy, K. W. Guarini, and M. Leong, "High performance FDSOI CMOS technology with metal gate and high-k," presented at 2005 Symposium on VLSI Technology. Kyoto, Japan. Japan Soc. of Appl. Phys.. IEEE Electron Devices Soc. 14-16 June 2005, 2005.

# Chapter 2 : Circuit implications of scaling sub-25 nm double-gate MOSFETs

#### 2.1 Introduction

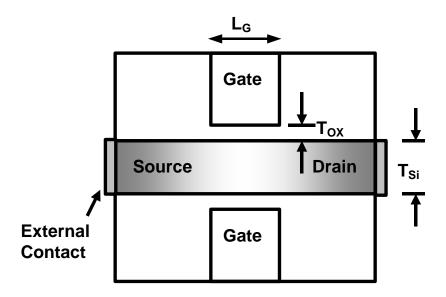

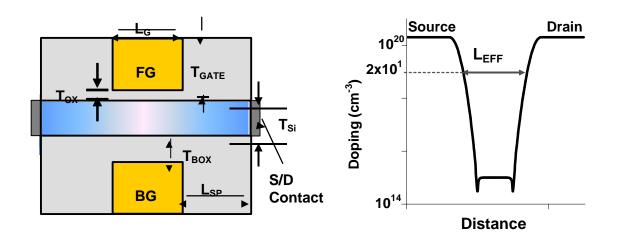

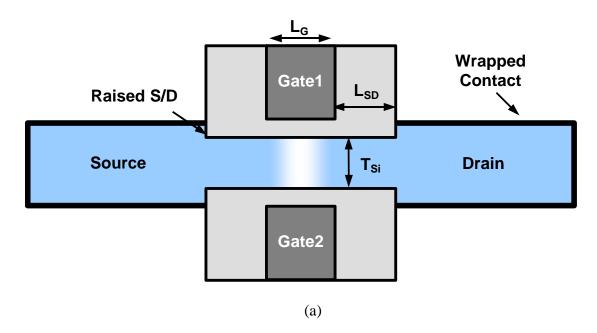

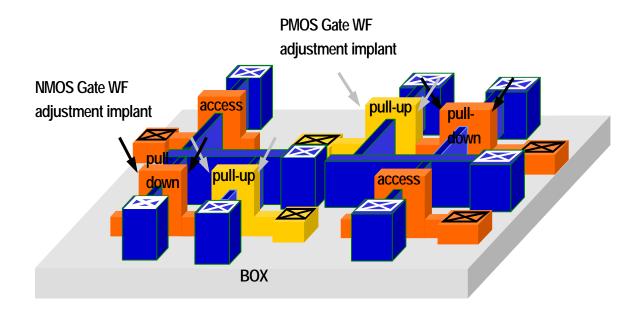

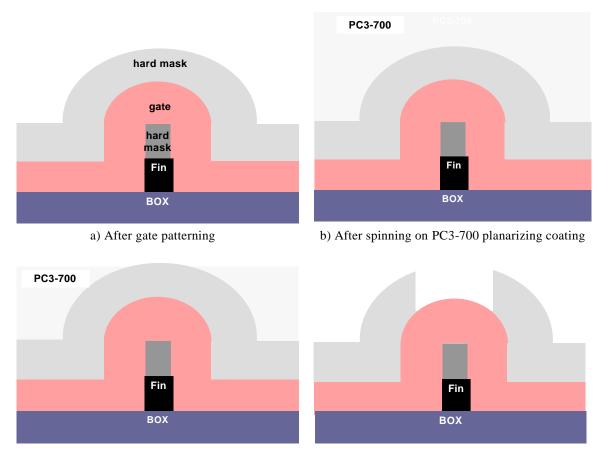

Double gate MOSFETs (Figure 2.1) such as the FinFET are promising structures to be scaled into the sub-25nm regime [1-4]. DG-MOSFETs usually are designed to have very thin Si channel that is fully-depleted in order to cut-off sub-surface leakage paths, thereby making them more scaleable. The use of lightly doped or undoped channels leads to enhanced immunity to dopant fluctuation effects, smaller drain-to-body capacitance and higher carrier mobility arising from a lower transverse electric field. With no doping in the channel, metal gates with suitable work function are required to achieve reasonable threshold voltages in fully-depleted devices. [5-8].

One of the challenges introduced by a thin silicon channel is the extremely high parasitic series resistance and contact resistance at the source and drain (S/D) regions. While parasitic resistance is a serious challenge in bulk devices [9, 10], the problem is more severe in thin-body devices, and various process technologies have been proposed to reduce it [11-13]. This chapter discusses device optimization methodology to identify the device design tradeoffs involved in order to find the balance between good-control of short channel effects (SCE) and minimizing external parasitic resistance. The tradeoffs

between the various device parameters in determining the short-channel behavior can be studied using the framework of the scale length [2, 14]. This is important from the viewpoint of device scalability and is discussed in detail in Chapter 4.

Figure 2.1: Schematic cross-section of the double-gate device structure use for simulations. Graded source-drain junctions are used. The structure includes sidewall spacers to capture the effect of parasitic capacitance. The gate work function is adjusted to meet the I<sub>OFF</sub> specification.

## 2.2 Device Design Optimization

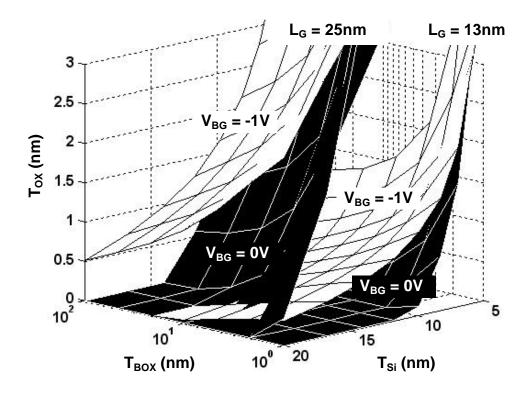

The DG-MOSFET device design optimization study has been carried out using calibrated energy transport models in the device simulator, Medici [15] and cross-checked with the quantum device simulator Nanomos 2.5 [16] for the case  $L_G=13$  nm. The parameters used in the simulations are tabulated in Table 2-1. The silicon body thickness,  $T_{Si}$ , needs to be around ~0.6 - 0.7  $L_G$  for adequate control of short channel effects (SCE). The carrier energy relaxation times used in the hydrodynamic simulations to account for transient velocity overshoot effects are adapted from [17].

| Parameter                | 45 nm node | 32 nm node |

|--------------------------|------------|------------|

| L <sub>G</sub> (nm)      | 25         | 13         |

| T <sub>OX</sub> (Å)      | 11         | 8          |

| T <sub>Si</sub> (nm)     | 7          | 5          |

| V <sub>DD</sub> (V)      | 0.7        | 0.5        |

| Gate height (nm)         | 37.5       | 19.5       |

| S-D gradient (nm/dec)    | 2.8        | 1.4        |

| t relaxation (ps)        | 1.6        | 1.3        |

| I <sub>OFF</sub> (μA/um) | 0.3        | 1          |

Table 2-1: Summary of device parameters used in the simulations. The numbers used here are essentially taken from the ITRS roadmap 2001 (with more conservative numbers for  $T_{OX}$  and  $I_{OFF}$ ). [18].

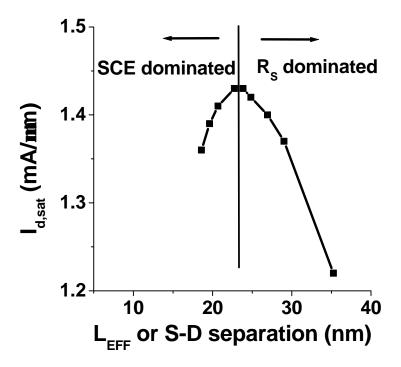

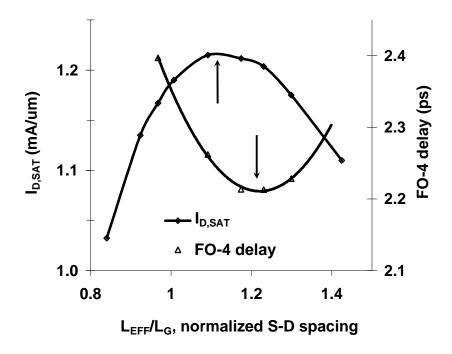

Commonly, device optimization has been carried out with the aim to maximize the saturation drive current,  $I_{D,SAT}$ , subject to an upper limit on the leakage current [5]. Using this approach, a 25nm gate length device has been optimized by changing the source-drain separation in order to get the maximum drain current,  $I_{D,SAT}$  (Figure 2.2). The source-drain separation is related to the effective channel length of the device,  $L_{EFF}$ , and can be changed by adjusting the offset spacer thickness[19, 20].

The optimal source-drain (S-D) spacing is determined by a tradeoff between short-channel effects (SCE) and the series resistance of the channel. When S-D separation decreases,  $L_{EFF}$  is reduced and the leakage current increases due to increased worsened short channel effects. The S-D spacing is changed together with the metal gate

work function,  $\Phi_M$ , to meet the constant  $I_{OFF}$  specification. Therefore in a DIBL dominated regime (small  $L_{EFF}$ ), a higher  $\Phi_M$  is needed to compensate for the leakage increase due to degraded SCE. On the other hand, as the  $L_{EFF}$  increases with a larger S-D separation, the improvement in short channel effects due to reduced source/drain coupling is offset by a large increase in parasitic extension resistance and poor gate coupling between the channel and extensions, thereby degrading  $I_{D,SAT}$ . Thus, the right balance between the SCE and series resistance sets the optimal  $L_{EFF}$ .

Figure 2.2: Dependence of the  $I_{D,SAT}$  on the source to drain separation for  $L_G$ =25 nm. The optimal  $I_{D,SAT}$  is set by the tradeoff between SCE and series resistance.  $L_{EFF}$  is defined at the position where the doping falls off to  $2x10^{19}$  cm<sup>-3</sup>

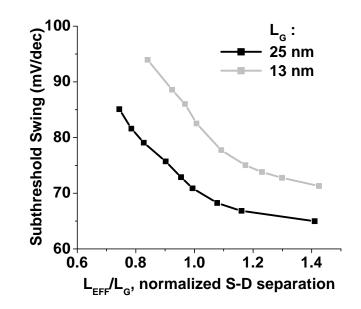

Figure 2.3: Subthreshold swing variation with the S-D separation normalized w.r.t.  $L_G$ . The swing for shorter  $L_G$  degrades due to increased source/drain coupling to the channel resulting in worsened DIBL and sub-threshold swing.

Figure 2.4: The optimal  $L_{EFF}$  needed is larger than  $L_{G}$  for very small  $L_{G}$ . With degraded SCE, the optimal underlap between gate and source/drain regions needed is greater.

Also, when the gate length is scaled from 25 nm to 13 nm, the short-channel effects are degraded (Figure 2.3) if the  $T_{OX}$  and  $T_{Si}$  cannot be scaled proportionately to  $L_{G}$  due to gate leakage limitations. Therefore, the optimal S-D separation or  $L_{EFF}$  for maximizing  $I_{D,SAT}$  in a scaled device with degraded SCE is expected to be larger. This is verified in Figure 2.4. Thus, having an effective channel length that is larger than the physical gate length ( $L_{EFF} > L_{G}$ ) is probably necessary to continue scaling devices. The trends hold true for PMOS devices as well.

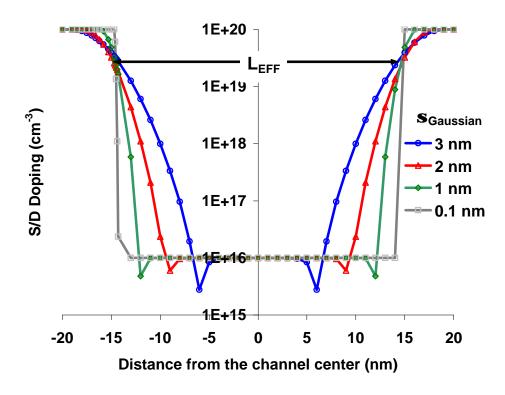

In the above simulations the source/drain doping gradients were kept fixed as shown in Table 2-1. In order to understand the effect of source/drain doping gradients on device optimization, FinFETs with four different doping gradients were optimized to have same  $I_{OFF}$  and DIBL =100 mV/V, resulting in devices with the same  $V_{TH}$  and SCE. A device with a very graded profile would need thick gate sidewall spacers in practice to reduce the S/D encroachment into the channel. The optimal doping profiles from simulation are shown in Figure 2.5 and are all seen to intersect at a doping level of 2-3 x  $10^{19}$  cm<sup>-3</sup>, which is the level at which  $L_{EFF}$  is defined [20]. Alternatively, if the  $V_{TH}$  and SCE effects are the same in these devices, they ought to have the same  $L_{EFF}$ . Therefore, the doping level of 2-3 x  $10^{19}$  cm<sup>-3</sup> is an appropriate point from which to define  $L_{EFF}$ , consistent with [20].

This implies that different source-drain dopant activation technologies can be used in conjunction with the appropriate spacer thickness to achieve the same  $L_{\text{EFF}}$ . Steep S/D junctions need thin spacers, while graded junctions need a correspondingly thicker spacers.

Figure 2.5: Equivalent source-drain doping profiles identified from Medici simulations [15] of four different FinFET devices, all with the same  $I_{OFF}$  and DIBL=100 mV/V. These equivalent doping profiles all intersect at a doping level of 2-3 x  $10^{19}$  cm<sup>-3</sup>, implying that they all have the same  $L_{EFF}$ . Steep junctions need thin gate sidewall spacers, while graded junctions need a correspondingly thicker spacers to achieve the same  $L_{EFF}$ .

# 2.3 Effect of Parasitic Capacitances

This optimization for maximum  $I_{D,SAT}$ , however, does not take into consideration the role of parasitic capacitances and their impact on circuit performance. The total gate capacitance is the sum of the gate oxide capacitance, the gate to S/D overlap capacitance and the sidewall fringing capacitance [21].

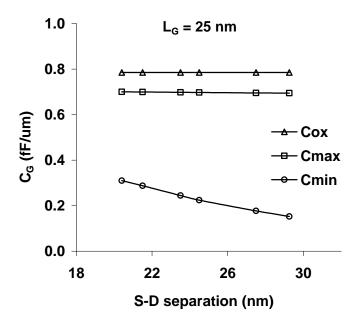

In order to separate the effect of the overlap capacitance from the sidewall fringing effects, the capacitance simulations were run with a line gate, where the gate height,  $T_G$ , is set to zero. Therefore,  $C_{MIN}$ ,  $(C_G @V_{GS}=0)$ , is related directly to the overlap capacitance arising from the gate-to-source-drain overlap region. As the source and drain separation increases, the overlap capacitance between the gate and the source-drain regions decreases linearly (Figure 2.6). The  $C_{MAX}$ ,  $(C_G @V_{GS}=V_{DD})$ , the gate capacitance in strong inversion, is slightly smaller than  $C_{OX}$  (=  $\epsilon_{OX}/T_{OX}$ , equivalent oxide capacitance), due to the increase in the electrical oxide thickness from quantum mechanical effects and is independent of source/drain overlap.

Figure 2.6: Variation of gate capacitance ( $C_G$ ) with the S-D separation (assuming a line gate,  $T_G = 0$ nm).  $C_{MAX}$  is slightly smaller that  $C_{OX}$  because the quantum mechanical charge centroid is shifted away from the oxide interface.  $C_{MIN}$  ( $C_G @V_{GS} = 0$ ), decreases almost linearly with the S-D separation due to reduced gate-to-source/drain overlap area.

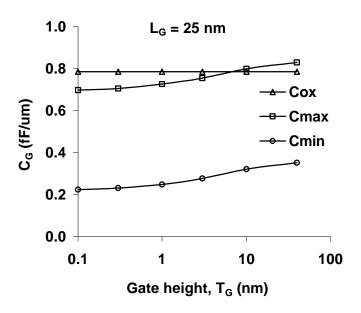

Figure 2.7: Variation of total gate capacitance ( $C_G$ ) with the gate height ( $T_G$ ).  $C_{MIN}$  and  $C_{MAX}$  increase with gate height due to increased fringing fields and saturate at large  $T_G$ .

The other component of the gate capacitance, the parasitic sidewall capacitance through the gate sidewall spacer, is not affected by the source-drain overlap. This component increases as the height of the gate is increased and saturates at large values of the gate height (Figure 2.7). While a smaller gate height is good to achieve a smaller capacitance, the height of the gate electrode is often determined by the need to keep the sheet resistance of the gate within bounds, and to ensure that the channel is protected from the S/D implants.

### 2.4 Circuit Simulations

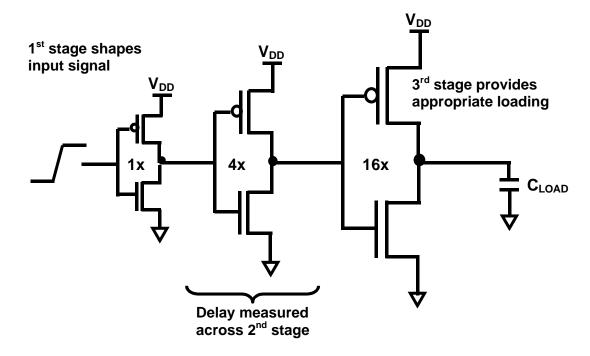

To investigate the effect of parasitic capacitance on circuit performance, mixed-mode simulations of inverter FO-4 buffer chain were carried out in Medici [15]. The parasitic source/drain capacitance for a thin body transistor is very small, so it is expected that the optimal fan-out using the method of logical effort for minimal delay would be

closer to 3 [22]. However, a smaller effective fan-out per stage increases the number of driving stages and the total layout area, and the sensitivity of delay to fan-out near the optimal fan-out is small, so the fan-out factor of 4 is still used in this study.

Figure 2.8: Schematic of FO-4 inverter mixed-mode simulation setup to measure the stage delay. The chain consists of 3 stages, the first stage corrects the input slope, the propagation delay is measured across the second stage and the last stage has a capacitive load equal to 4x of its input capacitance to present the appropriate Miller capacitance

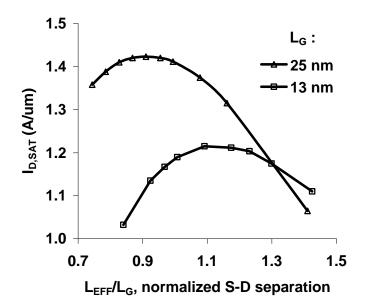

The dependence of the FO-4 inverter delay on the source-drain spacing was investigated. The optimal spacing was found to be larger than that expected from maximizing drive current (Figure 2.9). This is because as the gate-to-S/D overlap region becomes smaller, its parasitic contribution to the total gate capacitance decreases. Therefore, in increasing the S/D spacing beyond the optimal value for maximum  $I_{D,SAT}$ , (from Figure 2.2) the capacitance reduction is more significant than the reduction in  $I_{D,SAT}$ , which results in a overall reduced delay. However, when the source-drain spacing

becomes even larger i.e. as the gate to S/D underlap increases, the series resistance starts to dominate and the delay goes back up. The optimal spacing corresponding to minimal delay can result in dynamic power savings as well, because the parasitic part of the total switching capacitance is lowered significantly.

Figure 2.9: Dependence of the  $I_{D,SAT}$  and FO-4 delay on the normalized source to drain separation for  $L_G=13$  nm. The optimal separation from the delay perspective is clearly larger than that for maximum  $I_{D,SAT}$ , i.e.  $L_{EFF} > L_G$

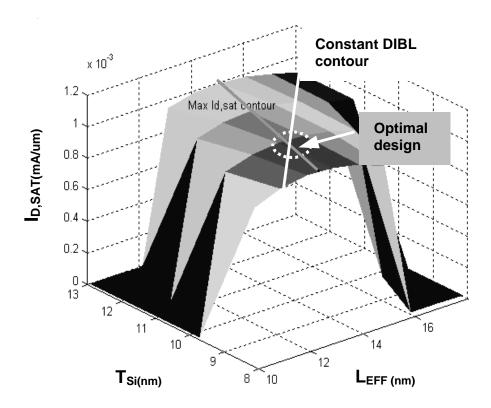

# 2.5 Device Optimization under constant DIBL constraint

Device optimization thus far has been carried out under constant  $I_{OFF}$ , with  $L_{EFF}$  as the only design variable. As  $L_{EFF}$  is made longer, the DIBL gets better monotonically. In reality, constant  $V_{TH}$  (sets leakage) and constant DIBL are both constraints that need to be satisfied in maximizing performance. This aspect is addressed in greater detail in Chapter 4 on back-gated FDSOI design. In this section, a 100 mV/V DIBL constraint is

additionally imposed, and the design optimization is briefly addressed below. Here  $T_{si}$  is the additional physical parameter that is varied together with  $L_{EFF}$  to optimize device performance under DIBL constraints.

Figure 2.10: Dependence of  $I_{D,SAT}$  on  $T_{Si}$  and  $L_{EFF}$  for DG-MOSFET with  $L_G=13$  nm, EOT = 6 Å,  $\rho_C=10^{-8}~\Omega~cm^2$ . As  $T_{Si}$  increases, SCE are degraded, and  $L_{EFF}$  needs to be longer in order to meet the constant DIBL constraint, as shown by the constant DIBL contour. The optimal  $I_{D,SAT}$  shows a weak dependence on  $T_{Si}$ , decreasing with thinner  $T_{Si}$  due to higher series resistance.

For each  $T_{Si}$ , the  $L_{EFF}$  optimization is carried out as described in Section 2.2 in order to identify the optimal  $I_{D,SAT}$  and is shown by maximum  $I_{D,SAT}$  contour in Figure 2.10. When  $T_{Si}$  increases, SCE are degraded, and  $L_{EFF}$  needs to be longer in order to meet the constant DIBL constraint, as shown by the constant DIBL contour in Figure 2.10. The intersection point between the maximum  $I_{D,SAT}$  contour and the constant DIBL contour

corresponds to the optimal device under DIBL constraints from the viewpoint of maximizing ON-current. A similar study can be carried out to identify optimal delay point under SCE constraints.

#### 2.6 Conclusions

When optimizing DG-MOSFET for maximum drive current, I<sub>D,SAT</sub>, under constant leakage constraints, it is seen that the effective channel length, L<sub>EFF</sub>, is an important design parameter. The optimal S-D separation is determined from the tradeoffs between short-channel effects and parasitic series resistance. Nanoscale devices may have to be designed with gate underlapped source/drain regions to meet the SCE requirements and optimize their performance. Also, the optimal underlap for maximizing drive current, I<sub>D,SAT</sub>, is seen to be larger for smaller gate length devices. It is clear that optimizing devices with circuit performance considerations is important. The impact of parasitic capacitances on the performance of DG-MOSFETs has been investigated. The optimal L<sub>EFF</sub> for minimizing circuit delay has been found to be larger than that needed to maximize transistor drive current, due to smaller parasitic overlap capacitance.

#### 2.7 References

- [1] H. S. P. Wong, Y. Taur, and D. J. Frank, "Discrete random dopant distribution effects in nanometer-scale MOSFETs," *Microelectronics Reliability*, vol. 38, pp. 1447-1456, 1998.

- [2] D. J. Frank, Y. Taur, and H. S. Wong, "Generalized scale length for two-dimensional effects in MOSFETs," *IEEE Electron Device Letters*, vol. 19, pp. 385-7, 1998.

- [3] L. L. Chang, Y. K. Choi, J. Kedzierski, N. Lindert, P. Q. Xuan, J. Bokor, C. M. Hu, and T. J. King, "Moore's law lives on Ultra-thin body SOI and FinFET CMOS transistors look to continue Moore's law for many years to come," *Ieee Circuits & Devices*, vol. 19, pp. 35-42, 2003.

- [4] Y.-K. Choi, N. Lindert, P. Xuan, S. Tang, D. Ha, E. Anderson, T.-J. King, J. Bokor, and C. Hu, "Sub-20 nm CMOS FinFET technologies," presented at International Electron Devices Meeting. Technical Digest. Washington, DC, 2001.

- [5] L. Chang, S. Tang, K. Tsu-Jae, J. Bokor, and H. Chenming, "Gate length scaling and threshold voltage control of double-gate MOSFETs," presented at International Electron Devices Meeting. Technical Digest. IEDM. San Francisco, CA, 2000.

- [6] P. Ranade, R. Lin, Q. Lu, Y. C. Yeo, H. Takeuchi, T. J. King, and C. Hu, "Molybdenum gate electrode technology for deep sub-micron CMOS generations," presented at Gate Stack and Silicide Issues in Silicon Processing II. Symposium. San Francisco, CA, 2002.

- [7] I. Polishchuk, P. Ranade, T. J. King, and C. Hu, "Dual work function CMOS gate technology based on metal interdiffusion," presented at Gate Stack and Silicide Issues in Silicon Processing II. Symposium. San Francisco, CA, 2002.

- [8] D. W. Ha, P. Ranade, Y. K. Choi, J. S. Lee, T. J. King, and C. M. Hu, "Molybdenum gate work function engineering for ultra-thin-body silicon-oninsulator (UTB SOI) MOSFETs," *Japanese Journal of Applied Physics Part 1-*Regular Papers Short Notes & Review Papers, vol. 42, pp. 1979-1982, 2003.

- [9] S. Thompson, P. Packan, T. Ghani, M. Stettler, M. Alavi, I. Post, S. Tyagi, S. Ahmed, S. Yang, and M. Bohr, "Source/drain extension scaling for 0.1 um and

- below channel length MOSFETs," presented at 1998 Symposium on VLSI Technology Digest of Technical Papers. Honolulu, HI, 1998.

- [10] J. Yuan, P. M. Zeitzoff, and J. C. S. Woo, "Source/drain parasitic resistance role and electrical coupling effect in sub 50 nm MOSFET design," presented at 32nd European Solid State Device Research Conference. Firenze, Italy. 24-26 Sept. 2002, 2002.

- [11] Y. K. Choi, D. W. Ha, T. J. King, and C. M. Hu, "Nanoscale ultrathin body PMOSFETs with raised selective germanium source/drain," *Ieee Electron Device Letters*, vol. 22, pp. 447-448, 2001.

- [12] Y. Chunshan, V. W. C. Chan, and P. C. H. Chan, "Low S/D resistance FDSOI MOSFETs using polysilicon and CMP," presented at Proceedings 2001 IEEE Hong Kong Electron Devices Meeting. Hong Kong, China. IEEE Electron Devices Soc.. Dept. Electron. & Inf. Eng. Hong Kong Polytech. Univ. 30 June 2001, 2001.

- [13] Z. Krivokapic, W. Maszara, F. Arasnia, E. Paton, Y. Kim, L. Washington, E. Zhao, J. Chan, J. Zhang, A. Marathe, and M. R. Lin, "High performance 25 nm FDSOI devices with extremely thin silicon channel," presented at 2003 Symposium on VLSI Technology. Digest of Technical Papers. Kyoto, Japan. 10-12 June 2003, 2003.

- [14] K. Suzuki, T. Tanaka, Y. Tosaka, H. Horie, and Y. Arimoto, "Scaling theory for double-gate SOI MOSFET's," *IEEE Transactions on Electron Devices*, vol. 40, pp. 2326-9, 1993.

- [15] "Medici v. 2002.4," Synopsys Inc.

- [16] "Nanomos, v 2.5," http://nanohub.purdue.edu.

- [17] M. Y. Chang, D. W. Dyke, C. C. Leung, and P. A. Childs, "High-energy electron-electron interactions in silicon and their effect on hot carrier energy distributions," *Journal of Applied Physics*, vol. 82, pp. 2974-9, 1997.

- [18] "International Technology Roadmap for Semiconductors," 2001.

- [19] Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices: Cambridge University Press, 1998.

- [20] Y. Taur, Y.-J. Mii, R. Logan, and H.-S. Wong, "On "effective channel length" in 0.1-um MOSFETs," *IEEE Electron Device Letters*, vol. 16, pp. 136-8, 1995.

- [21] J. M. Rabaey, A. Chandrakasan, and B. Nikolic', *Digital Integrated Circuits*, 2 ed: Prentice Hall, 2002.

- [22] I. Sutherland, R. F. Sproull, and D. Harris, *Logical Effort: Designing Fast CMOS Circuits*: Morgan Kaufmann Publishers, 1999.

# **Chapter 3: Energy-Delay Optimization of Multi-**

# Gate FETs in the sub-25nm era

#### 3.1 Introduction

There are primarily two types of power dissipation in a CMOS digital integrated circuit: dynamic and static. The dynamic power arises from the useful work done in switching between logic states during digital computation. Dynamic power is proportional to  $CV_{DD}^2f$ , where C is the capacitive load being switched,  $V_{DD}$  is the supply voltage, and f is the clock frequency. The dynamic power dissipation is directly related to the rate of computation, so it can be adjusted to meet power budgets by adjusting the frequency of operation. Supply voltage scaling can also be used to adjust the dynamic power dissipation [1].

Static power, on the other hand, is associated with the holding of logic states i.e. when the circuit is idle. This power is due to leakage mechanisms such as sub-threshold leakage or gate leakage within the transistors in the circuit, and is wasteful because it does not contribute to computation [1]. Leakage is unavoidable in modern CMOS technologies, and actually increases exponentially with scaling and is perceived as a major roadblock to scaling [2]. Today's microprocessors have thus entered power-limited

scaling where performance alone is not critical; rather performance under a power budget is the metric of relevance [3].

Power dissipation becomes a primary design constraint with further CMOS scaling, requiring circuit designs to be optimized considering both energy and delay. The effectiveness of heat removal system from hot spots poses limits on the power density, and impacts system cost and maximum attainable performance. Power constraints are even more stringent in mobile processor designs in which long battery life is desirable. The goal of a processor design, therefore, is to achieve the maximum operating frequency while meeting the power density constraint.

For high-performance chips, the high subthreshold leakage current must be within bounds to keep chip static power dissipation within acceptable limits. One common approach is multi-V<sub>TH</sub> technology, where low V<sub>TH</sub> high-performance MOSFETs, are used only in critical paths to meet delay requirements and higher V<sub>TH</sub> and larger EOT devices with lower leakage currents are used everywhere else to minimize the overall power dissipation without sacrificing performance. To achieve optimal energy vs. delay (E-D) performance [4], multiple transistor designs are needed to cater to various application areas. Other circuit/architectural techniques used to curtail static power dissipation include the use of sleep transistors to cut off access to power/ground rails or other techniques to power down circuit blocks [5].

Another potential technique used in bulk-Si MOSFET technology to tune the  $V_{TH}$  of NMOS and PMOS transistors separately is adaptive body biasing (ABB). The  $V_{TH}$  of a transistor can be controlled to a limited extent by using ABB, by applying a finite body-to-source voltage. By modulating the  $V_{TH}$ , the overall leakage and frequency for a die can

be controlled to some extent. Reverse body biasing (RBB) has been employed to reduce the standby leakage power dissipation, and the application of forward body bias (FBB) in active mode increases the frequency of operation, but it increases the leakage power as well. FBB has the desirable result of reducing the depletion thickness of the channel, thereby improving the short-channel effects (SCE) of a bulk-Si MOSFET, and improves the overall sensitivity to parametric variations. For the same reason, RBB increases the sensitivity to process variations due to worsened SCE. In extremely scaled transistors, the body effect is degraded due to worse short channel effects, and so adaptive body biasing to reduce leakage is not effective [6, 7]. Implementing ABB in bulk-Si technology requires a triple-well technology, which may not always be available.

For a multi-gate FET, adaptive threshold control, implemented through back-gate biasing, can be used in conjunction with dynamic voltage scaling (DVS) to minimize power dissipation in circuits and has been used in this study to achieve energy-delay optimality [8-11]. The goal of this combined  $V_{DD}$  and  $V_{TH}$  scaling scheme is to achieve the optimal combination of frequency and power, i.e. identify the minimum energy required to operate at a certain target frequency.

With parallelism, achieved through the use multiple cores, becoming more important, the emphasis on transistor performance is reducing and that on lower leakage transistors with minimal variations is increasing. In scaled technologies, achieving the target  $V_{TH}$  through process control alone is getting harder and the degree of process variations is getting larger. Dynamically tunable  $V_{TH}$  technologies provide a post-manufacturing electrical knob to fine tune a chip back to within the specifications and

thereby fill this gap between the target and achievable  $V_{TH}$  and are expected to become more important in the future.

Conventional UTB or FDSOI MOSFETs are built on thick BOX and therefore exhibit little or no effect on  $V_{TH}$  from the application of back-gate bias. However, when the BOX thickness is scaled down, the back-gate coupling to the channel increases and the  $V_{TH}$  change with back-gate bias can be used to modulate MOSFET performance. This chapter presents the design of energy-delay optimized back-gated thin-body SOI MOSFETs, (BG-FETs), and uses back-gate biasing to control the leakage power dissipation. It is demonstrated here that BG-FETs exhibit power savings over double-gate MOSFETs that increase with scaling into the sub-10 nm gate length regime. [12]

# 3.2 Adaptive V<sub>TH</sub> in FDSOI MOSFETs

In this section, we quantify the circuit level benefits of enhancement mode (ENH) thin-body double gate (DG) and back-gated (BG) MOSFETs.

Figure 3.1 - Cross-sectional schematic of BG FETs studied. The effective channel length,  $L_{EFF}$ , for the BG-FET is defined as the separation between the points where doping falls off to  $2x10^{19}$  cm<sup>-3</sup>.

|                                         | 32 nm node           |                                       |      | 22nm node            |

|-----------------------------------------|----------------------|---------------------------------------|------|----------------------|

|                                         | DC ENIL              | DG-FET                                |      | DC FNIII             |

| Device parameters                       | BG ENH               | HP <sup>a</sup>                       | LPb  | BG-ENH               |

| L <sub>G</sub> (nm)                     | 13                   |                                       |      | 9                    |

| L <sub>SP</sub> (nm)                    | 13                   |                                       |      | 9                    |

| T <sub>OX</sub> (Å) (EOT)               | 6                    |                                       |      | 5                    |

| T <sub>BOX</sub> (Å)                    | 63                   | 11.5                                  | 11.5 | 47                   |

| T <sub>Si</sub> (nm)                    | 5                    | 8.2                                   | 8.2  | 3                    |

| T <sub>GATE</sub> (nm)                  | 19.5                 | 19.5                                  | 19.5 | 13.5                 |

| N <sub>BODY</sub> (cm <sup>-3</sup> )   | 2 x 10 <sup>16</sup> | $2 \times 10^{16}$ $2 \times 10^{16}$ |      | 2 x 10 <sup>16</sup> |

| $\Phi_G(eV)$                            | 4.4                  | 4.45                                  | 4.6  | 4.33                 |

| V <sub>DD</sub> (V)                     | 0.6                  | 0.6                                   | 0.6  | 0.5                  |

| S-D $\sigma_{Gaussian}$ (nm)            | 2.0                  | 2.0                                   | 2.0  | 1.4                  |

| $\rho_{\rm C}$ , $(\Omega\text{-cm}^2)$ | 5x10 <sup>-9</sup>   | 5x10 <sup>-9</sup>                    |      | 5x10 <sup>-9</sup>   |

| L <sub>EFF</sub> (nm)                   | 20.2                 | 15.6                                  | 15.6 | 12                   |

| $I_{off, active} (\mu A/\mu m)$         | 1                    | 1                                     | 0.01 | 3                    |

| I <sub>ON</sub> (μA/um)                 | 575                  | 665                                   | 398  | 629                  |

| I <sub>SLEEP</sub> (nA/μm) <sup>c</sup> | 10                   | 1000                                  | 10   | 66                   |

Table 3-1: Summary of the MOSFET design parameters used. -  $HP^a$  refers to high performance and  $LP^b$  refers to low power. The  $L_{EFF}$  for the MOSFET is defined as distance between points where the doping concentration falls to  $2x10^{19}$  cm<sup>-3</sup>. <sup>c</sup> The sleep state standby leakage current,  $I_{SLEEP}$ , is evaluated at  $V_{BG} = -V_{DD}$ .

DG-FET and BG-FET device simulations were carried out in the Taurus-Device simulator using drift-diffusion transport and the 1-D Schrödinger equation [13]. (See Figure 3.1 and Table 3-1).

### 3.3 Transistor Design Optimization

The DG-FETs and BG-FETs were each optimized to achieve maximum  $I_{ON}$  at constant active-state leakage,  $I_{OFF}=10^{-6}$  A/ $\mu$ m, and DIBL of 100 mV/V. This was achieved by co-optimizing  $T_{Si}$ ,  $T_{BOX}$ , S-D separation to change  $L_{EFF}$ , and using gate workfunction tuning to achieve the target  $I_{OFF}$ , at constant  $T_{OX}$  using the design-of-experiments (DOE) methodology, similar to that described in Chapter 2 [14]. Two versions of the DG-FET are also included in the study: a low  $V_{TH}$ , high-performance (HP) device and a higher  $V_{TH}$ , low-power (LP) device. (See Table 3-1.) The only difference between these two devices is the  $V_{TH}$ , with the LP device having a 100x lower leakage as compared to the HP device, achieved through a gate workfunction shift. These two versions of the DG-FETs would be needed for a multi- $V_{TH}$  technology to control the overall power dissipation as discussed earlier. Note that  $L_{EFF}$  must be larger than the physical gate length  $L_{G}$  to achieve good short channel effects in sub-15nm devices [15] (Table 3-1).

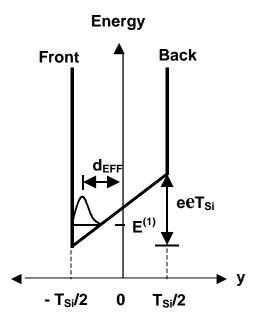

BG-FETs, have a thicker  $T_{BOX}$ , and therefore need to have a thinner body than DG-FETs to have the same degree of short channel effect control. In this section, the front- and back-gate workfunctions are assumed to be equal, resulting in a negligible transverse electric field in the channel. This pushes the active state leakage path to position of the weakest gate control, i.e. the back oxide/channel interface. However, in the sleep state, a reverse bias can applied to the back-gate to reduce the leakage of these

devices. The scalability of the BG-FET can be improved if reverse back-gate biasing can be used even in the active mode (together with a front-gate with a lower workfunction to compensate for the accompanying  $V_{TH}$  shift) to setup a high electric field in the channel and is described in chapter 4.

A thinner  $T_{BOX}$  provides higher  $V_{TH}$  sensitivity to  $V_{BG}$ . However, an ultra-thin  $T_{BOX}$  also has increased quantum-mechanical direct tunneling between the back-gate and the channel near the drain edge, thereby increasing the BG-leakage current in the sleep mode. Another disadvantage is worsened sub-threshold slope and device transconductance,  $g_M$ , due to the capacitive division of the channel potential between the front gate and the back-gate causing degraded transistor performance. In addition, at large reverse back-gate bias values, the back channel is biased into accumulation and the  $V_{TH}$  sensitivity to back-biasing becomes quite weak. At that point, the maximum reverse bias is limited by the back-gate induced band-band tunneling (BTBT) between the back-channel accumulation layer and the reverse-biased drain. The  $T_{BOX}$  was chosen in this work in such a way that the back-side BTBT leakage limit is still not reached at maximum back bias (limited to  $-V_{DD}$  for the n-channel MOSFET) and the direct tunneling leakage through the back-oxide is small (50-100× lower) compared to  $I_{OFF}$ .

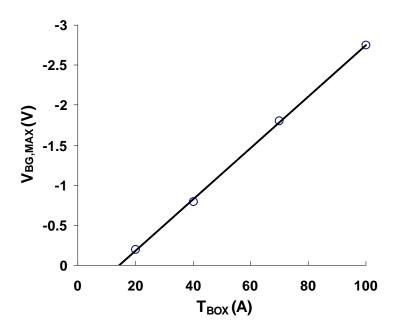

The back-gate effect to modulate  $V_{TH}$  in back-gated FDSOI devices can be retained with scaling if the  $T_{BOX}$  can be scaled as well (Figure 3.2). The  $T_{BOX}$  needs to be about ~5x –10x of the  $T_{OX}$  to have a good tradeoff of  $V_{TH}$  tunability without having to apply a very large  $V_{BG}$  and to limit degradation of device turn-on characteristics.

Figure 3.2 - The BG-FET devices show good sensitivity to  $V_{BG}$  that is retained with scaling, if the  $T_{BOX}$  is scaled as well. (ref. Table 3-1)

# 3.4 Comparison of DG-FETs and BG-FETs

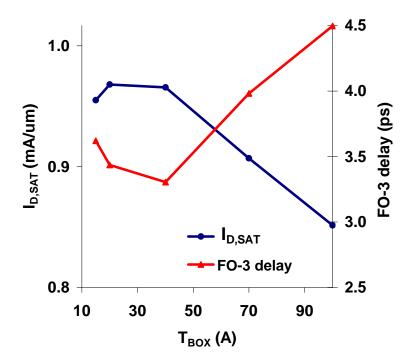

BG-FETs and DG-FETs are compared to study the short channel behavior, ON-state performance and the immunity to process-induced variations. Figure 3.2 shows that the BG-FET design can be optimized to have a large back-gate effect, and therefore can be put into deep sleep mode, making it attractive for low power applications. Simulations of the BG- FETs were carried out with  $L_G = 9$ nm and 13nm, and the effectiveness of the back-gate control on  $V_{TH}$  is still retained at short  $L_G$ . The BG-FETs are optimized in order to achieve a sleep state current of  $10^{-8}$  A/ $\mu$ m at  $V_{BG} = -V_{DD}$ . Increasing the back-gate effect to reduce the sleep state current comes at the expense of  $I_{ON}$ . From Figure 3.3, it can be seen that the BG-FETs devices have  $I_{ON}$  intermediate to those for the HP and LP DG-FETs. In order to limit saturation current degradation arising from the back-gate effect, a thicker  $T_{BOX}$  is desirable.

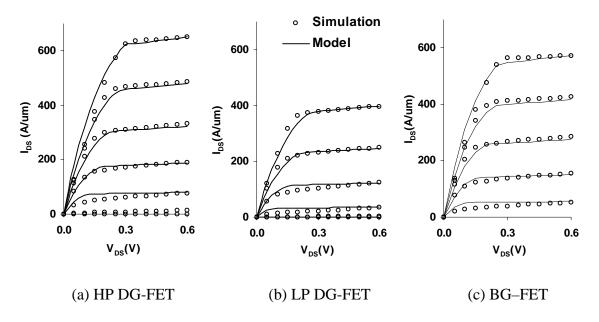

Figure 3.3 - Drain characteristics of the FETs used in the study. (a-c) The simulation data from Taurus [13] (points) was fitted to an empirical model (Eq 3-1), shown by solid lines.

Figure 3.4 (a) Change in the  $I_{DS}$  with back-gate biasing is captured through (b)  $I_{OFF}$  vs.  $V_{DS}$  @ $V_{BG}$ . The leakage of the BG devices matches that of the HP DG-FET at zero back bias, and at  $V_{BG}$  = - $V_{DD}$  match that of the LP DG-FET.

$$I_{DLIN} = \frac{2KV_{DS}(V_{GS} - V_{TH} - 0.5V_{DS})}{V_{DS} + E_{C}L} \left(1 - \frac{V_{DS}}{V_{A}}\right)$$

$$I_{DSAT} = \frac{K(V_{GS} - V_{TH})^{2}}{V_{GS} - V_{TH} + E_{C}L} \left(1 - \frac{V_{DS}}{V_{A}}\right)$$

$$V_{DSAT} = \frac{E_{c}L(V_{GS} - V_{TH})}{E_{C}L + V_{GS} - V_{TH}}$$

Eq. 3-1

A semi-empirical device model (Eq. 3-1) based on a subset of BSIM3 model equations can fit the simulated drain current characteristics,  $I_{DS}$ - $V_{DS}$  data of HP, LP DG-FETs and BG-FETs (Figure 3.3). It also captures the  $V_{TH}$  shift from back-gate biasing and captures its effect on ON-state and OFF-state currents (Figure 3.4). Also, mobility enhancement parameters and the effect of parameter variations can be modeled to create Spectre AHDL models for DC simulation to estimate gate delay and power dissipation.

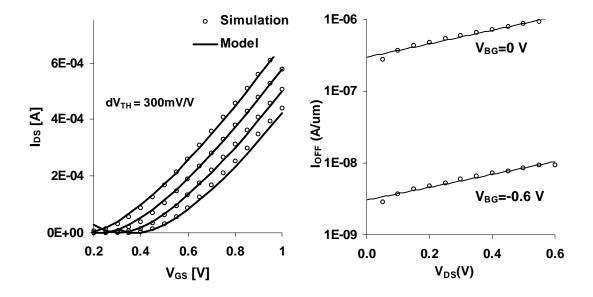

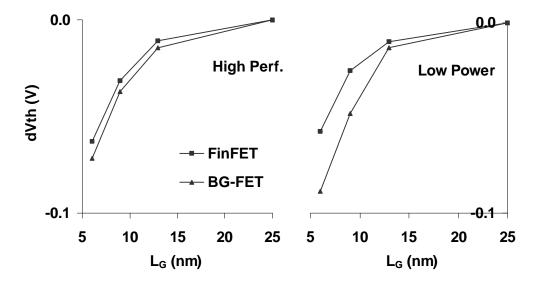

Figure 3.5 - The BG-FET devices show similar  $V_{TH}$ -rolloff behavior to the DG-FET devices. The low power and high-performance devices show similar  $V_{TH}$ -roll off.

In comparing short-channel effects, V<sub>TH</sub> roll-off (

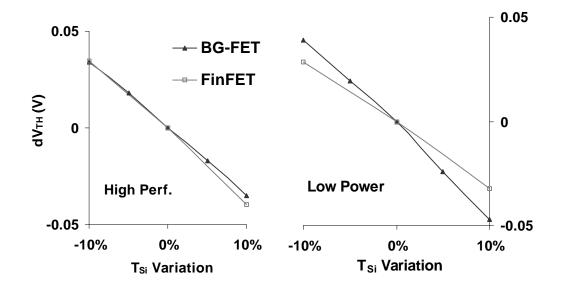

Figure 3.5) and the sensitivity of  $V_{TH}$  to  $T_{Si}$  variations (Figure 3.6) for the BG-FET and the FinFET devices are similar. The DG-FET shows slightly better roll-off and lower  $T_{Si}$  sensitivity, because it has the thickest Si body.

Figure 3.6 - The BG-FET and the DG-FET devices show similar sensitivity to variations in  $T_{Si}$  for both HP and LP designs.

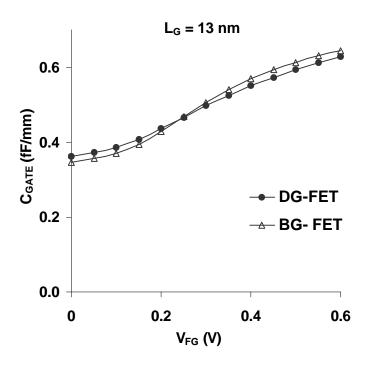

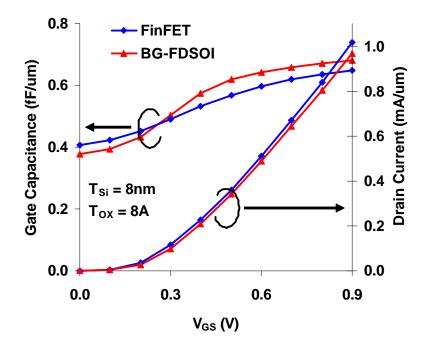

The BG-FET has slightly larger inversion gate capacitance as compared to the DG-FET (Figure 3.7) due to its increased carrier confinement due to the applied backgate bias resulting in a quantum-mechanical charge centroid location that is closer to the gate oxide interface. The BG-FET needs to have a slightly longer  $L_{EFF}$  as compared to the DG-FET to achieve the same SCE, resulting in a reduced overlap capacitance.

Figure 3.7 - The gate capacitance is similar for BG-FET and DG-FET devices, thus, the intrinsic delay, tp0, scales with I<sub>ON</sub>.

### 3.5 Circuit level benefits of BG-FETs

Adaptive supply- and threshold-voltage scaling can be used to minimize energy dissipation as delay requirements of a circuit change. Deeply scaled bulk-Si MOSFETs have limited  $V_{TH}$  tuning range due to reduced body effect and reduced  $V_{DD}/V_{TH}$  ratios [6, 7]. The  $V_{TH}$  of DG-FET devices cannot be dynamically changed. The  $V_{TH}$  tunability of deeply scaled BG devices makes them attractive for achieving minimal energy over a wide range of target frequencies.

Adaptive body biasing can be used to set the optimum  $V_{TH}$  for each die so as to compensate for variations in chip performance or power dissipation [6, 7]. The  $V_{TH}$  of the NMOS/PMOS devices in each die is therefore controlled not only by gate workfunction and channel length engineering but also by the application of the appropriate forward or

reverse back-gate bias. Dies that are too slow and fail to meet the performance target need to be forward biased, thereby increasing the die operating frequency and the overall die leakage, whereas those that leak excessively have to be reverse biased, reducing the operating frequency as well. The goal of the ABB is to find the optimum PMOS/NMOS  $V_{TH}$  combination that maximizes the die frequency while meeting the leakage constraint.

Dynamic voltage scaling (DVS) [16] can been used to reduce the dynamic power dissipation because of the quadratic dependence of switching power on  $V_{DD}$ . As  $V_{DD}$  is scaled, the device currents are degraded due to a reduced gate overdrive,  $V_{GS}$ - $V_{TH}$ , leading to slower switching speeds. This is the only power saving technique that can be applied to DG-FETs such as the FinFET, which have no external  $V_{TH}$  control capability. This interdependence between dynamic power and switching speeds can be broken by using a combination of DVS and ABB.  $V_{DD}$  can be scaled to save switching power and the  $V_{TH}$  can be lowered correspondingly to maintain enough gate overdrive to retain the switching speed. However, reducing the  $V_{TH}$  increase the leakage current of the transistors significantly. Therefore, there exists a clear tradeoff between the static power dissipation (from lowering  $V_{TH}$ ) and the active power (from lowering  $V_{DD}$ ) for a given application, leading to the existence of an optimal  $V_{DD}$  and  $V_{TH}$  combination that requires the lowest energy to perform a given task [4, 17].

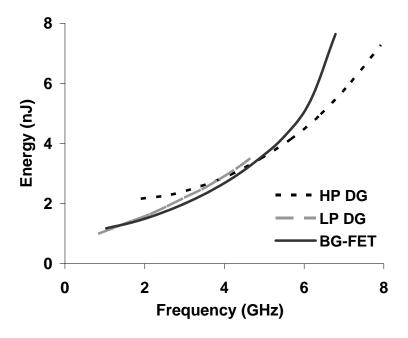

Figure 3.8 demonstrates an example system, where adaptive  $V_{DD}$  and  $V_{TH}$  control of BG-FETs achieves wider energy scalability spanning the range of both HP/LP DG-FETs. While the highest performance achievable by BG-FETs is lower than that of HP DG-FETs, the minimum energy approaches that of the LP DG-FETs when the

computational throughput is reduced significantly. Thus the BG-FET spans a wide range of E-D space and is the energy optimal device for intermediate frequencies. [12]

Figure 3.8 - Dynamic voltage scaling of DG-FETs and BG FETs at  $L_G=13 \text{nm}$ . With back-gate bias adjusted as voltage is scaled, the BG-FETs are able to achieve higher performance than the low-power DG-FET and lower energy than the HP DG-FET.

Active leakage control [18] implemented with BG devices allows a circuit to benefit from the low sleep-state leakage while still having performance that is determined by the active-state  $I_{ON}$ . The energy penalty for placing a BG device in the sleep state is the switched capacitance of the back gate, and it can be done in a single cycle. For a bulk-Si MOSFET, switching a large well capacitance incurs a significant energy and delay penalty. Since the benefits of the BG-FET device (Figure 3.2) going into a deeper sleep is retained with scaling into the sub-10nm regime, it is well suited for leakage control in future systems. In our simulations the maximum applied negative back bias was limited to  $-V_{DD}$ ; in practical systems it can be made more negative.

| Circuit Parameters | Value               |  |

|--------------------|---------------------|--|

| Logic depth        | 375 CV/I            |  |

| Gate area          | 2.4 mm <sup>2</sup> |  |

| Activity           | 10%                 |  |

| % Core sleep       | 30%                 |  |

Table 3-2: Example system @  $L_G = 13$ nm

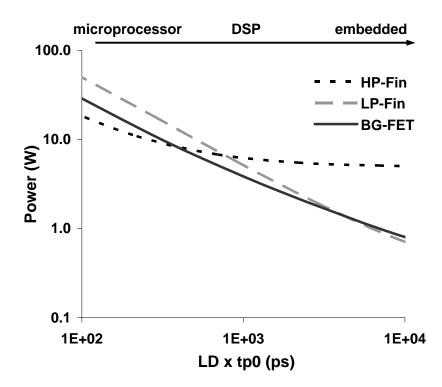

Figure 3.9: Minimum power envelope with changing logic depth in the example system (Table 3-2). The envelope represents the minimum power achievable through a combination of voltage scaling and back-gate biasing to adjust  $V_{TH}$ .

Figure 3.9 illustrates E-D trade-offs with varying logic depths in an example system implemented with both DG-FETs and BG-FETs. BG-FET implementations make use of adaptive threshold control and active leakage control in addition to  $V_{DD}$  adjustment to achieve a wider range of optimality. The minimum power envelope for the BG-FETs

lies in between that of the HP and LP FinFETs. Both Figure 3.8 and Figure 3.9 illustrate the capability of the BG-FETs to achieve delays similar to a HP DG-FET, and attain the low power of LP DG-FETs at low operating frequencies.

A multi- $V_{TH}$  DG-FET technology with more that three  $V_{TH}$  values can potentially outperform BG-FETs, but the benefit of BG-FET technology is in providing a single technology solution to meet different target applications with different throughput requirements.

#### 3.6 Conclusions

Power dissipation of scaled high performance ICs will be controlled by utilizing more than one type of transistor together with device, design and architectural techniques. This chapter presents the design of energy-delay optimized BG-FETs, and discusses the effectiveness of back-gate biasing to control the leakage current. It is demonstrated that BG-FETs exhibit power savings benefits over double-gate MOSFETs that increase with scaling into the sub-10 nm regime. Energy vs. delay (E-D) optimization shows that BG-FETs can span a wide range in E-D space, making it possible to have a single-device solution to meet high performance and low power needs through adaptive supply and threshold voltage biasing.

#### 3.7 References

- [1] J. M. Rabaey, A. Chandrakasan, and B. Nikolic', *Digital Integrated Circuits*, 2 ed: Prentice Hall, 2002.

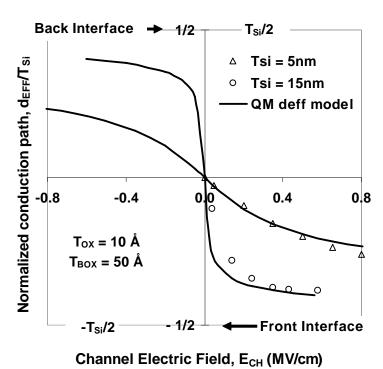

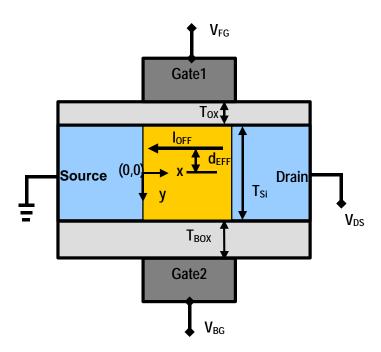

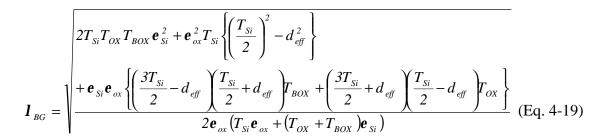

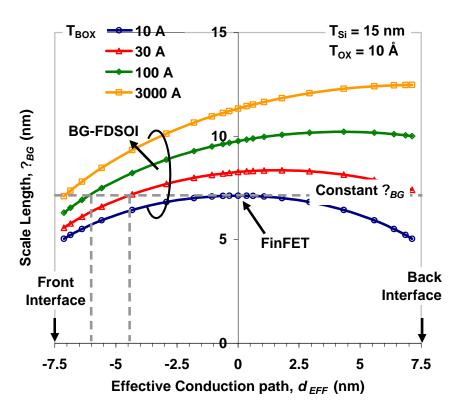

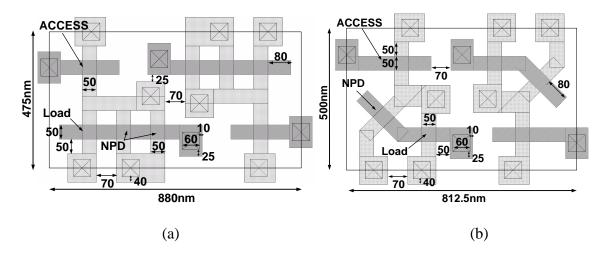

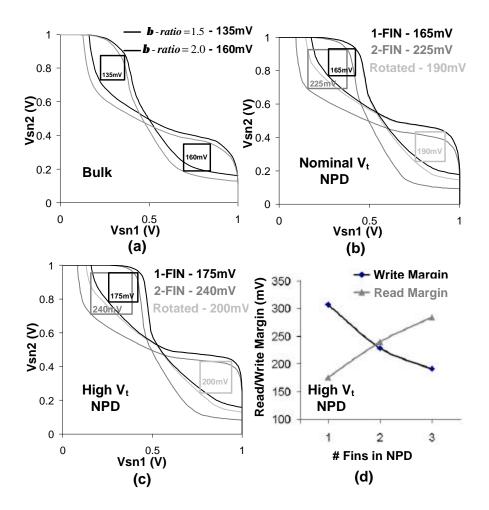

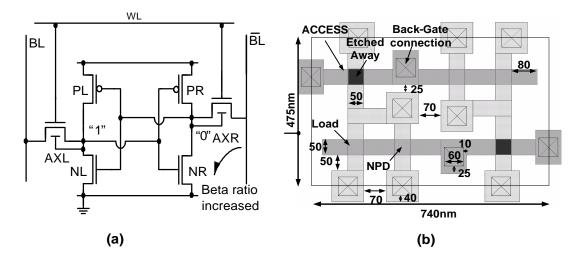

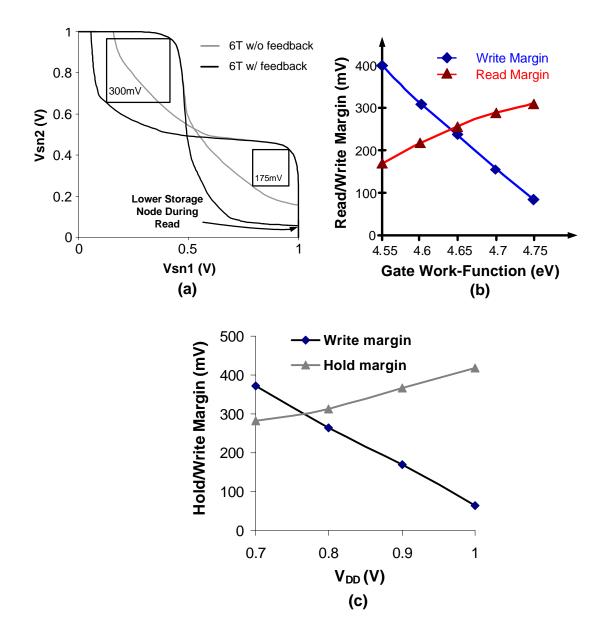

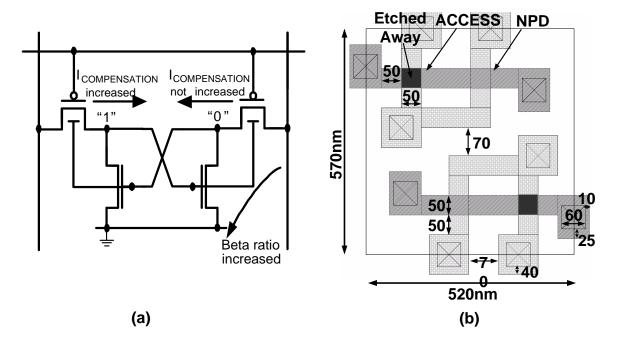

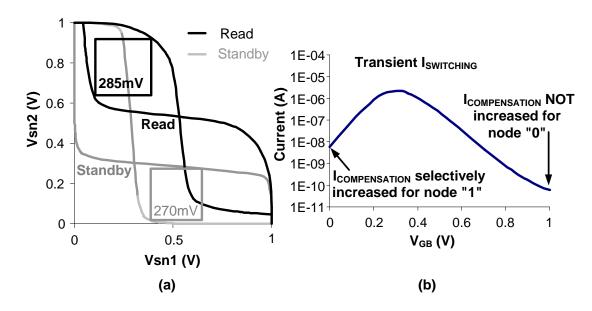

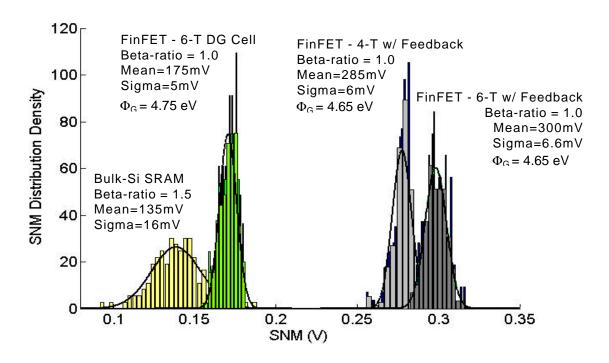

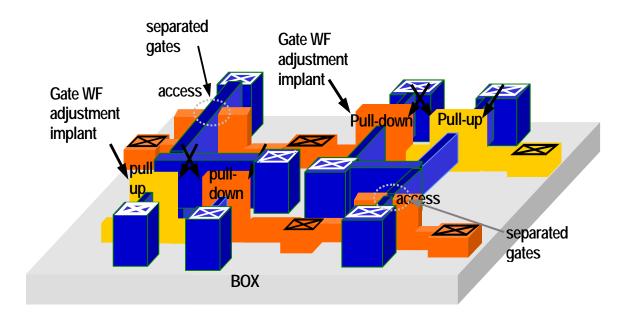

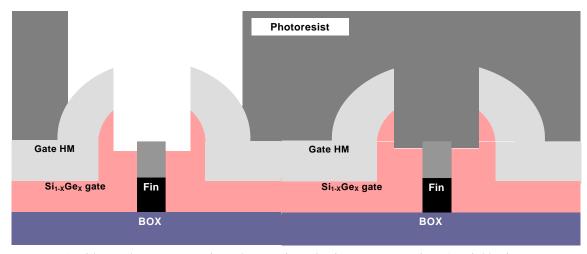

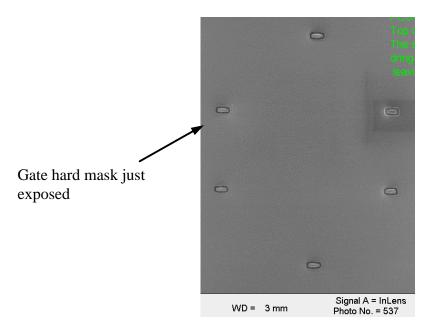

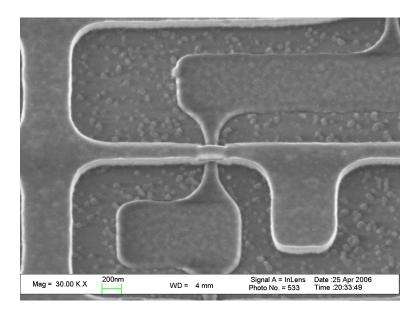

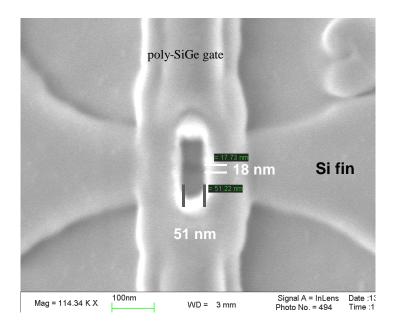

- [2] "International Technology Roadmap for Semiconductors, 2005 ed," http://www.itrs.net/Links/2005ITRS/Home2005.htm.