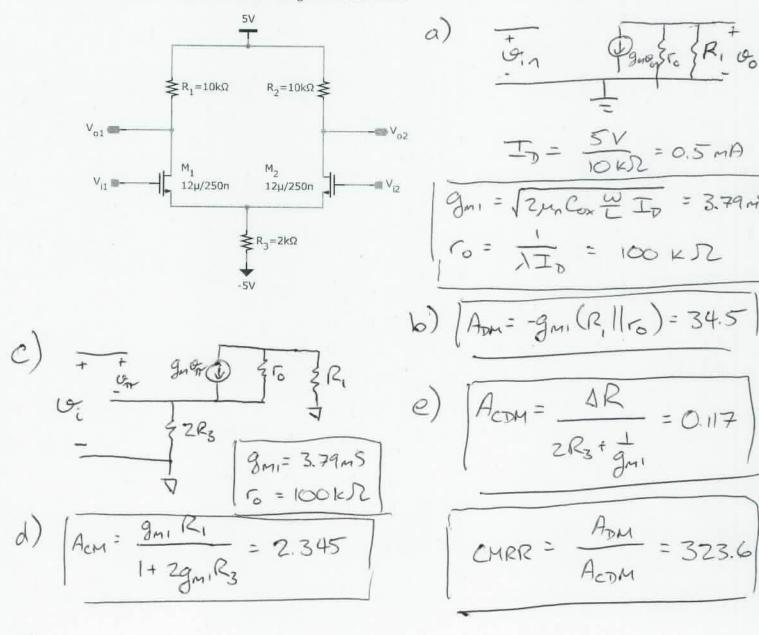

- 1. In the circuit below,  $V_{ic}$  is adjusted such that  $V_{oc} = 0 \text{ V}$ .

- a) Draw the low-frequency small-signal differential-mode half-circuit model. Calculate the values of all low-frequency small-signal parameters (r<sub>0</sub>'s, etc.).

- b) Calculate the value of the low-frequency small-signal differential-mode gain,  $A_{dm}$ , of the circuit.

- c) Draw the low-frequency small-signal common-mode half-circuit model. Specify the values of all low-frequency small-signal parameters.

- d) Calculate the value of the low-frequency small-signal common-mode gain, Acm, of the circuit.

- e) Because of manufacturing imperfections, the values of resistors  $R_1$  and  $R_2$  are slightly different:  $R_1 = R_o + \Delta R/2$  and  $R_1 = R_o + \Delta R/2$  with  $R_o = 10 \, \mathrm{k}\Omega$  and  $\Delta R = 0.05 R_o$ . Calculate the low-frequency small-signal common-mode to differential gain,  $A_{cdm}$ , and the common-mode rejection ratio, CMRR.

- f) Describe a circuit modification resulting in at least a two-orders-of-magnitude improvement of the CMRR. You do not need to design the modification.

f) Replace Rz with a current source, source resistancie at least 100x Rz.

2) First try: current mirror Rout = ro = 1 = 1.275 MB X 2=0.02v-1, ID=39MA doesn't neet spec = ) try cascode Second for: cascode Rout = gmro2 - (1) ym = 2ID 2ID = √2ID (6x L - (7)  $r_0 = \frac{1}{\lambda I_0} - (3)$ Combine equations (1), (2), (3): 2-0.024-1, ID=39uA, un = 300cm2/vs Rout = 587 MJZ weeks spec Cox = loff , L = Lmin = (80 nm , W= Jum We could lower four to 10Moz and size W accordingly to minimize the transistor sizes. Showing Cascode biasing is important in schematic

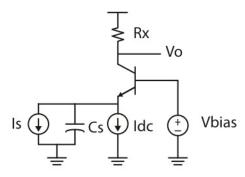

$$\omega_{3dB} = \frac{1}{C_s R_{in}}$$

$$R_{in} = \frac{1}{g_m}$$

$$2\pi * 500MHz = \frac{1}{10pF * R_{in}}$$

$$R_{in} = 31.8\Omega$$

$$R_{in} = \frac{1}{g_m} \Rightarrow g_m = 31.4mS$$

$$g_m = \frac{I_C}{V_T} \Rightarrow I_C = I_{dc} = 785\mu A$$

$$V_{0,Low\,Frequency} = i_{s} * R_{X} \Rightarrow R_{X} = 1k\Omega$$

Q4)

We know from previous that the resistance looking down from the output node is:

$$R_{0,Down} \approx g_m r_o^2$$

This resistance is probably much larger than 2k so we can assume the low frequency gain is:

$$a_v = -g_m R_L \Rightarrow g_m = \frac{10}{2k} = 5mS$$

The dominant pole is in input since the resistance is larger than output  $(R_L)$  and the cascade node  $(1/g_m)$ . Also the capacitor is larger since there is miller effect and the gate-source capacitor.

$$\omega_{3dB} = \frac{1}{R_s(C_{gs,1} + 2C_{ov,1})}$$

$$2\pi * 800MHz = \frac{1}{R_s(\frac{2}{3}WLC_{ox} + WC_{oV} + 2WC_{oV})}$$

$$2\pi * 800MHz = \frac{1}{10K(\frac{2}{3}W0.18 * 10e - 15 + 3W * 0.2e - 15)}$$

$$W \approx 11.05\mu m$$

$$I_D = 678\mu A$$

$$V_{dsat} = \frac{g_m}{\frac{W}{L}\mu_nC_{ox}} = 270mV$$

$$V_{GS} = V_{dsat} + V_{Th} = 670mV$$

$$V_{Bias,min} = V_{dsat} + V_{GS} = 940mV$$

$$r_0 = \frac{1}{\lambda I_D} = \frac{1}{0.02 * 678e - 6} = 73.7k\Omega \Rightarrow g_m r_o^2 = 27.2M\Omega!$$

In the circuit below, M<sub>1</sub> and M<sub>2</sub> are used as switches to control current flow between nodes V<sub>1</sub> and  $V_2$ . The control voltages  $V_{c1}$  and  $V_{c2}$  are set to 0 V and 3 V to turn the switch on, and 3 V and 0 V to turn the switch off.

Determine the minimum width of  $M_1$  and  $M_2$  required such that the maximum resistance  $R_{on}$  between nodes  $V_1$  and  $V_2$  is  $10 \Omega$  when the switch is on and  $V_1$  varies between 0 V and 3 V for  $V_2 \approx V_1$ . Choose  $L_1 = L_2 = 180$  nm. For which value of  $V_1$  does  $R_{on}$  reach its maximum?

Relevance: thousands of switches like this one tick along in the analog-to-digital and digital-to-analog converters used in audio and video cards, cameras, or radios.

$$\begin{pmatrix}

6

\end{pmatrix}

\begin{pmatrix}

a

\end{pmatrix}

\underbrace{I_{D1}}_{I_{D2}} = \frac{1}{2} \underbrace{M_P \left(6x \left(\frac{\omega}{L}\right)_1 \left(V_{DD} - V_6 - V_{TH}\right)^2}_{\frac{1}{2} M_P \left(6x \left(\frac{\omega}{L}\right)_2 \left(V_{DD} - V_6 - V_{TH}\right)^2} = \frac{\omega_1}{\omega_2} = \frac{1}{10}$$

(b)

$$Id_1 = I_{C_1} = I_{S_2} e^{VBE_1/V_7}$$

$$Id_2 = I_{C_2} = I_{S_2} e^{VBE_2/V_7} \begin{cases} I_{D_1} = \frac{1}{10} = \frac{(VBE_1 - VBE_2)/V_7}{I_{D_2}} = \frac{1}{10} = \frac{(VBE_1 - VBE_2)/V_7}{I_{D_2}} \end{cases}$$

Combine (1) & (2):

$$|I_{D_1} = \frac{kT}{gR_1} ln(10)$$